半导体器件的制作方法

实施方式涉及半导体器件。

背景技术:

1、根据电子工业的发展和用户的需求,电子装置正在进一步小型化且具有高性能。因此,在电子装置中使用的半导体器件也需要高度集成和具有高性能。为了制造高性能的半导体器件,需要能够最小化在相邻的导电结构之间的寄生电容的技术,以最小化由于rc延迟引起的信号传输速度的劣化。

技术实现思路

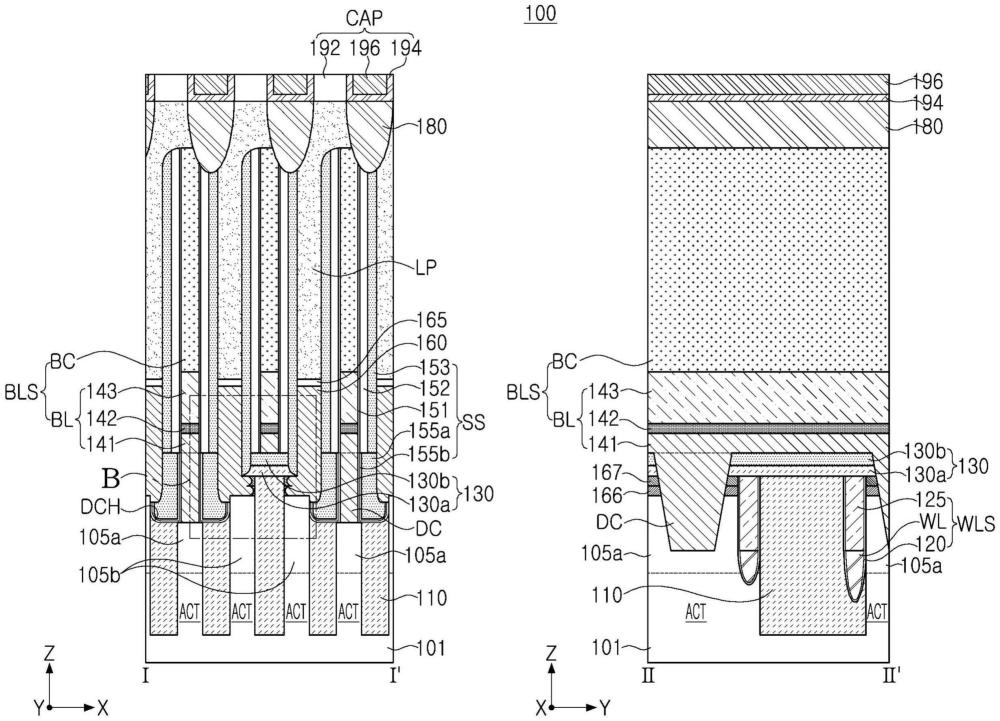

1、根据实施方式的一方面,一种半导体器件包括:基板,包括有源区;位线结构,在基板上并在一个方向上延伸;位线接触,电连接有源区的第一杂质区和位线结构;以及存储节点接触,在位线结构的侧壁上并电连接到有源区的第二杂质区,其中存储节点接触包括在垂直于基板的上表面的垂直方向上延伸的垂直延伸部分以及一体地连接到垂直延伸部分并在平行于基板的上表面的水平方向上延伸的水平延伸部分。

2、根据实施方式的一方面,一种半导体器件包括:基板,包括有源区,有源区具有第一杂质区和第二杂质区;牺牲图案层,在有源区上;器件隔离层,限定有源区并具有与牺牲图案层的上表面共面的上表面;字线结构,在第一水平方向上延伸并具有与牺牲图案层的上表面共面的上表面;位线结构,在基板上并在与第一水平方向相交的第二水平方向上延伸;位线接触,电连接第一杂质区和位线结构;以及存储节点接触,在位线接触的侧表面上并电连接到第二杂质区,其中存储节点接触包括接触第二杂质区的上表面并在平行于基板的上表面的水平方向上延伸的水平延伸部分。

3、根据实施方式的一方面,一种半导体器件包括:基板,包括有源区,有源区具有第一杂质区和第二杂质区;牺牲图案层,在有源区上;器件隔离层,限定有源区并具有与牺牲图案层的上表面共面的上表面;字线结构,在第一水平方向上延伸并具有与牺牲图案层的上表面共面的上表面;位线结构,在基板上并在与第一水平方向相交的第二水平方向上延伸;以及位线接触,电连接第一杂质区和位线结构,其中牺牲图案层包括在第一杂质区上的与位线接触的侧表面接触的部分,并且牺牲图案层包括金属、金属氧化物、金属氮化物和硅锗中的至少一种。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中所述水平延伸部分在比所述位线结构的下表面低的水平处。

3.根据权利要求1所述的半导体器件,其中所述水平延伸部分与所述有源区的上表面的至少一部分接触。

4.根据权利要求1所述的半导体器件,其中整个所述水平延伸部分在所述垂直方向上与所述有源区的所述第二杂质区重叠。

5.根据权利要求1所述的半导体器件,还包括限定所述有源区的器件隔离层,所述器件隔离层的上表面在比所述有源区的上表面高的水平处。

6.根据权利要求5所述的半导体器件,其中:

7.根据权利要求5所述的半导体器件,还包括在所述有源区上的牺牲图案层,所述牺牲图案层的上表面与所述器件隔离层的所述上表面共面,并且所述牺牲图案层与所述水平延伸部分接触。

8.根据权利要求7所述的半导体器件,其中所述牺牲图案层包括金属、金属氧化物、金属氮化物和与所述基板的材料不同的半导体材料中的至少一种。

9.根据权利要求5所述的半导体器件,其中所述水平延伸部分与在所述垂直方向上从所述有源区突出的所述器件隔离层的侧表面的至少一部分接触。

10.根据权利要求1所述的半导体器件,其中所述垂直延伸部分包括突出超过所述水平延伸部分的下表面的突起。

11.根据权利要求10所述的半导体器件,还包括围绕所述位线接触的侧壁的间隔物结构,所述间隔物结构与所述突起接触。

12.根据权利要求1所述的半导体器件,还包括在所述位线结构和所述存储节点接触之间的间隔物结构,所述水平延伸部分的至少一部分在所述垂直方向上与所述间隔物结构重叠。

13.根据权利要求12所述的半导体器件,其中所述间隔物结构包括依次堆叠在所述位线结构的所述侧壁上的第一间隔物、第二间隔物和第三间隔物,所述水平延伸部分包括在所述垂直方向上与所述第二间隔物重叠的部分。

14.一种半导体器件,包括:

15.根据权利要求14所述的半导体器件,其中所述水平延伸部分在与所述牺牲图案层相同的水平处。

16.根据权利要求14所述的半导体器件,其中所述牺牲图案层包括在所述第一杂质区上的部分,所述部分接触所述位线接触的所述侧表面。

17.根据权利要求14所述的半导体器件,其中所述牺牲图案层包括在所述有源区上的第一层和第二层,所述第一层包括硅氧化物,所述第二层包括金属、金属氧化物、金属氮化物和硅锗中的至少一种。

18.一种半导体器件,包括:

19.根据权利要求18所述的半导体器件,其中:

20.根据权利要求19所述的半导体器件,还包括存储节点接触,所述存储节点接触具有:

技术总结

一种半导体器件包括:基板,具有有源区;位线结构,在基板上并在一个方向上延伸;位线接触,电连接有源区的第一杂质区和位线结构;以及存储节点接触,设置在位线结构的侧壁上并电连接到有源区的第二杂质区,其中存储节点接触包括在垂直于基板的上表面的垂直方向上延伸的垂直延伸部分以及一体地连接到垂直延伸部分并在平行于基板的上表面的水平方向上延伸的水平延伸部分。

技术研发人员:安浚爀,朴素贤

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!