一种Sinc滤波器与电子设备的制作方法

本申请涉及数模转换及其数字滤波,具体而言,涉及一种sinc滤波器与电子设备。

背景技术:

1、在数模混合芯片中,同一芯片内数字电路往往会对模拟电路产生很强的干扰,这种干扰会带来模拟电路性能的损失。普通的奈奎斯特采样率的模数转换器(adc)在这种环境下就很难达到较高的精度。

2、为此,近年来高精度adc的研究和开发成为了adc热点,而采用过采样和sigma-delta结构的adc以其在高精度方面显著的优势成为了该领域的代表。这种结构降低了对模拟电路的要求,然而大大增加了数字电路的复杂度。其中的数字抽取滤波器作为一个必要的模块,具有大量的算术电路,尤其当位宽和阶数都很高时,其物理实现将严重耗费硬件资源,通常将占据整个adc芯片的大部分面积。

3、综上,现有技术中滤波器存在耗费资源严重,占用面积大的问题。

技术实现思路

1、本申请的目的在于提供一种sinc滤波器与电子设备,以解决现有技术中存在的滤波器存在耗费资源严重,占用面积大的问题。

2、为了实现上述目的,本申请实施例采用的技术方案如下:

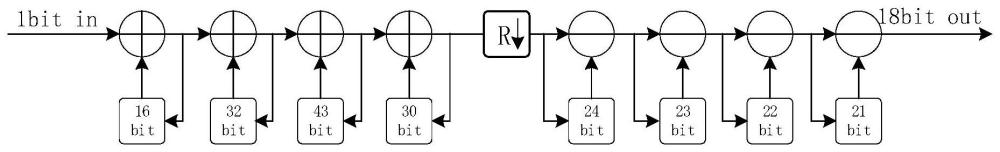

3、一方面,本申请实施例提供一种sinc滤波器,应用于周期复位系统,所述sinc滤波器包括积分器、抽取器以及梳状器,所述积分器、所述抽取器以及所述梳状器依次连接;

4、所述积分器包括多个级联的积分单元,每个积分单元均包括相互连接的加法器与第一寄存器,所述第一寄存器位于延时支路上;其中,

5、前n级积分单元中,第一寄存器的数据位宽小于hogenaure结构的标准值,且所述标准值依据所述sinc滤波器输出信号的位宽确定,n≥1。

6、可选地,前n级积分单元中,第一寄存器的数据位宽满足公式:

7、yn=q*log2(r*n)

8、其中,yn表示第n级积分单元中第一寄存器的数据位宽,q表示积分单元的级数,r表示降采样率,n表示sinc滤波器的级数。

9、可选地,hogenaure结构的标准值满足公式:

10、

11、

12、wj=bmax-bj

13、其中,bmax表示中间量,n表示sinc滤波器的级数,r表示降采样率,bin表示输入量,bj表示第j级低位截断的位宽个数,fj表示前j级的误差方差之和,σt2n+1表示最后一级误差源的方差,wj表示hogenaure结构中,第j级积分单元的第一寄存器的数据位宽标准值,符号表示向上取整,符号表示向下取整。

14、可选地,当所述积分器包括四个积分单元时,第一个积分单元中第一寄存器的数据位宽为16bit,第二个积分单元中第一寄存器的数据位宽为32bit。

15、可选地,多个所述积分单元通过流水方式连接。

16、可选地,在所述积分器中,前一级积分单元的第一寄存器与后一级积分单元的加法器相连,第一级积分单元的加法器用于接收输入信号,最后一级积分单元的第一寄存器与所述抽取器相连。

17、可选地,所述梳状器包括多个差分单元,所述差分单元的数量与所述积分单元的数量相等,每个所述差分单元均包括相互连接的减法器与第二寄存器,所述第二寄存器位于延时支路上,所述多个差分单元的第二寄存器的数据位宽逐渐降低。

18、可选地,所述梳状器包括第三寄存器、全加模块以及第四寄存器,所述抽取器、所述第三寄存器、所述全加模块以及所述第四寄存器依次连接,所述第三寄存器、所述全加模块以及所述第四寄存器还分别接收不同的控制信号,并在所述控制信号的控制下执行相加或相减逻辑。

19、可选地,所述全加模块包括反相器、选择器以及全加器,所述第三寄存器的第一抽头连接选择器的第一端口,所述第三寄存器的第二抽头通过反相器连接选择器的第二端口,所述选择器、所述全加器以及所述第四寄存器依次连接。

20、另一方面,本申请实施例还提供了一种电子设备,所述电子设备包括上述的sinc滤波器。

21、相对于现有技术,本申请具有以下有益效果:

22、本申请提供了一种sinc滤波器与电子设备,该sinc滤波器应用于周期复位系统,sinc滤波器包括积分器、抽取器以及梳状器,积分器、抽取器以及梳状器依次连接;积分器包括多个级联的积分单元,每个积分单元均包括相互连接的加法器与第一寄存器,第一寄存器位于延时支路上;其中,前n级积分单元中,第一寄存器的数据位宽小于hogenaure结构的标准值,且标准值依据sinc滤波器输出信号的位宽确定,n≥1。由于本申请提供的sinc滤波器中,在周期复位的应用场景下,对n级积分单元的寄存器位宽进行了优化,移除了高位未使用的寄存器,因此减小了整个sinc滤波器的耗费资源与面积。

23、为使本申请的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:

1.一种sinc滤波器,其特征在于,应用于周期复位系统,所述sinc滤波器包括积分器、抽取器以及梳状器,所述积分器、所述抽取器以及所述梳状器依次连接;

2.如权利要求1所述的sinc滤波器,其特征在于,前n级积分单元中,第一寄存器的数据位宽满足公式:

3.如权利要求1所述的sinc滤波器,其特征在于,hogenaure结构的标准值满足公式:

4.如权利要求1所述的sinc滤波器,其特征在于,当所述积分器包括四个积分单元时,第一个积分单元中第一寄存器的数据位宽为16bit,第二个积分单元中第一寄存器的数据位宽为32bit。

5.如权利要求1所述的sinc滤波器,其特征在于,多个所述积分单元通过流水方式连接。

6.如权利要求5所述的sinc滤波器,其特征在于,在所述积分器中,前一级积分单元的第一寄存器与后一级积分单元的加法器相连,第一级积分单元的加法器用于接收输入信号,最后一级积分单元的第一寄存器与所述抽取器相连。

7.如权利要求1所述的sinc滤波器,其特征在于,所述梳状器包括多个差分单元,所述差分单元的数量与所述积分单元的数量相等,每个所述差分单元均包括相互连接的减法器与第二寄存器,所述第二寄存器位于延时支路上,所述多个差分单元的第二寄存器的数据位宽逐渐降低。

8.如权利要求1所述的sinc滤波器,其特征在于,所述梳状器包括第三寄存器、全加模块以及第四寄存器,所述抽取器、所述第三寄存器、所述全加模块以及所述第四寄存器依次连接,所述第三寄存器、所述全加模块以及所述第四寄存器还分别接收不同的控制信号,并在所述控制信号的控制下执行相加或相减逻辑。

9.如权利要求8所述的sinc滤波器,其特征在于,所述全加模块包括反相器、选择器以及全加器,所述第三寄存器的第一抽头连接选择器的第一端口,所述第三寄存器的第二抽头通过反相器连接选择器的第二端口,所述选择器、所述全加器以及所述第四寄存器依次连接。

10.一种电子设备,其特征在于,所述电子设备包括如权利要求1至9任一项所述的sinc滤波器。

技术总结

本申请提供了一种Sinc滤波器与电子设备,涉及数模转换及其数字滤波技术领域。该Sinc滤波器应用于周期复位系统,Sinc滤波器包括积分器、抽取器以及梳状器,积分器、抽取器以及梳状器依次连接;积分器包括多个级联的积分单元,每个积分单元均包括相互连接的加法器与第一寄存器,第一寄存器位于延时支路上;其中,前n级积分单元中,第一寄存器的数据位宽小于Hogenaure结构的标准值,且标准值依据Sinc滤波器输出信号的位宽确定,n≥1。本申请提供的Sinc滤波器与电子设备具有减小了耗费资源与面积的优点。

技术研发人员:陈看,付小川,徐珑,张强

受保护的技术使用者:成都时域半导体有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!