基于低压差线性稳压器电路的锁相环电路以及芯片的制作方法

本发明涉及反馈控制电路,尤其涉及一种基于低压差线性稳压器电路的锁相环电路以及芯片。

背景技术:

1、锁相环(phase locked loop,pll)电路是一种利用相位同步产生的电压,去调谐压控振荡器以产生目标频率的负反馈控制电路。pll电路被广泛地应用于集成电路中用于时钟信号的处理。在很多的场合,pll的输出时钟信号需要有精准的频率。

2、一般地,pll电路包括:鉴频鉴相器(phase frequency detector,pfd)、电荷泵(charge pump,cp)、环路滤波器(loop pass filter,lpf)以及压控振荡器(voltage-controlled oscillator,vco)。

3、目前,为了简化pll电路的结构,通常采用低压差线性稳压器电路为pll电路提供供电电压和驱动电流。

4、在采用低压差线性稳压器电路的基础上,有源的lpf相比于无源的lpf,需要一个额外的基准电压,但是,如果该基准电压的噪声较高,那么将导致该基准电压的噪声被引入到pll电路中,从而导致pll电路产生相位噪声。

技术实现思路

1、本申请实施例提供的基于低压差线性稳压器电路的锁相环电路以及芯片,能够克服现有技术的至少一部分缺陷。

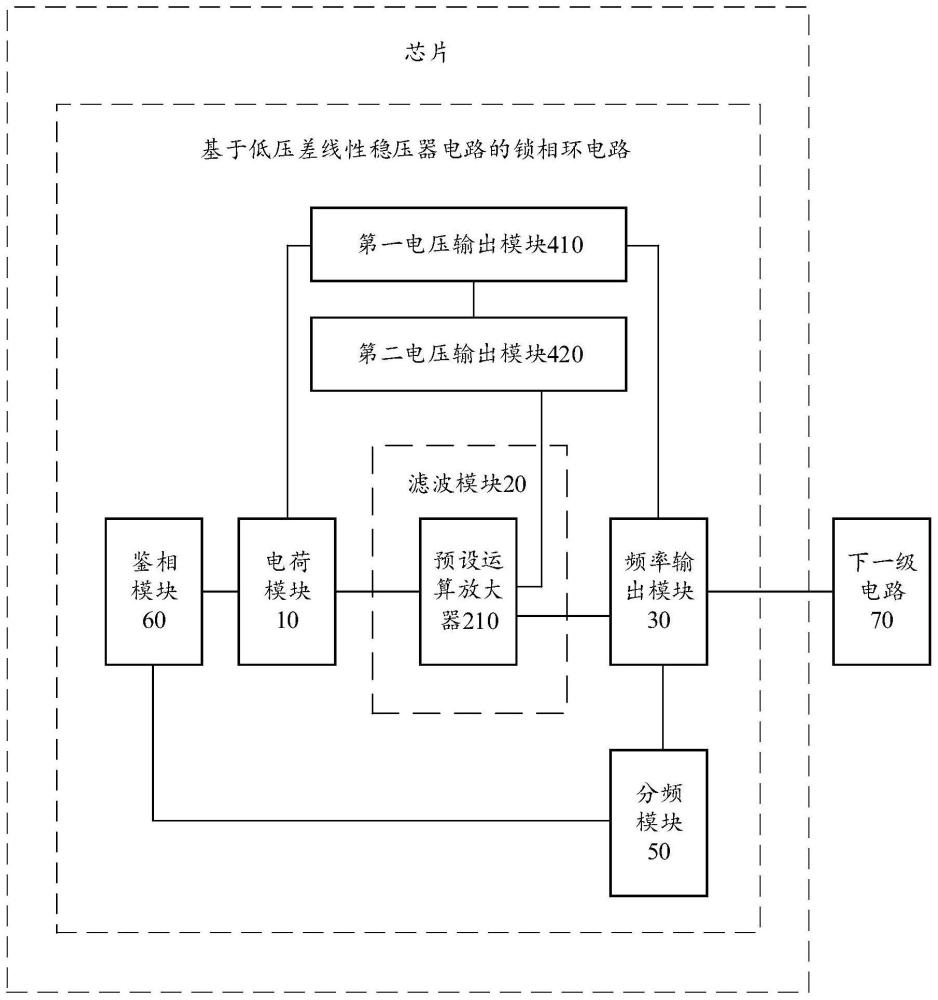

2、第一方面,本申请实施例提供了一种基于低压差线性稳压器电路的锁相环电路。该锁相环电路包括:频率输出模块、电荷模块、具有预设运算放大器的滤波模块以及低压差线性稳压器电路;所述低压差线性稳压器电路包括:互相连接的第一电压输出模块和第二电压输出模块;所述第一电压输出模块分别与所述频率输出模块以及所述电荷模块连接,所述第一电压输出模块,被配置为:向所述频率输出模块以及所述电荷模块提供驱动电压;所述第二电压输出模块与所述滤波模块中的预设运算放大器连接,所述第二电压输出模块,被配置为:向所述预设运算放大器提供基准电压。

3、可选地,所述第一电压输出模块包括:恒压电源、第一p型mos管、第二p型mos管、第一n型mos管、第二n型mos管和第三n型mos管;所述第一p型mos管的源极、所述第二p型mos管的源极以及所述第一n型mos管的漏极均与所述恒压电源连接;所述第一p型mos管的栅极与所述第二p型mos管的栅极连接,所述第一p型mos管的漏极分别与所述第一p型mos管的栅极以及所述第二n型mos管的漏极连接;所述第二p型mos管的漏极分别与所述第一n型mos管的栅极以及所述第三n型mos管的漏极连接;所述第一n型mos管的源极分别与所述第二n型mos管的栅极以及所述第三n型mos管的栅极连接并形成第一电压输出端,所述第一电压输出端用于输出所述驱动电压;所述第二n型mos管的源极与所述第三n型mos管的源极分别与所述第二电压输出模块连接。

4、可选地,所述第二电压输出模块包括:第一电阻、第四n型mos管和第五n型mos管;所述第四n型mos管的漏极和栅极均与所述第二n型mos管的源极连接,所述第四n型mos管的源极与所述第一电阻的第一端连接,所述第一电阻的第二端连接到地;所述第五n型mos管的漏极和栅极均与所述第三n型mos管的源极连接,并且所述第五n型mos管的栅极形成第二电压输出端,所述第二电压输出端用于输出所述基准电压;所述第五n型mos管的源极连接到地。

5、可选地,所述第四n型mos管具有:第一晶体管宽度和第一通道长度;所述第五n型mos管具有:第二晶体管宽度和第二通道长度;所述第一晶体管宽度与所述第一通道长度之间的比值为第一比值;所述第二晶体管宽度与所述第二通道长度之间的比值为第二比值;所述第一比值为所述第二比值的正整数倍。

6、可选地,所述预设运算放大器具有:反相输入端、同相输入端、信号输出端、电源输入端和接地端;所述同相输入端与所述第二电压输出端连接,所述同相输入端用于接收所述基准电压;所述电源输入端与所述恒压电源连接,所述电源输入端用于接收所述恒压电源提供的电能;所述反相输入端与所述电荷模块连接,所述反相输入端用于接收所述电荷模块所输出的电流;所述信号输出端与所述频率输出模块连接,所述信号输出端用于将所述预设运算放大器输出的电压信号输出至所述频率输出模块;所述接地端连接到地。

7、可选地,所述滤波模块还包括:第二电阻、第三电阻、第一电容、第二电容和第三电容;所述第二电阻的第一端与所述电荷模块连接,所述第二电阻的第二端与所述反相输入端连接;所述第一电容的第一端与所述第二电阻的第一端连接,所述第一电容的第二端连接到地;所述第三电阻的第一端与所述反相输入端连接,所述第三电阻的第二端与所述第二电容的第一端连接,所述第二电容的第二端与所述信号输出端连接;所述第三电容的第一端分别与所述第三电阻的第一端以及所述反相输入端连接,所述第三电容的第二端分别与所述第二电容的第二端以及所述信号输出端连接。

8、可选地,所述频率输出模块包括:压控振荡器、第四电阻和第五电阻;所述第四电阻的第一端与所述第一电压输出端连接,所述第四电阻的第二端分别与所述压控振荡器以及所述第五电阻的第一端连接;所述第五电阻的第二端与所述滤波模块连接。

9、可选地,在所述滤波模块没有对所述频率输出模块输出电压信号时,所述频率输出模块所输出的基础频率信号是根据所述第四电阻和所述第五电阻对通过所述压控振荡器的电压进行分压而确定的。

10、可选地,所述第五电阻为可调节电阻值的电阻,在所述滤波模块对所述频率输出模块输出电压信号时,通过所述第五电阻对所述滤波模块输出的电压信号进行动态分压,并对通过所述压控振荡器的电压进行动态调节,以使得对所述频率输出模块所输出的频率信号进行动态调节。

11、第二方面,本申请实施例提供了一种芯片,该芯片包括如上所述的锁相环电路。

12、本申请实施例提供的基于低压差线性稳压器电路的锁相环电路的至少一个有利方面是:通过第一电压输出模块输出驱动电压,并通过第二电压输出模块输出基准电压,从而为锁相环电路提供噪声较低的驱动电压和基准电压,进而避免引入额外的基准电压而造成锁相环电路产生相位噪声。

技术特征:

1.一种基于低压差线性稳压器电路的锁相环电路,其特征在于,所述锁相环电路包括:频率输出模块、电荷模块、具有预设运算放大器的滤波模块以及低压差线性稳压器电路;

2.根据权利要求1所述的锁相环电路,其特征在于,所述第一电压输出模块包括:恒压电源、第一p型mos管、第二p型mos管、第一n型mos管、第二n型mos管和第三n型mos管;

3.根据权利要求2所述的锁相环电路,其特征在于,所述第二电压输出模块包括:第一电阻、第四n型mos管和第五n型mos管;

4.根据权利要求2所述的锁相环电路,其特征在于,所述第四n型mos管具有:第一晶体管宽度和第一通道长度;

5.根据权利要求3所述的锁相环电路,其特征在于,所述预设运算放大器具有:反相输入端、同相输入端、信号输出端、电源输入端和接地端;

6.根据权利要求5所述的锁相环电路,其特征在于,所述滤波模块还包括:第二电阻、第三电阻、第一电容、第二电容和第三电容;

7.根据权利要求2所述的锁相环电路,其特征在于,所述频率输出模块包括:压控振荡器、第四电阻和第五电阻;

8.根据权利要求7所述的锁相环电路,其特征在于,在所述滤波模块没有对所述频率输出模块输出电压信号时,所述频率输出模块所输出的基础频率信号是根据所述第四电阻和所述第五电阻对通过所述压控振荡器的电压进行分压而确定的。

9.根据权利要求7所述的锁相环电路,其特征在于,所述第五电阻为可调节电阻值的电阻,在所述滤波模块对所述频率输出模块输出电压信号时,通过所述第五电阻对所述滤波模块输出的电压信号进行动态分压,并对通过所述压控振荡器的电压进行动态调节,以使得对所述频率输出模块所输出的频率信号进行动态调节。

10.一种芯片,其特征在于,所述芯片包括如权利要求1至9中任一项所述的锁相环电路。

技术总结

本申请实施例涉及一种基于低压差线性稳压器电路的锁相环电路。该锁相环电路包括:频率输出模块、电荷模块、具有预设运算放大器的滤波模块以及低压差线性稳压器电路;低压差线性稳压器电路包括:互相连接的第一电压输出模块和第二电压输出模块;第一电压输出模块,被配置为:向频率输出模块以及电荷模块提供驱动电压;第二电压输出模块,被配置为:向预设运算放大器提供基准电压。该锁相环电路通过第一电压输出模块输出驱动电压,并通过第二电压输出模块输出基准电压,从而为锁相环电路提供噪声较低的驱动电压和基准电压,进而避免引入额外的基准电压而造成锁相环电路产生相位噪声。

技术研发人员:殷强,芦文

受保护的技术使用者:深圳市中科蓝讯科技股份有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!