多次可编程存储单元结构及其制造方法与流程

本发明涉及半导体,特别是涉及一种多次可编程存储单元结构及其制造方法。

背景技术:

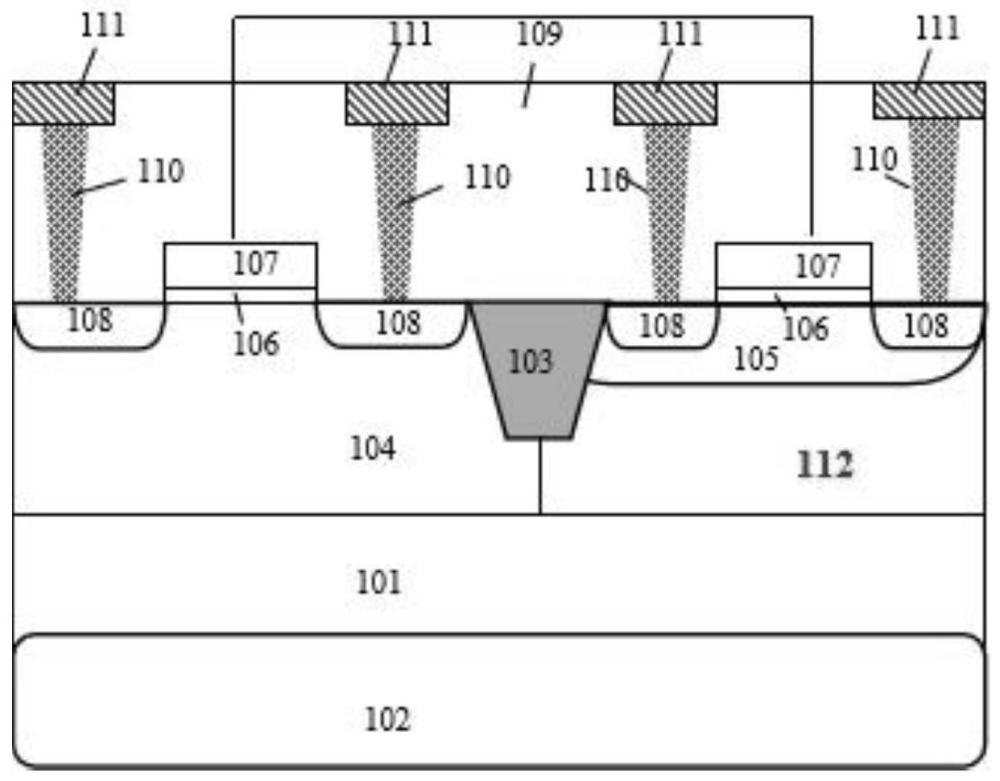

1、随着半导体技术的发展,存储器具有速度快、可靠性高、体积小、功耗低等优点,被广泛应用。其中多次可编程mtp(multi-time programmable)存储器成本低,可以根据客户需要进行多次重新编程和更新。常见的mtp器件结构如图11所示,其中各标号的结构为:

2、101:p型外延层,102:深n型离子注入(dnw),103:浅沟槽隔离(sti),104:p型阱区(pw),105:控制栅cg,106:栅氧化层,107:浮栅fg,108:n型重掺杂区,109:层间介质层(ild),110:接触孔(contact),111:金属电极

3、请参阅图12,为了使cg to pw(控制栅至p型阱区)以及wl to wl(字线至字线)的隔离耐压同时满足要求,cg采用两道n型杂质离子注入,其中低能量注入在p型阱表面形成n型区,高能量注入中和p型阱掺杂浓度,提高cg与pw结的耐压。但高能量cg注入会在sti底部形成n型掺杂,wl to wl容易发生punch(穿通),同时sti深度等工艺波动,也会导致wl towl隔离耐压变化较大,工艺窗口较小。

4、为解决上述问题,需要提出一种新型的多次可编程存储单元结构及其制造方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种多次可编程存储单元结构及其制造方法,用于解决现有技术中为了使cg to pw(控制栅至p型阱区)以及wl towl(字线至字线)的隔离耐压同时满足要求,cg采用两道n型杂质离子注入,其中低能量注入在p型阱表面形成n型区,高能量注入中和p型阱掺杂浓度,提高cg与pw结的耐压。但高能量cg注入会在sti底部形成n型掺杂,wl to wl容易发生punch(穿通),同时sti深度等工艺波动,也会导致wl to wl隔离耐压变化较大,工艺窗口较小的问题。

2、为实现上述目的及其他相关目的,本发明提供一种多次可编程存储单元结构,包括:

3、p型的衬底,在所述衬底上形成有p型的外延层,在所述外延层上形成有深n型掺杂区;

4、形成于所述外延层上的浅沟槽隔离,所述浅沟槽隔离用于定义出有源区;

5、分别形成于所述有源区上的p型阱区以及p型掺杂区,所述p型掺杂区的掺杂浓度低于所述p型阱区,所述p型掺杂区为形成控制栅的区域;

6、形成于所述p型掺杂区表面的n型掺杂区,n型掺杂区作为控制栅,其中靠近所述n型掺杂区处所述浅沟槽隔离底部的n型杂质离子浓度低于预设值;

7、形成于p型阱区和所述p型掺杂区上的栅介质层以及位于所述栅介质层上的多晶硅浮栅;

8、形成于所述多晶硅浮栅侧壁上的侧墙,在所述p型阱区和所述p型掺杂区上形成有位于多晶硅浮栅两侧的n型重掺杂区;

9、用于引出所述n型重掺杂区、所述多晶硅浮栅的金属互连结构。

10、优选地,所述衬底为硅衬底。

11、优选地,所述浅沟槽隔离的深度为2500至3000埃。

12、优选地,通过控制栅光罩注入p型杂质离子和n型杂离子,分别形成p型掺杂区和所述n型掺杂,不额外增加光罩层数。

13、优选地,所述侧墙由位于所述控制栅上的氧化层侧墙以及位于所述氧化层侧墙上的氮化层侧墙组成。

14、优选地,所述金属互连结构的形成方法包括:形成覆盖所述多晶硅浮栅的层间介质层;在所述层间介质层上形成于所述n型重掺杂区、所述多晶硅浮栅连通的接触孔;形成填充所述接触孔的金属层。

15、本发明还提供一种多次可编程存储单元结构的制造方法,包括:

16、步骤一、提供p型的衬底,在所述衬底上形成p型的外延层,在所述外延层上形成深n型掺杂区;

17、步骤二、在所述外延层上形成浅沟槽隔离以定义出有源区;

18、步骤三、分别在所述有源区上形成p型阱区以及p型掺杂区,所述p型掺杂区的掺杂浓度低于所述p型阱区,所述p型掺杂区为形成控制栅的区域,之后在所述p型掺杂区表面形成n型掺杂区作为控制栅,使得靠近所述n型掺杂区处所述浅沟槽隔离底部的n型杂质离子浓度低于预设值;

19、步骤四、形成位于p型阱区和所述p型掺杂区上的栅介质层以及位于所述栅介质层上的多晶硅浮栅,形成位于所述多晶硅浮栅侧壁上的侧墙,之后在所述p型阱区和所述p型掺杂区上形成位于多晶硅浮栅两侧的n型重掺杂区;

20、步骤五、形成用于引出所述n型重掺杂区、所述多晶硅浮栅、所述控制栅的金属互连结构。

21、优选地,步骤一中的所述衬底为硅衬底。

22、优选地,步骤二中的所述浅沟槽隔离的深度为2500至3000埃。

23、优选地,步骤三中所述通过控制栅光罩,同时注入p型杂质离子和n型杂质离子,分别形成所述p型掺杂区和所述n型掺杂区,不额外增加光罩层数。

24、优选地,步骤四中的所述侧墙由位于所述控制栅上的氧化层侧墙以及位于所述氧化层侧墙上的氮化层侧墙组成。

25、优选地,步骤四中利用热氧化法形成所述栅介质层。

26、优选地,步骤五中的所述金属互连结构的形成方法包括:形成覆盖所述多晶硅浮栅的层间介质层;在所述层间介质层上形成于所述n型重掺杂区、所述多晶硅浮栅、控制栅连通的接触孔;形成填充所述接触孔的金属层。

27、如上所述,本发明的多次可编程存储单元结构及其制造方法,具有以下有益效果:

28、本发明减淡浅沟槽隔离底部n型杂质离子浓度,可以有效防止wl to wl(字线至字线)击穿,减小漏电,改善wl to wl隔离耐压,同时解决因工艺波动等所导致的wl to wl隔离耐压波动较大问题,提高工艺窗口;本发明器件的cg to pw(控制栅至p型阱区)以及wlto wl隔离耐压可以达到现有器件水平。

技术特征:

1.一种多次可编程存储单元结构,其特征在于,包括:

2.根据权利要求1所述的多次可编程存储单元结构,其特征在于:所述衬底为硅衬底。

3.根据权利要求1所述的多次可编程存储单元结构,其特征在于:所述浅沟槽隔离的深度为2500至3000埃。

4.根据权利要求1所述的多次可编程存储单元结构,其特征在于:通过控制栅光罩,同时注入n型和p型杂质离子,分别形成所述p型掺杂区和所述n型掺杂区。

5.根据权利要求1所述的多次可编程存储单元结构,其特征在于:所述侧墙由位于所述控制栅上的氧化层侧墙以及位于所述氧化层侧墙上的氮化层侧墙组成。

6.根据权利要求1所述的多次可编程存储单元结构,其特征在于:所述金属互连结构的形成方法包括:形成覆盖所述多晶硅浮栅的层间介质层;在所述层间介质层上形成于所述n型重掺杂区、所述多晶硅浮栅连通的接触孔;形成填充所述接触孔的金属层。

7.根据权利要求1至5任一项所述的多次可编程存储单元结构的制造方法,其特征在于:

8.根据权利要求6所述的多次可编程存储单元结构的制造方法,其特征在于:步骤一中的所述衬底为硅衬底。

9.根据权利要求6所述的多次可编程存储单元结构的制造方法,其特征在于:步骤二中的所述浅沟槽隔离的深度为2500至3000埃。

10.根据权利要求6所述的多次可编程存储单元结构的制造方法,其特征在于:步骤三中通过控制栅光罩注入p型杂质离子和n型杂离子,分别形成所述p型掺杂区和所述n型掺杂区。

11.根据权利要求6所述的多次可编程存储单元结构的制造方法,其特征在于:步骤四中的所述侧墙由位于所述控制栅上的氧化层侧墙以及位于所述氧化层侧墙上的氮化层侧墙组成。

12.根据权利要求6所述的多次可编程存储单元结构的制造方法,其特征在于:步骤四中利用热氧化法形成所述栅介质层。

13.根据权利要求6所述的多次可编程存储单元结构的制造方法,其特征在于:步骤五中的所述金属互连结构的形成方法包括:形成覆盖所述多晶硅浮栅的层间介质层;在所述层间介质层上形成于所述n型重掺杂区、所述多晶硅浮栅连通的接触孔;形成填充所述接触孔的金属层。

技术总结

本发明提供一种多次可编程存储单元结构,包括P型的衬底,在衬底上形成有P型的外延层,在外延层上形成有深N型掺杂区;形成于外延层上的浅沟槽隔离,浅沟槽隔离用于定义出有源区;分别形成于有源区上的P型阱区以及P型掺杂区,P型掺杂区的掺杂浓度低于P型阱区,P型掺杂区为形成控制栅的区域;形成于P型掺杂区表面的N型掺杂区,N型掺杂区作为控制栅,其中靠近N型掺杂区处浅沟槽隔离底部的N型杂质离子浓度低于预设值;形成于P型阱区和P型掺杂区上的栅介质层以及位于栅介质层上的多晶硅浮栅;形成于多晶硅浮栅侧壁上的侧墙。本发明可以有效解因工艺波动等所导致的WL to WL(字线至字线)隔离耐压波动较大问题,同时防止WLto WL穿通,减小漏电,改善隔离耐压。

技术研发人员:宋婉,刘冬华,许昭昭

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!