电路板组件、DDR内存电路布线方法以及电子设备与流程

本发明属于电路板布线,尤其涉及一种带有多通道ddr内存电路的电路板组件、ddr内存电路布线方法以及电子设备。

背景技术:

1、ddr内存芯片技术在电路布线设计中广泛使用,主要用于保障ddr内存芯片能够工作在最大设计速率,满足处理芯片的高内存需求。

2、在ddr内存芯片拓扑结构方面,一般优先采用t形拓扑结构,虽然能实现等长绕线,但t形拓扑结构支持的ddr内存芯片的个数不多,一般不超过4颗,同时地址线面积占用大,增大了工程师绘制地址线的时间,降低了工作效率。

3、同时,由于电子设备(如超薄笔记本电脑)的结构限制(厚度薄)无法在电子设备上使用大体积的ddr内存芯片,进而造成处理芯片无法在电子设备上实现大内存。

4、基于以上原因,亟需一种能够解决以上技术问题的处理芯片用电路布线方法。

技术实现思路

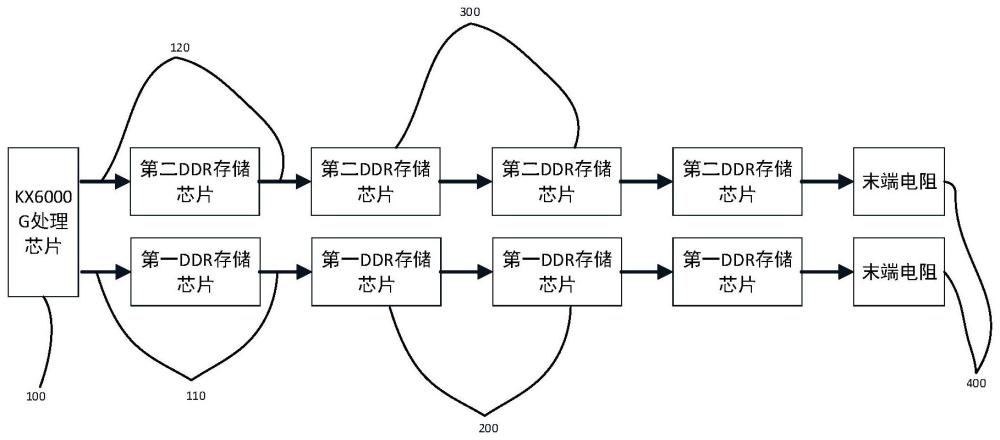

1、本发明的目的在于克服上述现有技术的不足,提供一种带有多通道ddr内存电路的电路板组件、ddr内存电路布线方法以及电子设备,其中,处理芯片与最靠近的ddr内存芯片之间、每两相邻的ddr内存芯片之间的地址线均等长且呈菊花链布局,减少了工程师绘制地址线的时间,提升了工作效率,减小了地址线绕线占用pcb电路板的面积,采用多个串联设置的ddr内存芯片可以在电子设备结构限制的情况下增大内存。

2、本发明是这样实现的,一种带有多通道ddr内存电路的电路板组件,应用于电子设备上,包括:

3、pcb电路板,布置有a通道地址线和b通道地址线;

4、pcb电路板的背面依次串联设置多颗第一ddr内存芯片,在pcb电路板的正面依次串联设置多颗第二ddr内存芯片,其中,多颗第一ddr内存芯片与多颗第二ddr内存芯片一一对称设置;

5、处理芯片,通过a通道地址线与多颗第一ddr内存芯片进行通信,通过b通道地址线与多颗第二ddr内存芯片进行通信;

6、其中,多颗第一ddr内存芯片按相邻位置进行两两分组分成多个第一分组,各个第一分组中的ddr内存芯片之间的a通道地址线的第一长度相等,排布位置最靠近处理芯片的第一ddr内存芯片与处理芯片之间的a通道地址线的长度,和所述第一长度相等;

7、多颗第二ddr内存芯片按相邻位置进行两两分组分成多个第二分组,各个第二分组中的ddr内存芯片之间的b通道地址线的第二长度相等,排布位置最靠近处理芯片的第二ddr内存芯片与处理芯片之间的b通道地址线的长度,和所述第二长度相等;

8、其中,a通道地址线和b通道地址线呈菊花链拓扑布局。

9、进一步地,a通道地址线包括多根第一分地址线,b通道地址线包括多根第二分地址线,在处理芯片与各个第一ddr内存芯片的同一个布线分段中,各个第一分地址线的长度相等;在处理芯片与第二ddr内存芯片的同一个布线分段中,各个第二分地址线的长度相等。

10、优选地,每颗ddr内存芯片的出线端的长度均一致。

11、优选地,所述第一长度和第二长度的公差范围为±1mil。

12、优选地,该pcb电路板采用十层板布线,其中,处理芯片布置在pcb电路板的正面,pcb电路板每层均具有可供a通道地址线的第一组地址线穿过的第一组通孔,a通道地址线中的第一组地址线通过第一组通孔传输至pcb电路板的背面,再通过pcb电路板的第八层与第十层之间的第一组盲埋孔在pcb电路板的第八层布线,最后通过pcb电路板的第十层到第八层之间的第二组盲埋孔与pcb电路板背面的第一颗ddr内存芯片连接;

13、a通道地址线中的第二组地址线通过第二组通孔传输至pcb电路板的背面布线,再通过pcb电路板的第三组通孔在pcb电路板的第六层布线,最后通过第四组通孔与pcb电路板背面的第一颗ddr内存芯片连接。

14、优选地,b通道地址线中的第一组地址线通过pcb电路板的第一层与第三层之间的第三组盲埋孔在pcb电路板的第三层布线,最后通过pcb电路板第一层与第三层之间的第四组盲埋孔与pcb电路板正面的第一颗ddr内存芯片连接;

15、b通道地址线中的第二组地址线通过pcb电路板的第五组通孔在pcb电路板的第五层布线,最后通过pcb电路板的第六组通孔与pcb电路板正面的第一颗ddr内存芯片连接。

16、本发明提供的一种ddr内存电路布线方法,包括:

17、在pcb电路板的背面依次串联设置多颗第一ddr内存芯片,在pcb电路板的正面依次串联设置多颗第二ddr内存芯片,将多颗第一ddr内存芯片与多颗第二ddr内存芯片一一对称设置;

18、处理芯片通过a通道地址线与多颗第一ddr内存芯片连接,通过b通道地址线与多颗第二ddr内存芯片连接;

19、多颗第一ddr内存芯片按相邻位置进行两两分组分成多个第一分组,各个第一分组中的第一ddr内存芯片之间的a通道地址线的第一长度相等,排布位置最靠近处理芯片的第一ddr内存芯片与处理芯片之间的a通道地址线的长度,和所述第一长度相等;

20、多颗第二ddr内存芯片按相邻位置进行两两分组分成多个第二分组,各个第二分组中的第二ddr内存芯片之间的b通道地址线的第二长度相等,排布位置最靠近处理芯片的第二ddr内存芯片与处理芯片之间的b通道地址线的长度,和所述第二长度相等;

21、a通道地址线和b通道地址线呈菊花链拓扑布局。

22、进一步地,a通道地址线包括多根第一分地址线,b通道地址线包括多根第二分地址线,在处理芯片与各个第一ddr内存芯片的同一个布线分段中,a通道地址线中的多根第一分地址线的长度均相等;在处理芯片与第二ddr内存芯片的同一个布线分段中,b通道地址线中的多根第二分地址线的长度均相等。

23、本发明还提供了一种电子设备,包括以上所述的带有多通道ddr内存电路的电路板组件。

24、本发明提供的一种带有多通道ddr内存电路的电路板组件、ddr内存电路布线方法以及电子设备,包括布局有a通道地址线、b通道地址线和处理芯片的pcb电路板,在pcb电路板的背面串联设置多颗第一ddr内存芯片,在pcb电路板的正面串联设置多颗第二ddr内存芯片,第一ddr内存芯片与第二ddr内存芯片一一对称设置;采用多个串联设置的ddr内存芯片可以在电子设备结构限制的情况下增大内存,其中,处理芯片与临近的第一颗第一ddr内存芯片之间、每两个相邻的第一ddr内存芯片之间的a通道地址线的长度均相等;处理芯片与背面的第一颗第二ddr内存芯片之间、每两相邻的第二ddr内存芯片之间的b通道地址线的长度均相等,a通道地址线和b通道地址线呈呈菊花链拓扑布局。采用以上结构设计,减少了工程师绘制地址线的时间,提升了工作效率,减小了地址线绕线占用pcb电路板的面积。

技术特征:

1.一种带有多通道ddr内存电路的电路板组件,应用于电子设备上,其特征在于,所述电路板组件包括pcb电路板,布设在pcb电路板上的处理芯片、多颗第一ddr内存芯片和多颗第二ddr内存芯片,其中:

2.根据权利要求1所述的电路板组件,其特征在于,a通道地址线包括多根第一分地址线,b通道地址线包括多根第二分地址线,在处理芯片与各个第一ddr内存芯片的同一个布线分段中,各个第一分地址线的长度相等;在处理芯片与第二ddr内存芯片的同一个布线分段中,各个第二分地址线的长度相等。

3.根据权利要求1或2所述的电路板组件,其特征在于,每颗ddr内存芯片的出线端的长度均一致。

4.根据权利要求3所述的电路板组件,其特征在于,所述第一长度和第二长度的公差范围为±1mil。

5.根据权利要求1或2所述的电路板组件,其特征在于,该pcb电路板采用十层板布线,其中,处理芯片布置在pcb电路板的正面,pcb电路板每层均具有可供a通道地址线的第一组地址线穿过的第一组通孔,a通道地址线中的第一组地址线通过第一组通孔传输至pcb电路板的背面,再通过pcb电路板的第八层与第十层之间的第一组盲埋孔在pcb电路板的第八层布线,最后通过pcb电路板的第十层到第八层之间的第二组盲埋孔与pcb电路板背面的第一颗ddr内存芯片连接;

6.根据权利要求5所述的电路板组件,其特征在于,b通道地址线中的第一组地址线通过pcb电路板的第一层与第三层之间的第三组盲埋孔在pcb电路板的第三层布线,最后通过pcb电路板第一层与第三层之间的第四组盲埋孔与pcb电路板正面的第一颗ddr内存芯片连接;

7.一种ddr内存电路布线方法,其特征在于,包括:

8.根据权利要求7所述的ddr内存电路布线方法,其特征在于,a通道地址线包括多根第一分地址线,b通道地址线包括多根第二分地址线,在处理芯片与各个第一ddr内存芯片的同一个布线分段中,a通道地址线中的多根第一分地址线的长度均相等;在处理芯片与第二ddr内存芯片的同一个布线分段中,b通道地址线中的多根第二分地址线的长度均相等。

9.根据权利要求8所述的ddr内存电路布线方法,其特征在于,在等长布线过程中,需要依次完成上一段等长布线后才能开始下一段等长布线。

10.一种电子设备,其特征在于,包括权利要求1至6中任一项所述的带有多通道ddr内存电路的电路板组件。

技术总结

一种带有多通道DDR内存电路的电路板组件、DDR内存电路布线方法以及电子设备,包括布局有a通道地址线、b通道地址线和处理芯片的PCB电路板,在PCB电路板的正面和背面分别串联设置多颗第一DDR内存芯片和第二DDR内存芯片,多颗第一DDR内存芯片与多颗第二DDR内存芯片一一对称设置;采用多个串联设置的DDR内存芯片可以在电子设备结构限制的情况下增大内存,其中,处理芯片分别与最靠近的第一颗DDR内存芯片之间、背面和正面每两个相邻的DDR内存芯片之间的a通道地址线和b通道地址线的长度均相等且呈菊花链布局,此种结构设计,减少了工程师绘制地址线的时间,提升了工作效率,减小了地址线绕线占用PCB电路板的面积。

技术研发人员:李祝军,唐智鹏

受保护的技术使用者:深圳微步信息股份有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!