数字换能器接口加扰的制作方法

数字换能器接口加扰

1.相关专利申请的交叉引用

2.本申请要求2018年10月9日提交的美国临时专利申请no.62/743,498的权益和优先权,其全部内容通过引用而并入本文。

背景技术:

3.当今的便携式通信装置通常包括多个数字麦克风组件(诸如两个、四个甚或更多个麦克风组件),这些数字麦克风组件经由标准化数据通信接口联接至共享数据总线。使用时分方案,根据相关的通信协议,将所述多个数字麦克风组件的相应数据流写入到共享数据总线上。便携式通信装置的数字微处理器或数字信号处理器(dsp)通常包括对应的标准化数据通信接口,以用于接收由多个数字麦克风组件生成的时分复用数据流。所述多个数字麦克风组件同时工作以将相应的传入声音转换成对应的音频数据流。便携式通信装置的数字微处理器或dsp充任总线主控器(bus master),并且用于解码共享数据总线上的时分复用音频数据流,并将该音频数据流转换成原始数字麦克风信号。原始数字麦克风信号表示数字麦克风组件上的传入声音。通常将便携式通信装置的数字微处理器或dsp配置或编程为,操纵所述多个原始数字麦克风信号,以对传入声音产生各种希望的增强效果,诸如波束成形、噪声抑制、反馈抵消等。

4.然而,发明人已经认识到,将多个数字麦克风组件连接到共享数据总线上会导致某些明显的缺点。这些缺点之一是,由第一数字麦克风组件输出至共享数据总线的结构化数据流对被联接至共享数据总线的另一个第二数字麦克风组件的功能和/或性能产生负面影响,反之亦然。因此,在第一数字麦克风组件与第二数字麦克风组件之间存在有害的交叉调制,并且随着被连接至共享数据总线的数字麦克风组件的数量增加,该问题趋于加剧。

5.通过数字麦克风组件将结构化数据流写入到共享数据总线上,可能会在完整的多麦克风系统和托管该完整的多麦克风系统的便携式通信装置中产生其它类型的不希望的副作用。由于特定数字麦克风组件的结构化数据流的频谱内容与所传输的数据的内容高度相关,因此至少部分地产生了这些问题。由经脉冲密度调制(pdm)编码的音频信号所输送的结构化数据流的功率谱,以及数字麦克风组件的电源的电流消耗与音频信号本身高度相关。另外,通常由数字麦克风组件的过采样和噪声整形(noise

‑

shaped)adc电路所生成的经噪声整形的pdm信号包括低于adc的采样频率的一半或者处于adc的采样频率的一半的高频频谱分量。对于典型的数字麦克风组件,adc的采样频率可能高于2mhz。这些高频频谱分量以及通常具有高振幅的所有频谱分量在便携式通信装置的其它类型的电子电路中,通常是干扰问题或emi问题的来源。

6.所有类型的数字换能器装置(包括上面所讨论的数字麦克风组件)可以指定:

7.1)对传入的emi噪声机制的一定程度的暴露依从性,例如,表达为psrr或rf暴露耐受水平等。

8.2)特定的emi辐射水平。后者可能需要在指定/标准化条件(诸如pcb板设置、总线长度、迹线宽度等)下的有保证的最大rf辐射水平。

附图说明

9.本公开的前述和其它特征根据下面结合附图的描述和所附权利要求将完全变得更加显而易见。附图仅描绘了根据本公开的几个实施方式,并因此不应被视为对其范围的限制。下面,结合附图对各种实施方式进行更详细描述。

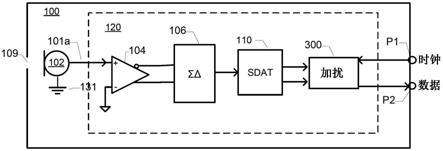

10.图1是根据一些实施方式的示例微型数字麦克风组件的框图,该微型数字麦克风组件包括被联接至集成电路的信号处理电子装置的mems换能器部件。

11.图2是根据一些实施方式的示例性微型数字麦克风组件的侧截面视图。

12.图3示出了根据一些实施方式的示例性微型数字麦克风组件的集成电路的示例性数字加扰电路的简化框图。

13.图4示出了根据一些实施方式的示例性数字解扰电路的简化框图。

14.图5示出了根据一些实施方式的示例性多麦克风系统的简化框图,该多麦克风系统包括被联接至共享数据总线的多个微型数字麦克风组件。

15.图6示出了根据一些实施方式的示例性微型数字麦克风组件的结构化数据流输出以及加扰数据流输出的相应频谱标绘图。

具体实施方式

16.在下面的详细描述中,参照附图,对各种实施方式进行描述。本领域技术人员应当明白,附图是示意性的并且为清楚起见而进行了简化,并因此仅示出对于理解本公开而言必不可少的细节,而其它细节则被省去了。贯穿全文,相同标号是指相同要素或组件。因此,不必针对各个附图来详细描述相同的要素或组件。还应意识到,特定动作和/或步骤可以按出现的特定次序描述或描绘,而本领域技术人员应理解,这种关于顺序的特异性实际上并不需要。

17.本公开的第一方面涉及一种可连接至微机电系统(mems)换能器的集成电路,该mems换能器被配置成响应于声音而生成换能器音频信号。该集成电路包括:输入端子,该输入端子可连接至mems换能器的输出端;模数转换器(adc),该adc被联接至输入端子,并且被配置成在集成电路被连接至mems换能器时,通过对换能器音频信号进行采样和量化来生成对应的数字音频流;模数转换器(adc),该adc被联接至输入端子,并且被配置成在集成电路被连接至mems换能器时,通过对换能器音频信号进行采样和量化来生成对应的数字音频流;数据通信接口,该数据通信接口被联接至adc的输出端,并且被配置成根据预定数据协议来将数字音频流转换成结构化数据流;数字加扰电路,该数字加扰电路被联接至数据通信接口,并且被配置成将结构化数据流变换成对应的加扰数据流;以及数据总线接口,该数据总线接口被联接至数字加扰电路,并且被配置成输出加扰数据流。

18.本公开的第二方面涉及麦克风组件,该麦克风组件包括壳体以及mems换能器部件,该mems换能器部件被设置在壳体中,并且被配置成将声音转换成换能器输出端处的换能器音频信号。该麦克风组件还包括集成电路,该集成电路可连接至mems换能器并且包括:输入端子,该输入端子被连接至换能器输出端以用于接收换能器音频信号;模数转换器(adc),该adc被联接至输入端子,并且被配置成在集成电路被连接至mems换能器时,通过对换能器音频信号进行采样和量化来生成对应的数字音频流;数据通信接口,该数据通信接口被联接至adc的输出端,并且被配置成根据预定数据协议来将数字音频流转换成结构化

数据流;数字加扰电路,该数字加扰电路被联接至数据通信接口,并且被配置成将结构化数据流变换成对应的加扰数据流;以及数据总线接口,该数据总线接口被联接至数字加扰电路,并且被配置成输出加扰数据流。该麦克风组件还包括外部装置接口,该外部装置接口包括被设置在壳体的表面上的多个触点,其中,该集成电路的数据总线接口被联接至所述多个触点。

19.本公开的第三方面涉及多麦克风系统,该多麦克风系统包括:第一麦克风组件、第二麦克风组件、主处理器以及通信接口。第一麦克风组件包括:第一壳体;第一mems换能器部件,该第一mems换能器部件被设置在第一壳体中,并且被配置成将声音转换成第一mems换能器部件的换能器输出端处的第一换能器音频信号;以及可连接至第一mems换能器的第一集成电路。第一集成电路包括:第一输入端子,该第一输入端子被连接至第一mems换能器部件的换能器输出端以用于接收第一换能器音频信号;第一模数转换器(adc),该第一adc被联接至第一输入端子,并且被配置成在第一集成电路被连接至第一mems换能器时,通过对第一换能器音频信号进行采样和量化来生成对应的第一数字音频流;第一数据通信接口,该第一数据通信接口被联接至第一adc的输出端,并且被配置成根据预定数据协议来将第一数字音频流转换成第一结构化数据流;第一数字加扰电路,该第一数字加扰电路被联接至第一数据通信接口,并且被配置成将第一结构化数据流变换成对应的第一加扰数据流;以及第一数据总线接口,该第一数据总线接口被联接至第一数字加扰电路,并且被配置成将第一加扰数据流输送到共享数据总线上。第二麦克风组件包括:第二壳体;第二mems换能器部件,该第二mems换能器部件被设置在第二壳体中,并且被配置成将声音转换成第二mems换能器部件的换能器输出端处的第二换能器音频信号;以及可连接至第二mems换能器的第二集成电路。第二集成电路包括:第二输入端子,该第二输入端子被连接至第二mems换能器部件的换能器输出端以用于接收第二换能器音频信号;第二模数转换器(adc),该第二adc被联接至第二输入端子,并且被配置成在第二集成电路被连接至第二mems换能器时,通过对第二换能器音频信号进行采样和量化来生成对应的第二数字音频流;第二数据通信接口,该第二数据通信接口被联接至第二adc的输出端,并且被配置成根据预定数据协议来将第二数字音频流转换成第二结构化数据流;第二数字加扰电路,该第二数字加扰电路被联接至第二数据通信接口,并且被配置成将第二结构化数据流变换成对应的第二加扰数据流,其中,第二加扰数据流和第一加扰数据流是不相关的;以及第二数据总线接口,该第二数据总线接口被联接至第二数字加扰电路,并且被配置成将第二加扰数据流输送到共享数据总线上。主处理器包括第三数据总线接口,该第三数据总线接口从共享数据总线接收第一加扰数据流和第二加扰数据流;以及第三数字解扰电路,该第三数字解扰电路被配置为根据一个或更多个解扰算法,对第一加扰数据流和第二加扰数据流进行解复用并转换成对应的结构化数据流。通信接口被配置成,根据预定数据协议从结构化数据流中取回(retrieve)第一数字音频流和第二数字音频流。

20.本发明的多麦克风系统显著减少了与现有技术的多麦克风系统以及数字麦克风组件相关联的上述emi辐射问题以及emi耐受性或依从性问题。在集成电路上或者在数字麦克风组件上的数字加扰电路的操作通过使由数字麦克风组件响应于传入的声音而生成的结构化数据流的频谱分量白化(whitening)或随机化,来以希望的方式修改或变换共享数据总线上的开关活动。结构化数据流的频谱分量的这种白化或随机化消除了或者显著减少

了数据流与音频信号本身之间的上述相关性。换句话说,数字加扰电路将结构化数据流(诸如pdm编码流)变换成对应的加扰数据流,该加扰数据流优选地包含完全相同的信息,但是其中频谱分量与音频信号本身是不相关的。

21.本公开的第四方面涉及一种在音频信号处理集成电路中对数字音频流进行处理的方法。所述方法包括以下步骤:从微机电系统(mems)换能器接收换能器音频信号;通过使用模数转换器(adc)对换能器音频信号进行采样和量化来生成对应的数字音频流;根据数据通信接口的预定数据协议,将数字音频流转换成结构化数据流;将结构化数据流变换成对应的加扰数据流;以及经由数据总线接口从音频信号处理集成电路输出加扰数据流。

22.本发明的集成电路、数字加扰电路以及加扰方法能有效消除经由多麦克风系统的所述多个数字麦克风组件中的单独的数字麦克风组件之间的共享数据总线的交叉调制或干扰。实现这种效果的一种机制是,与结构化数据流的频谱分量相比,加扰数据流的频谱分量在频率上相对均匀分散,使得结构化数据流的明显频谱峰值被消除。这些明显的频谱峰值通常是多麦克风系统的各个组件中的非线性和相互调制的来源,从而在所述数字麦克风组件中的单独数字麦克风组件之间产生上述交叉调制或干扰问题。交叉调制往往会降低单独数字麦克风组件的重要性能指标,诸如信噪比、pssr等。

23.可以将数字解扰电路集成在本发明的多麦克风系统的主装置或处理器上。该数字解扰电路被设计、配置或构造成,使所述多个数字麦克风组件的所述数字加扰电路中的各个数字加扰电路的操作反转。按这种方式,数字解扰电路可以初始地解复用共享数据总线上的所述多个加扰数据流,此后根据一种或更多种预定解扰算法,将取回的加扰数据流解码或解扰成对应的结构化数据流。

24.下面,参照附图,对所述集成电路的实施方式进行详细描述。

25.图1示出了示例微型数字麦克风组件100的电框图,该微型数字麦克风组件包括被联接至集成电路120的信号处理电子装置的mems换能器部件102。可以将mems换能器部件102可以被设置在壳体103(图2所示)中。将mems换能器部件102配置成,在换能器输出端101a处将声音转换成对应的换能器音频信号。可以将换能器音频信号作为单端信号或差分信号施加至麦克风前置放大器或跨导放大器104的反相输入端和非反相输入端中的一个或两个输入端。可以使用亚微米cmos技术或者任何其它合适的半导体制造技术将集成电路120形成为单独的集成电路。麦克风前置放大器104接收由mems换能器部件102生成的换能器音频信号。作为输出,麦克风前置放大器104根据麦克风前置放大器104的预定小信号电压放大或跨导(gm),来生成表示换能器音频信号的差分电流信号或差分电压信号。将该差分电流信号或差分电压信号提供给电压输入或电流输入模数转换器(adc)106的输入端。

26.将adc 106配置为对换能器音频信号进行采样和量化以生成对应的数字音频流。adc 106可以是过采样类型的,例如,采样频率高于1mhz或高于3mhz,并且适于根据特定的转换器类型来生成表示换能器音频信号的多位或一位数字麦克风信号。麦克风前置放大器104优选地表现出大的输入阻抗,诸如大于100mω,诸如大于1gω。

27.将在adc 106的输出端处提供的数字音频流提供给专有或行业标准的数据通信接口(sdat)110的输入端,该sdat被配置成,根据预定数据协议将数字音频流转换成结构化数据流。该预定数据协议可以是串行数据协议,诸如所谓的传统pdm、i2s、usb、soundwire或spi。该预定数据协议可以支持双向数据传输或单向数据传输。可以将某些协议配置成在结

构化数据流中排它地传输音频数据(诸如传统pdm协议),而其它的数据协议则支持各种类型的控制信息的传输。标准化数据通信接口优选地包括单独的时钟线(clk),该clk对通过接口110的单独且相关联的数据线或数据线路(data)输送的结构化数据流的数据的定时进行控制。在一个实施方式中,标准化数据通信接口110还包括数字命令和控制接口,该数字命令和控制接口可以被配置成,从便携式通信装置(例如,智能手机)的主处理器(未示出)接收各种类型的数据命令。

28.将结构化数据流从数据通信接口110的输出端施加至数字加扰电路300的输入端。将数字加扰电路300配置成,根据在数字加扰电路300中实现的乘法/自同步加扰算法或加法或同步加扰算法,将结构化数据流变换成对应的加扰数据流,如下面另外详细讨论的。该集成电路120另外包括外部装置接口,该外部装置接口可以包括被安装在载体基板111的顶表面或底表面上的多个触点或焊盘p1、p2。该数据总线接口经由外部装置接口de触点p1、p2,在共享或公共数据总线(未示出)上输出加扰数据流。该数据总线接口可以包括各种总线驱动器电路。该数据总线接口和外部装置接口允许将微型数字麦克风组件100经物理和电联接或连接至共享数据总线。该共享数据总线可以包括被设置在先前讨论的便携式通信装置的载体基板(例如,印刷电路板)上的多个电线或导体。

29.图2是上面讨论的微型数字麦克风组件100的具体实施方式的壳体的侧截面图。在本实施方式中,该mems换能器部件102包括用于捕获和转换可听范围内的声音信号的电容式声换能器,即,mems麦克风部件。将该电容式mems换能器部件102配置成,将在20hz到20khz之间的可听范围的至少一部分内的传入声音转换成对应的经数字编码的麦克风信号。该电容式mems换能器部件102例如可以表现出介于0.5pf到10pf之间的换能器电容。该电容式换能器部件可以包括分别提供麦克风信号的第一互充电换能器电极和第二互充电换能器电极(例如,振膜135和背板136)。可以通过恰当的高阻抗dc偏压电源(未示出)将电荷注入振膜135和背板136之一上。另选地,该换能器可以是压电装置或者某一其它已知的或将来的换能器。

30.该麦克风组件100另外包括先前讨论的集成电路120,该集成电路可以包括半导体管芯,例如,集成本文所公开的各种模拟和数字电路的混合信号cmos半导体器件。该集成电路120例如被整形并且调整尺寸,以安装在组装件100的基板或载体部件111上,其中,该载体部件111同样支承电容式mems换能器部件102。该麦克风组件100包括壳体,该壳体包括被安装到基板或载体部件111的外周边缘上的盖子103,使得盖子103和载体部件111共同形成以下麦克风壳体:该麦克风壳体包围换能器部件102和集成电路120,并且保护该换能器部件和集成电路免受外部环境的污染(诸如灰尘、湿气、热、emi信号)。该麦克风壳体103可以包括贯穿载体部件111或者在其它实施方式中贯穿盖子103的声音入口或声孔109,以供将声波输送至mems换能器部件102。

31.mems换能器部件102响应于冲击(impinging)声音而在换能器输出端(例如,参见图1的项101a)处生成先前讨论的换能器音频信号。该换能器输出端例如可以包括mems部件102的焊盘或端子,该焊盘或端子经由一个或更多个焊线107电联接至处理电路122。该处理电路122可以与集成电路120类似、相同,或者可以包括该集成电路。

32.图3示出了微型数字麦克风组件100的集成电路120的示例性数字加扰电路300的简化框图。将数字加扰电路300配置成,根据预定的z域传递函数,对施加在数字加扰电路

300的输入节点301处的结构化数据流s.in执行或实现乘法或自同步加扰算法。该数字加扰电路300在输出节点311处生成对应的加扰数据流s.out。该预定的z域传递函数优选地由根据h(x)=x

m

+c

m

‑1·

x

m

‑2+

…

+1的最大长度不可约多项式h(x)来进行定义;其中,m是一个正整数,例如,介于8到40之间的正整数。数字加扰电路300包括:多个数字异或(xor)门310a、310b、310c、310d;多个数字触发器电路320a、320b、320c、320d;以及系数存储器部件c1、c2、c3以及c

m

。

33.z域传递函数由以下列出的方程进行定义:

[0034][0035]

技术人员应意识到,数字触发器电路320a、320b、320c、320d中的各个数字触发器电路皆是根据时钟信号进行工作的,并因此在所述数字异或门310a、310b、310c、310d中的各个数字异或门实现数字乘法功能时向该数字触发器电路的输入信号提供单位延迟,以便与系数存储器部件c1、c2、c3以及c

m

组合地共同实现选定的z域传递函数。最大长度不可约多项式h(x)的长度可以在实际的约束内,经由正整数m的值进行自由选择,其中,该多项式的阶次是c_m=1的m的最高值。给定的实现将具有有限数量的系数存储器部件,各个系数存储器部件的值为{0、1}。

[0036]

技术人员将理解,集成电路120的数字加扰电路300的另选实施方式可以包括加法或同步加扰或编码算法,该加法或同步加扰或编码算法被配置为,根据伪随机二进制序列(prbs)对结构化数据流进行编码。该加法或同步加扰算法例如可以基于具有预定多项式和预定初始状态的线性反馈移位寄存器(lfsr)。

[0037]

图4示出了微型数字麦克风组件100的集成电路120的示例性数字解扰电路400的简化框图。将该数字解扰电路400配置成,执行或实现乘法或自同步解扰算法,该乘法或自同步解扰算法是上面讨论的由数字加扰电路300执行的上述数字加扰算法的反转。在数字解扰电路400的输入节点401处施加特定数字麦克风的加扰数据流d.in,并且在数字解扰电路400的输出节点411处恢复或解码所讨论的数字麦克风的对应的结构化数据流d.out。

[0038]

数字解扰电路400包括:多个数字异或门410a、410b、410c、410d;多个数字触发器电路420a、420b、420c、420d;以及系数存储器部件c1、c2、c3以及c

m

。

[0039]

数字解扰电路400的z域传递函数由以下列出的方程进行定义:

[0040][0041]

技术人员将理解,由于由数字加扰电路300和数字解扰电路400所执行的组合的加扰和解扰算法的乘法性质,数字解扰电路400是自同步的。

[0042]

图5示出了示例性多麦克风系统500的简化框图,该多麦克风系统包括被联接至共享数据总线的四个微型数字麦克风组件100a、100b、100c、100d,该共享数据总线包括时钟导线405和数据导线407。本领域技术人员应意识到,系统500的其它实施方式可以包括更少(例如,一个、两个)或更多的微型数字麦克风组件。可以将多麦克风系统500集成在诸如智能手机的便携式通信装置(未示出)中,在该智能手机中,将微型数字麦克风组件100a、100b、00c、100d设置在该智能手机的外壳的不同物理位置。所述微型数字麦克风组件100a、100b、100c、100d中的各个微型数字麦克风组件皆可以对应于上面讨论的微型数字麦克风

组件100。各个微型数字麦克风组件的数据总线接口经由一个或更多个外部可接入的焊盘或端子p

‑

1、p

‑

2电联接或连接至共享数据总线,这些焊盘或端子例如被设置在所述组件的载体上。所述微型数字麦克风组件中的各个微型数字麦克风组件皆包括电源焊盘或端子p

‑

3、p7,用于接收可能处于1.5v到2.0v之间的电源电压v

dd

。所述微型数字麦克风组件中的各个微型数字麦克风组件皆可以包括编程引脚p

‑

4,该编程引脚可以通过将p

‑

4焊盘接地或者连接至电源电压v

dd

,来设定数字麦克风组件的某一参数、状态或标识(例如左或右)。

[0043]

将所述四个数字麦克风组件100a、100b、100c、100d的相应的数据加扰电路配置成,例如通过在它们相应的加扰算法之间引入某一相移,或者通过使用对结构化数据流进行加扰或转换的不同的多项式h(x)函数,来生成不相关的加扰数据流。特定的微型数字麦克风组件的加扰算法的相移可以通过焊盘/引脚编程来进行设定,并且使用与上面讨论的p

‑

4相同的引脚来为麦克风组件指派左或右标识。如果微型数字麦克风组件的数据通信接口不支持控制数据交换(诸如传统的pdm数据通信接口),那么这将是特别有益的。否则,可以例如通过主处理器将微型数字麦克风组件的加扰算法的相移写入数字加扰电路300可访问的特定存储器寄存器或存储器区域。这可使主处理器能够控制被连接至共享数据总线的所述多个微型数字麦克风组件的相应的相移设定。

[0044]

该多麦克风系统500包括主处理器505,诸如便携式通信装置的先前讨论的数字微处理器或dsp。主处理器505包括总线主控电路(bus master circuit)508,该总线主控电路用于对共享数据总线上的时分复用音频数据流进行解码。该总线主控电路508包括总线接口,该总线接口包括将总线主控电路508电连接至共享数据总线的i/o焊盘521、522。因此,总线主控电路508从共享数据总线接收四个加扰数据流,并且初始地对这四个加扰数据流进行解复用,以产生与所述四个数字麦克风组件100a、100b、100c、100d相对应的四个独立的加扰数据流。此后,总线主控电路508通过应用适当的数字解扰电路400,来将各个加扰数据流变换成对应的结构化数据流,该数字解扰电路基于与所讨论的数字麦克风组件的数字加扰电路300相同的加扰算法或多项式h(x)函数。因而,该数字解扰电路400可以包括四个不同的解扰算法,这四个不同的解扰算法是由数字麦克风组件的所述四个数字加扰电路所执行的所述四个加扰算法中的相应的加扰算法的反转。因而,总线主控电路508向主处理器500的标准化数据通信接口504输出所述四个结构化数据流,这四个结构化数据流对应于由所述四个数字麦克风组件100a、100b、100c、100d的相应的标准化数据通信接口所生成的结构化数据流。该标准化数据通信接口504将结构化数据流转换成由所述四个数字麦克风组件100a、100b、100c、100d所生成的对应的数字音频信号。如果共享数据总线上的数据协议支持这种控制信息的传输,则可以将主控电路508另外配置成,从结构化数据流中提取各种类型的控制数据。

[0045]

技术人员应意识到,解扰电路400可以基于专用且适当配置的数字电路模块和部件,或者基于包括可执行微处理器代码的软件例程或应用程序。因此,在某些实施方式中,由数字解扰电路400所执行的解扰算法可以由如图4示意性例示的数字电路模块和部件来执行。另选地,可以通过在便携式通信装置的数字微处理器或dsp上执行的可执行微处理器代码来执行解扰算法。

[0046]

图6示出了通过应用上面讨论的加扰算法和数字加扰电路而在数字麦克风组件中实现的优点。标绘图600示出了由数字麦克风组件响应于20khz传入声压而生成的未加扰的

数据流的经由matlab模拟的频谱,该20khz传入声压的水平相对于满刻度为

‑

20db。频率刻度是对数的,并且示出了从0hz到1.5mhz的频率。该数字麦克风组件包括采样频率为3mhz的过采样且噪声整形多位adc,以将换能器音频信号转换成经噪声整形的pdm信号。显然,未加扰的数据流的频谱在20khz输入频调(tone)处显示出明显的峰值。由20khz以上的噪声水平稳步上升,也可以明显看出噪声整形多位adc的噪声整形操作。20khz处的频谱峰值的高水平可能会在先前讨论的多麦克风系统500的所述四个数字麦克风组件中的单独数字麦克风组件之间引入先前讨论的交叉调制或干扰问题。

[0047]

标绘图610是与上面的标绘图600相对应的标绘图,但是其中数字加扰电路300处于活动状态以生成数字麦克风组件的经加扰或解相关的数据流输出。用于当前模拟的数字加扰电路基于利用由最大长度不可约9阶多项式h(x)所定义的z域传递函数的乘法加扰算法。显而易见的是,加扰数据流的频谱在整个频率上具有大致恒定的噪声水平,这表明加扰数据流的频谱基本上是白的。因此,消除了在该频率下由输入声压在20khz处生成的先前频谱峰值。因而,数字加扰电路300的操作显然在白化由数据通信接口传递的结构化数据流的频谱方面非常有效。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1