域控制器时间同步结构的制作方法

1.本实用新型涉及汽车领域,特别是涉及一种用于域控制器内和外部时间同步的域控制器时间同步结构。

背景技术:

2.目前整车e/e架构由于面临来自不同控制器和传感器的数据交互需求而变得愈加复杂,所需要解决的问题包括:功能复杂性,通信带宽,计算能力,灵活性,可拓展性等。

3.其中域控制器上层应用算法对获取数据的同步尤其敏感,以高级辅助驾驶、自动驾驶系统为例,系统包含环境感知、数据融合、路径规划和应用执行,其中系统正确运行的一个重要问题就是要保证获取的数据精确时间同步,算法的基准是所有的数据都是在同一时间点获取的,否则应用功能无法保证做出正确的预判,可能造成自动驾驶的严重事故。但是由于域控制器内部异构、外部控制器节点以及传感器节点设备时钟晶振及数据传输路径不同,导致系统获取的数据在时间上不能完全同步。急需一种能使域控制器内部异构、外部控制器节点以及传感器节点实现时间同步的域控制器时间同步结构。

技术实现要素:

4.本实用新型要解决的技术问题是提供一种能使域控制器内部异构、外部控制器节点以及传感器节点实现时间同步的域控制器时间同步结构。

5.为解决上述技术问题,本实用新型提供一种域控制器时间同步结构,包括:

6.通信模块,其连接外部主时钟源(外部控制器节点)、mcu和第一soc模块,其用于将外部主时钟源的时间传输至mcu和第一soc模块;

7.第一时钟电路,其连接通信模块、mcu和第一soc模块,其用于提供基准时间校准通信模块、mcu和第一soc模块时钟;

8.第二时钟电路,其连接mcu和第二soc模块,其用于提供基准时间校准第二soc模块时钟;

9.mcu,其连接外部传感器节点、第一soc模块和第二soc模块;

10.第三时钟电路,其连接mcu,其用于提供基准时间校准外部传感器节点时钟。

11.可选择的,进一步改进所述的域控制器时间同步结构,所述第一时钟电路、第二时钟电路和/或第三时钟电路集成于mcu。

12.可选择的,进一步改进所述的域控制器时间同步结构:所述第一时钟电路集成于第一soc模块,第二时钟电路集成于第二soc模块,第三时钟电路集成于mcu。

13.可选择的,进一步改进所述的域控制器时间同步结构,所述mcu通过以太网接口连接通信模块。

14.可选择的,进一步改进所述的域控制器时间同步结构,所述第一soc模块具有以太网接口。

15.可选择的,进一步改进所述的域控制器时间同步结构,所述mcu通过gpio引脚和

spi引脚连接第二第soc模块。

16.可选择的,进一步改进所述的域控制器时间同步结构,所述通信模块是以太网交换机。

17.可选择的,进一步改进所述的域控制器时间同步结构,所述mcu通过can总线接口和外部传感器节点连接。

18.可选择的,进一步改进所述的域控制器时间同步结构,所述mcu具有太网接口、gpio接口、spi接口和can接口。

19.可选择的,进一步改进所述的域控制器时间同步结构,所述外部传感器节点包括摄像头和雷达。

20.基于本实用新型提供的域控制器各模块之间的结构关系,说明本实用新型的工作过程及原理如下:

21.一、第一同步路径,域控制器和外部主时钟源控制器的时间同步的路径:外部主时钟源-通信模块-第一时钟电路-mcu和第一soc模块,通过该路径实现时间同步。

22.该同步路径通过通信模块将外部主时钟源传输至mcu,第一时钟电路提供基准时间校准,mcu和第一soc模块根据提供第一时钟电路的基准时间校准各自的时钟时间,实现时间同步。其中mcu和soc分别运行gptp协议,该协议是基于数据包的时间同步协议。数据传输和时间同步使用同一网络,它描述了如何在基于数据包网络(比如以太网)上分配同步时间(相位、频率和绝对时间)的机制,时钟精度达到亚微秒级。

23.二、第二同步路径,域控制器片内异构多核的时间同步:mcu和第二soc模块之间的时间同步。

24.mcu和第二soc模块的时间同步路径需要mcu的gpio引脚和能携带mcu时间戳信息的通讯接口引脚(例如spi通信引脚等),以mcu为主时钟master,第二时钟电路提供基准时间校准同步第二soc模块时钟。

25.由于本实用新型将mcu通过gpio引脚和spi引脚连接第二soc模块形成第二同步路径,所以mcu和第二soc模块能够实现时间同步,示例性的同步机制如下:

26.(1)mcu记录当前的时间tx,并通过gpio通知第二soc模块(mcu和第二soc模块之间的时间同步通过使用gpio引脚进行中断通知,以保证mcu和第二soc模块的时间基准点尽可能相近)。

27.(2)第二soc模块响应gpio引脚的请求,并记录第二soc模块当前的时间t1。

28.(3)mcu通过spi引脚将记录的当前时间t1发送给第二soc模块(gpio中断请求和spi传送时间戳信息尽可能短,以保证同步的精度)。

29.(4)第二soc模块接收到tx时刻的第二soc模块系统时间为t2,立即更新第二soc模块的系统时间

30.三、第三同步路径,域控制器(内部时钟)和外部传感器节点(设备/控制)的时间同步。

31.系统外部传感器(camera/radar)通过私有can接口连接到域控制器的mcu,在mcu的内部完成数据融合的处理后将数据传给决策模块。mcu和外部传感器的时间同步方案需要mcu节点通过私有can发送同步帧到外部传感器节点,以mcu为主时钟master,第三时钟电路提供基准时间校准,同步外部传感器节点。mcu和外部传感器的时间同步机制如下:

32.(1)mcu发送全局时间can同步报文。

33.(2)外部传感器接受节点采用最高优先级处理全局时间can同步报文,并记录外部节点当前的时间t1

34.(3)mcu在发送全局时间同步报文时填写计时器,以一定的周期发送同步报文,时间同步报文中携带时间戳信息。

35.(4)接收节点根据全局时间戳并加载计算本地时间戳,更新接受节点的系统时间。

36.本实用新型至少能实现以下有益效果:

37.1、本实用新型通过第一同步路径实现了域控制器和外部时钟源的时间同步。

38.2、本实用新型通过第二同步路径实现了域控制器片内异构多核的时间同步。

39.3、本实用新型通过第三同步路径实现了域控制器和外部传感器节点(设备/控制)的时间同步。

40.4、本实用新型通过上述三个同步路径,将域控制器内部异构、外部控制器节点以及传感器节点通过硬件结构连接在一起,使域控制器内部异构、外部控制器节点以及传感器节点运行基于同一个时间基点,进而实现时间同步,避免时间偏差。

附图说明

41.本实用新型附图旨在示出根据本实用新型的特定示例性实施例中所使用的方法、结构和/或材料的一般特性,对说明书中的描述进行补充。然而,本实用新型附图是未按比例绘制的示意图,因而可能未能够准确反映任何所给出的实施例的精确结构或性能特点,本实用新型附图不应当被解释为限定或限制由根据本实用新型的示例性实施例所涵盖的数值或属性的范围。下面结合附图与具体实施方式对本实用新型作进一步详细的说明:

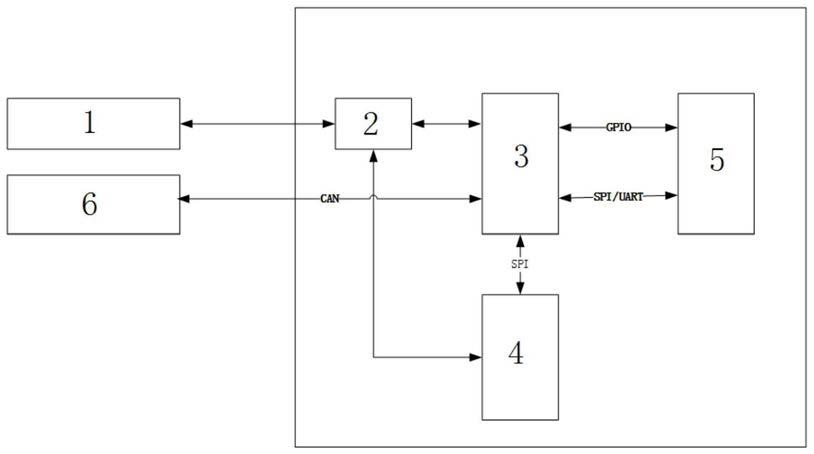

42.图1是本实用新型结构示意图。

43.附图标记说明

44.外部主时钟源1

45.通信模块2

46.mcu 3

47.第一soc模块4

48.第二soc模块5

49.外部传感器节点6

具体实施方式

50.以下通过特定的具体实施例说明本实用新型的实施方式,本领域技术人员可由本说明书所公开的内容充分地了解本实用新型的其他优点与技术效果。本实用新型还可以通过不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点加以应用,在没有背离实用新型总的设计思路下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。本实用新型下述示例性实施例可以多种不同的形式来实施,并且不应当被解释为只限于这里所阐述的具体实施例。应当理解的是,提供这些实施例是为了使得本实用新型的公开彻底且完整,并且将这些示例性具体实施例的技术方案充分传达给本领域技术人员。

51.应当理解的是,当元件被称作“连接”或“结合”到另一元件时,该元件可以直接连接或结合到另一元件,或者可以存在中间元件。不同的是,当元件被称作“直接连接”或“直接结合”到另一元件时,不存在中间元件。在全部附图中,相同的附图标记始终表示相同的元件。此外,还应当理解的是,尽管在这里可以使用术语“第一”、“第二”等来描述不同的元件、组件、区域、层和/或部分,但是这些元件、组件、区域、层和/或部分不应当受这些术语的限制。这些术语仅是用来将一个元件、组件、区域、层或部分与另一个元件、组件、区域、层或部分区分开来。因此,在不脱离根据本实用新型的示例性实施例的教导的情况下,以下所讨论的第一元件、组件、区域、层或部分也可以被称作第二元件、组件、区域、层或部分。

52.第一实施例;

53.参考图1所示,本实用新型提供一种域控制器时间同步结构,包括:

54.通信模块2,其连接外部主时钟源1、mcu 3和第一soc模块4,其用于将外部主时钟源1的时间传输至mcu 3和第一soc模块4;

55.第一时钟电路(图中未显示),其连接通信模块2、mcu 3和第一soc模块4,其用于提供基准时间校准通信模块2、mcu 3和第一soc模块4时钟;

56.第二时钟电路(图中未显示),其连接mcu 3和第二soc模块5,其用于提供基准时间校准第二soc模块5时钟;

57.mcu,其连接外部传感器节点6、第一soc模块4和第二soc模块5;

58.第三时钟电路(图中未显示),其连接mcu 3,其用于提供基准时间校准外部传感器节点6时钟。

59.第二实施例;

60.继续参考图1所示,本实用新型提供一种域控制器时间同步结构,包括:

61.通信模块2,其连接外部主时钟源1、mcu 3和第一soc模块4,其用于将外部主时钟源1的时间传输至mcu 3和第一soc模块4;

62.第一时钟电路(图中未显示),其连接通信模块2、mcu 3和第一soc模块4,其用于提供基准时间校准通信模块2、mcu 3和第一soc模块4时钟;

63.第二时钟电路(图中未显示),其连接mcu 3和第二soc模块5,其用于提供基准时间校准第二soc模块5时钟;

64.mcu,其连接外部传感器节点6、第一soc模块4和第二soc模块5;

65.第三时钟电路(图中未显示),其连接mcu 3,其用于提供基准时间校准外部传感器节点6时钟。

66.其中,所述第一时钟电路、第二时钟电路和第三时钟电路集成于mcu。

67.第三实施例;

68.继续参考图1所示,本实用新型提供一种域控制器时间同步结构,包括:

69.通信模块2,其连接外部主时钟源1、mcu 3和第一soc模块4,其用于将外部主时钟源1的时间传输至mcu 3和第一soc模块4;

70.第一时钟电路(图中未显示),其连接通信模块2、mcu 3和第一soc模块4,其用于提供基准时间校准通信模块2、mcu 3和第一soc模块4时钟;

71.第二时钟电路(图中未显示),其连接mcu 3和第二soc模块5,其用于提供基准时间校准第二soc模块5时钟;

72.mcu,其连接外部传感器节点6、第一soc模块4和第二soc模块5;

73.第三时钟电路(图中未显示),其连接mcu 3,其用于提供基准时间校准外部传感器节点6时钟;

74.其中,所述第一时钟电路、第二时钟电路和/或第三时钟电路集成于mcu;

75.或,所述第一时钟电路集成于第一soc模块,第二时钟电路集成于第二soc模块,第三时钟电路集成于mcu。

76.进一步改进上述第一~第三实施例,所述mcu通过以太网接口连接通信模块,所述第一soc模块具有以太网接口,所述mcu通过spi引脚连接第一第soc模块,所述mcu通过gpio引脚和spi引脚连接第二第soc模块,所述mcu通过can总线接口和外部传感器节点连接,所述通信模块是以太网交换机,所述mcu具有太网接口、gpio接口、spi接口和can接口,所述外部传感器节点包括但不限于摄像头和雷达。

77.除非另有定义,否则这里所使用的全部术语(包括技术术语和科学术语)都具有与本实用新型所属领域的普通技术人员通常理解的意思相同的意思。还将理解的是,除非这里明确定义,否则诸如在通用字典中定义的术语这类术语应当被解释为具有与它们在相关领域语境中的意思相一致的意思,而不以理想的或过于正式的含义加以解释。

78.以上通过具体实施方式和实施例对本实用新型进行了详细的说明,但这些并非构成对本实用新型的限制。在不脱离本实用新型原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1