封装结构及其制造方法与流程

1.本发明涉及一种封装结构及其制造方法,尤其涉及一种具有多个有源芯片的封装结构及其制造方法。

背景技术:

2.近年来,电子设备对于人类的生活越来越重要。为了加速各种功能的集成,可以将多个有源芯片集成在一个封装结构。因此,如何使具有多个有源芯片的封装结构的制造良率或质量可以提升,或可以使多个有源芯片的封装结构的制造成本可以降低,已成为迫在眉睫的问题。

技术实现要素:

3.本发明提供一种封装结构,其具有更好的质量。

4.本发明提供一种封装结构的制造方法,其具有更好的良率或较低的成本。

5.本发明的封装结构包括桥接芯片、硅穿孔芯片、第一模封体、第一有源芯片、第二有源芯片、第二模封体以及重布线路结构。第一模封体覆盖硅穿孔芯片及桥接芯片。第一有源芯片电连接于桥接芯片及硅穿孔芯片。第二有源芯片电连接于桥接芯片。第二模封体覆盖第一有源芯片及第二有源芯片。重布线路结构电连接于硅穿孔芯片。硅穿孔芯片位在第一有源芯片及重布线路结构之间。

6.本发明的封装结构的制造方法包括以下步骤。提供硅穿孔芯片及桥接芯片。形成覆盖硅穿孔芯片及桥接芯片的第一模封体。形成电连接于硅穿孔芯片的重布线路结构。配置电连接于桥接芯片及硅穿孔芯片的第一有源芯片。配置电连接于桥接芯片的第二有源芯片。形成覆盖第一有源芯片及第二有源芯片的第二模封体。在形成重布线路结构的步骤及配置第一有源芯片的步骤之后,硅穿孔芯片位在第一有源芯片及重布线路结构之间。

7.基于上述,本发明的封装结构可以集成(integrated)多个有源芯片。多个有源芯片之间可以通过桥接芯片彼此电连接,且有源芯片可以通过硅穿孔芯片与重布线路结构电连接。如此一来,可以提升封装结构的质量。并且,在封装结构的制造方法上,可以先将桥接芯片与硅穿孔芯片以第一模封体,再配置电连接至桥接芯片或硅穿孔芯片的有源芯片。如此一来,封装结构的制造良率可以提升,或可以使封装结构的制造成本降低。

附图说明

8.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

9.图1a至图1h为依照本发明的第一实施例的一种封装结构的部分制造方法的部分剖视示意图;

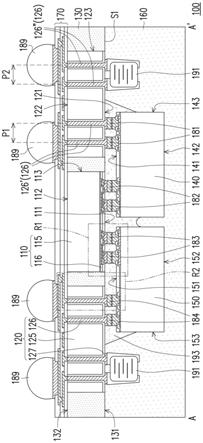

10.图1i为依照本发明的第一实施例的一种封装结构的部分剖视示意图;

11.图1j为依照本发明的第一实施例的一种封装结构的部分下视示意图;

12.图1k至图1l为依照本发明的第一实施例的一种封装结构的部分剖视放大示意图;

13.图2a为依照本发明的第二实施例的一种封装结构的部分剖视示意图;

14.图2b为依照本发明的第二实施例的一种封装结构的部分下视示意图;

15.图3为依照本发明的第三实施例的一种封装结构的部分剖视示意图;

16.图4为依照本发明的第四实施例的一种封装结构的部分剖视示意图。

17.附图标号说明

18.100、200、300、400:封装结构;

19.110:桥接芯片;

20.111:桥接连接面;

21.112:桥接背面;

22.113:桥接侧面;

23.115:硅衬底;

24.116:内互连结构;

25.116a:导电层;

26.116b:绝缘层;

27.120、320:硅穿孔芯片;

28.121:第一连接面;

29.122:第二连接面;

30.123:连接侧面;

31.125:硅衬底;

32.126:穿硅导体;

33.126a:导电芯层;

34.126b:绝缘壳层;

35.126’:第一穿硅导体;

36.126”:第二穿硅导体;

37.127:连接垫;

38.127a:导电连接层;

39.328:连接线路;

40.139:第一模封材料;

41.130:第一模封体;

42.131:第一模封表面;

43.132:第二模封表面;

44.140:第一有源芯片;

45.141:第一有源面;

46.142:第一背面;

47.143:第一侧面;

48.150:第二有源芯片;

49.151:第二有源面;

50.152:第二背面;

51.153:第二侧面;

52.160、460:第二模封体;

53.170:重布线路结构;

54.175:图案化介电层;

55.176、176a:图案化导电层;

56.181:第一导电连接件;

57.182:第二导电连接件;

58.183:第三导电连接件;

59.184:第四导电连接件;

60.189:导电端子;

61.191:无源组件;

62.193:填充层;

63.s1、s2:界面;

64.493:散热件;

65.10:第一载板;

66.20:第二载板;

67.11、21:离型层;

68.p1:第一间距;

69.p2:第一间距;

70.r1、r2:区域。

具体实施方式

71.本文所使用的方向用语(例如,上、下、右、左、前、后、顶部、底部)仅作为参看所绘附图使用且不意欲暗示绝对定向。另外,为求清楚表示,在附图中可能省略示出了部分的膜层或构件。

72.除非另有明确说明,否则本文所述任何方法绝不意欲被解释为要求按特定顺序执行其步骤。

73.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。然而,本发明亦可以各种不同的形式体现,而不应限于本文中所述的实施例。附图中的层或区域的厚度、尺寸或大小会为了清楚起见而放大。只要有可能,相同或相似的元件符号在附图和描述中用来表示相同或相似部分。

74.图1a至图1h是依照本发明的第一实施例的一种封装结构的部分制造方法的部分剖视示意图。图1i是依照本发明的第一实施例的一种封装结构的部分剖视示意图。图1j是依照本发明的第一实施例的一种封装结构的部分下视示意图。图1k至图1l是依照本发明的第一实施例的一种封装结构的部分剖视放大示意图。图1i例如是对应于图1j中a-a’剖在线的剖视示意图。图1k例如是对应于图1i中区域r1的放大示意图。图1l例如是对应于图1i中区域r2的放大示意图。另外,为求清楚表示,于附图中可能省略示出了部分的膜层或构件。举例而言,在图1j中,仅示例性地示出了部分的桥接芯片110、硅穿孔芯片120、第一有源芯片140、第二有源芯片150、第一导电连接件181、第二导电连接件182、第三导电连接件183、

第四导电连接件184、导电端子189或无源组件191。

75.请参照图1a,提供硅穿孔芯片120及桥接芯片110。举例而言,可以将硅穿孔芯片120及桥接芯片110配置在第一载板10上。第一载板10可以由玻璃、晶圆基板、金属或其他适宜的材料所制成,只要前述的材料能够于后续的工艺中,承载形成在其上的结构或构件。另外,本发明对于配置在第一载板10上的硅穿孔芯片120或桥接芯片110的个数并不加以限制。以图1a为例,配置在第一载板10上的硅穿孔芯片120的个数例如为四个,且配置在第一载板10上的桥接芯片110的个数例如为二个。

76.在本实施例中,第一载板10上可以具有离型层11。离型层11可以为光热转换(light to heat conversion,lthc)黏着层,但本发明不限于此。

77.在本实施例中,硅穿孔芯片120可以包括硅衬底125、穿硅导体126以及连接垫127。穿硅导体126可以贯穿硅衬底125,且穿硅导体126可以电连接于对应的连接垫127。连接垫127位在硅衬底125上。硅穿孔芯片120可以是以其连接垫127面向第一载板10的方式而被配置在第一载板10上。通过硅穿孔芯片120,可以使位在硅穿孔芯片120相对两端的电子组件可以通过硅穿孔芯片120的穿硅导体126而电连接。

78.在本实施例中,被配置在第一载板10上的硅穿孔芯片120可以为已知合格芯片(known good die,kgd)。举例而言,在将硅穿孔芯片120配置在第一载板10上之前,可以对硅穿孔芯片120进行电性、外观或其他适宜的检查或测试步骤。如此一来,可以确认被配置在第一载板10上的硅穿孔芯片120具有良好的功能,而可以提升封装结构100(标示在图1i或图1j)的良率。

79.在本实施例中,桥接芯片110可以包括硅衬底115以及内互连结构(interconnector structure)116。内互连结构116位在硅衬底115上。桥接芯片110可以是以其内互连结构116面向第一载板10的方式而被配置在第一载板10上。

80.在本实施例中,内互连结构116例如为通过一般半导体制造中的后半布线工序(back-end of line,beol)所形成的线路。因此,可以依据后续电连接的需求,将内互连结构116的线路进行调整或设计,以使桥接芯片110在应用上可以具有较多的弹性,且可以使线路或电性接点间具有更好的细节距(fine pitch)。

81.在本实施例中,被配置在第一载板10上的桥接芯片110可以为已知合格芯片(known good die;kgd)。举例而言,在将桥接芯片110配置在第一载板10上之前,可以对桥接芯片110进行电性、外观或其他适宜的检查或测试步骤。如此一来,可以确认被配置在第一载板10上的桥接芯片110具有良好的功能,而可以提升封装结构100(标示在图1i或图1j)的良率。

82.在一实施例中,硅穿孔芯片120或桥接芯片110不具有有源器件(active device)。举例来说,硅衬底115上的膜层可以不会构成晶体管(transistor)、二极管(diode)、集成电路(integrated circuit)或光电组件(optoelectronic device)。如此一来,桥接芯片110在制作、检查或测试上可以较为简单。在一实施例中,硅穿孔芯片120或桥接芯片110可以为无源芯片(passive die)。

83.请参照图1b至图1c,形成覆盖硅穿孔芯片120及桥接芯片110的第一模封体130。

84.请参照图1b,举例而言,可以形成覆盖硅穿孔芯片120及桥接芯片110的第一模封材料139。在一实施例中,第一模封材料139例如是通过模塑工艺(molding process)或其他

适宜的方法将熔融的模塑化合物(molding compound)形成在第一载板10上。然后,使熔融的模塑化合物冷却并且固化。在一实施例中,硅穿孔芯片120及桥接芯片110并不会被暴露于第一模封材料139之外,但本发明不限于此。

85.请参照图1c,举例而言,在形成第一模封材料139之后,可以进行第一减薄工艺,以移除部分的第一模封材料139,以形成侧向覆盖硅穿孔芯片120及桥接芯片110的第一模封体130,且暴露出硅穿孔芯片120及桥接芯片110。

86.在本实施例中,第一减薄工艺例如包括化学机械研磨(chemical mechanical polishing,cmp)、机械研磨(mechanical grinding)、蚀刻(etching)或其他适宜的工艺,但本发明不限于此。

87.在本实施例中,在经由上述的第一减薄工艺之后,硅穿孔芯片120的第二连接面122、桥接芯片110的桥接背面112及第一模封材料139的第二模封表面132可以基本上共面(coplaner)。

88.在一实施例中,在上述的第一减薄工艺中,硅穿孔芯片120的一部份(如:硅衬底125远离第一载板10的一部分或穿硅导体126远离第一载板10的一部分)或桥接芯片110的一部份(如:硅衬底115远离第一载板10的一部分)可能可以被些微地移除。

89.请参照图1d,形成电连接于硅穿孔芯片120的重布线路结构170。举例而言,于形成第一模封体130之后,可以至少于硅穿孔芯片120上形成重布线路结构170,且重布线路结构170可以电连接于硅穿孔芯片120的穿硅导体126。

90.在本实施例中,重布线路结构170可以被形成于硅穿孔芯片120、桥接芯片110以及第一模封体130上。举例而言,可以在硅穿孔芯片120、桥接芯片110以及第一模封体130上形成图案化介电层175。图案化介电层175可以具有多个介电层开口,以暴露出部分的穿硅导体126。然后,可以通过沉积工艺和/或电镀工艺等其他适宜的工艺在图案化介电层175上形成导电物质。并且,导电物质可以进一步填入图案化介电层175的介电层开口内,以形成具有导电性质的导通孔(conductive via)。随后,可以通过例如微影及蚀刻工艺以对覆盖于图案化介电层175上的导电物质进行图案化,以形成图案化导电层176。通过相同或相似于上述的步骤,可以形成至少一个图案化介电层175或至少一个图案化导电层176,以构成重布线路结构170。

91.请参照图1e至图1f,将硅穿孔芯片120、桥接芯片110、第一模封体130及重布线路结构170放置在第二载板20上,且移除第一载板10。

92.在一实施例中,可以先将在第一载板10及位在第一载板10上的构件(如:图1d所示出的结构)上配置第二载板20,以使第一载板10上的构件(如:硅穿孔芯片120、桥接芯片110、第一模封体130及重布线路结构170)被夹在第二载板20与第一载板10之间。然后,可以将第一载板10、第二载板20以及被夹在第二载板20与第一载板10之间的构件上下翻转(flipupside down)。然后,再将第一载板10移除。值得注意的是,上述的方式仅为示例性的举例,于本发明并不加以限制。

93.在本实施例中,第二载板20上可以具有离型层21。离型层21可以为光热转换黏着层,但本发明不限于此。

94.在本实施例中,在移除第一载板10之后,硅穿孔芯片120的连接垫127及桥接芯片110的内互连结构116可以被暴露出。

95.请参照图1f,在移除第一载板10之后,配置第一有源芯片140或第二有源芯片150。第一有源芯片140或第二有源芯片150电连接于桥接芯片110,且第一有源芯片140电连接于硅穿孔芯片120。值得注意的是,本发明对于第一有源芯片140或第二有源芯片150配置的数量或顺序并不加以限制。

96.在本实施例中,在经由前述的第一减薄工艺之后,桥接芯片110及硅穿孔芯片120的厚度基本上相同。并且,桥接芯片110及硅穿孔芯片120可以包括硬质的衬底(如:桥接芯片110包括硅衬底115,且硅穿孔芯片120包括硅衬底125)。另外,桥接芯片110及硅穿孔芯片120被第一模封体130至少侧向覆盖且固定。如此一来,在将第一有源芯片140或第二有源芯片150配置在桥接芯片110或硅穿孔芯片120上时,可以降低侧向的位移(shift)或提升垂直方向的接合力,而可以提升封装结构100的制造良率或质量。在一实施例中,第一模封体130可以完全覆盖桥接芯片110的桥接侧面113及硅穿孔芯片120的连接侧面123。

97.在一实施例中,第一有源芯片140或第二有源芯片150可以是电力管理芯片(power management integrated circuit,pmic)、微机电系统芯片(micro-electro-mechanical-system,mems)、特殊应用集成电路芯片(application-specific integrated circuit,asic)、动态随机存取内存芯片(dynamic random access memory,dram)、静态随机存取内存芯片(static random access memory,sram)、高带宽内存(high bandwidth memory,hbm)芯片、系统芯片(system on chip,soc)或其他类似的高效能运算(high performance computing,hpc)芯片,但本发明不限于此。

98.在一实施例中,第一有源芯片140与第二有源芯片150之间可以是同质的(homogeneous)芯片也可以是异质的(heterogeneous)芯片,于本发明并不加以限制。

99.在本实施例中,更可以在移除第一载板10之后,配置无源组件191。无源组件191可以电连接于硅穿孔芯片120。值得注意的是,本发明对于第一有源芯片140、第二有源芯片150或无源组件191配置的数量或顺序并不加以限制。在一实施例中,无源组件191例如是积层陶瓷电容器(multi-layer ceramic capacitor,mlcc),但本发明不限于此。

100.请参照图1g,形成覆盖第一有源芯片140及第二有源芯片150的第二模封体160。第二模封体160的材质或形成方式相同或相似于第一模封体130,故于此不加以重复。

101.在本实施例中,第一有源芯片140及第二有源芯片150并不会被暴露于第二模封体160之外,但本发明不限于此。

102.在本实施例中,第二模封体160可以更覆盖无源组件191,且无源组件191并不会被暴露于第二模封体160之外,但本发明不限于此。

103.请参照图1g至图1h,于形成第二模封体160之后,可以移除第二载板20。并且,可以在移除第二载板20之后,形成多个导电端子189。导电端子189可以电连接于重布线路结构170。

104.导电端子189可以是导电柱(conductive pillar)、焊球(solder ball)、导电凸块(conductive bump)或具有其他形式或形状的导电端子189。导电端子189可以经由电镀、沉积、置球(ball placement)、回焊(reflow)和/或其他适宜的工艺来形成。

105.请参照图1h至图1i,在本实施例中,可以经由单一化工艺(singulation process),以构成多个封装结构100。单一化工艺例如可以包括切割工艺(dicing process/cutting process),以切穿第一模封体130、第二模封体160和/或重布线路结构170。

106.值得注意的是,在进行单一化工艺之后,相似的组件符号将用于单一化后的组件。举例而言,桥接芯片110(如图1h所示)于单一化后可以为桥接芯片110(如图1i所示),硅穿孔芯片120(如图1h所示)于单一化后可以为硅穿孔芯片120(如图1i所示),第一模封体130(如图1h所示)于单一化后可以为第一模封体130(如图1i所示),第一有源芯片140(如图1h所示)于单一化后可以为第一有源芯片140(如图1i所示),第二有源芯片150(如图1h所示)于单一化后可以为第二有源芯片150(如图1i所示),第二模封体160(如图1h所示)于单一化后可以为第二模封体160(如图1i所示),重布线路结构170(如图1h所示)于单一化后可以为重布线路结构170(如图1i所示),诸如此类。其他单一化后的组件将依循上述相同的组件符号规则,于此不加以重复或特别示出。

107.值得注意的是,本发明并未限定配置多个导电端子189(若有)以及单一化工艺(若有)的顺序。

108.经过上述步骤后即可大致上完成本实施例的封装结构100的制作。

109.请参照图1i至图1l,封装结构100包括桥接芯片110、硅穿孔芯片120、第一模封体130、第一有源芯片140、第二有源芯片150、第二模封体160以及重布线路结构170。第一模封体130覆盖多个硅穿孔芯片120及桥接芯片110。第一有源芯片140电连接于桥接芯片110及硅穿孔芯片120。第二有源芯片150电连接于桥接芯片110。第二模封体160覆盖第一有源芯片140及第二有源芯片150。重布线路结构170电连接于硅穿孔芯片120,其中硅穿孔芯片120位在第一有源芯片140及重布线路结构170之间。

110.在本实施例中,第一模封体130的侧壁、第二模封体160的侧壁及重布线路结构170的侧壁基本上可以相切齐。

111.在本实施例中,桥接芯片110具有桥接连接面111、桥接背面112以及桥接侧面113。桥接背面112相对于桥接连接面111。桥接侧面113连接于桥接连接面111及桥接背面112。桥接芯片110包括硅衬底115以及内互连结构116。内互连结构116位在硅衬底115上。

112.在本实施例中,内互连结构116例如为多层的内互连结构。举例而言,内互连结构116包括多个导电层116a以及多个绝缘层116b,且部分的导电层116a1与部分的导电层116a2可以交错(interlace/intercross)。如此一来,可以提升内互连结构116在布线的布局利用率(layout utilization),而可以通过桥接芯片110的内互连结构116连接多个芯片或多个芯片的多个接点。

113.在一实施例中,内互连结构116远离硅衬底115的部分表面(如:内互连结构116最远离硅衬底115的表面)可以构成桥接连接面111,但本发明不限于此。

114.在一实施例中,硅衬底115远离内互连结构116的部分表面(如:硅衬底115最远离内互连结构116的表面)可以构成桥接背面112,但本发明不限于此。

115.在本实施例中,硅穿孔芯片120具有第一连接面121、第二连接面122以及连接侧面123。第二连接面122相对于第一连接面121。连接侧面123连接于第一连接面121及第二连接面122。硅穿孔芯片120可以包括硅衬底125、穿硅导体126以及连接垫127。穿硅导体126贯穿硅衬底125。连接垫127位在硅衬底125上。

116.在本实施例中,穿硅导体126包括导电芯层126a及侧向包覆导电芯层126a的绝缘壳层126b。硅衬底125的部分表面(如:硅衬底125最远离连接垫127的表面)、导电芯层126a的部分表面以及绝缘壳层126b的部分表面基本上共面(coplaner)且构成第二连接面122。

117.在一实施例中,硅衬底125的部分表面(如:硅衬底125具有连接垫127于其上的部分表面)或连接垫127的部分表面可以构成第一连接面121,但本发明不限于此。

118.在本实施例中,连接垫127可以包括导电连接层127a。导电芯层126a与导电连接层127a可以为相同的膜层。

119.在本实施例中,第一有源芯片140具有第一有源面141、第一背面142以及第一侧面143。第一背面142相对于第一有源面141。第一侧面143连接于第一有源面141及第一背面142。第一有源芯片140的第一有源面141面向硅穿孔芯片120的第一连接面121,且第一有源面141与第一连接面121部分重迭。第一有源芯片140的第一有源面141面向桥接芯片110的桥接连接面111,且第一有源面141与桥接连接面111部分重迭。

120.在本实施例中,第一有源芯片140的第一有源面141与硅穿孔芯片120的第一连接面121之间可以具有第一导电连接件181。第一有源芯片140与硅穿孔芯片120可以通过第一导电连接件181而彼此电连接。

121.在本实施例中,第一有源芯片140的第一有源面141与桥接芯片110的桥接连接面111之间可以具有第二导电连接件182。第一有源芯片140与桥接芯片110可以通过第二导电连接件182而彼此电连接。

122.在本实施例中,第二有源芯片150具有第二有源面151、第二背面152以及第二侧面153。第二背面152相对于第二有源面151。第二侧面153连接于第二有源面151及第二背面152。第二有源芯片150的第二有源面151面向桥接芯片110的桥接连接面111,且第二有源面151与桥接连接面111部分重迭。

123.在本实施例中,第二有源芯片150的第二有源面151与桥接芯片110的桥接连接面111之间可以具有第三导电连接件183。第二有源芯片150与桥接芯片110可以通过第三导电连接件183而彼此电连接。

124.在本实施例中,第二有源芯片150可以电连接于另一硅穿孔芯片120,但本发明不限于此。举例而言,第二有源芯片150的第二有源面151与另一硅穿孔芯片120的第一连接面121之间可以具有第四导电连接件184。第二有源芯片150与另一硅穿孔芯片120的硅穿孔芯片120可以通过第四导电连接件184而彼此电连接。

125.在一实施例中,第一导电连接件181、第二导电连接件182、第三导电连接件183或第四导电连接件184可以是焊球(solder ball)或具有其他形式或形状的导电连接件,于本发明并不加以限制。

126.在本实施例中,第一模封体130可以覆盖硅穿孔芯片120的连接侧面123以及桥接芯片110的桥接侧面113。第一模封体130具有第一模封表面131及第二模封表面132。第二模封表面132相对于第一模封表面131。

127.在本实施例中,硅穿孔芯片120的第二连接面122、桥接芯片110的桥接背面112及第一模封体130的第二模封表面132基本上共面(coplaner)。

128.在一实施例中,第一模封体130可以是均质材料(homogeneous material),且前述的均质材料无法再通过机械方法(如:破碎、剪、切、锯、磨等方式)将组件拆离成不同的单一材料。换句话说,在第一模封体130内可以不具有因不同材质或不同工艺所形成的界面(interface)。

129.在本实施例中,第二模封体160可以覆盖第一有源芯片140的第一侧面143或第一

背面142,且第二模封体160可以覆盖第二有源芯片150的第二侧面153或第二背面152。

130.在一实施例中,第二模封体160可以是均质材料。换句话说,在第二模封体160内可以不具有因不同材质或不同工艺所形成的界面。

131.在本实施例中,第一模封体130的第一模封表面131面向第二模封体160,且第一模封体130的第一模封表面131与第二模封体160物理性地接触(physically contact)。

132.在一实施例中,由于第一模封体130与第二模封体160是在不同的步骤中所形成的,因此,第一模封体130与第二模封体160之间可能具有一界面s1。

133.在本实施例中,重布线路结构170至少位在硅穿孔芯片120的第二连接面122上。举例而言,重布线路结构170可以位在硅穿孔芯片120的第二连接面122、桥接芯片110的桥接背面112以及第一模封体130的第二模封表面132上。重布线路结构170可以包括图案化介电层175以及图案化导电层176,且部分的图案化介电层175可以贯穿图案化导电层176。

134.在本实施例中,最接近硅穿孔芯片120的图案化导电层176a(即,多个图案化导电层176的其中之一)可以与硅穿孔芯片120的穿硅导体126的导电芯层126a相接触。在一实施例中,由于前述的图案化导电层176a与导电芯层126a是在不同的步骤中所形成的,因此,前述的图案化导电层176与导电芯层126a之间可以具有一界面s2。

135.在本实施例中,封装结构100可以更包括无源组件191,且第二模封体160可以更覆盖无源组件191。无源组件191可以电连接于硅穿孔芯片120中对应的穿硅导体126。举例而言,硅穿孔芯片120的穿硅导体126可以包括多个第一穿硅导体126’以及多个第二穿硅导体126”。第一穿硅导体126’可以重迭且电连接于第一有源芯片140或第二有源芯片150。第二穿硅导体126”可以重迭且电连接于无源组件191。

136.在本实施例中,多个第一穿硅导体126’之间具有第一间距p1,多个第二穿硅导体126”之间具有第二间距p2,且第二间距p2大于或等于第一间距p1。

137.在本实施例中,封装结构100可以更包括填充层193。填充层193可以位在第一有源芯片140与硅穿孔芯片120、第一有源芯片140与桥接芯片110之间以及第二有源芯片150与桥接芯片110之间。填充层193例如是毛细填充胶(capillary underfill,cuf)或其他适宜的填充材料,于本发明并不加以限制。

138.在本实施例中,封装结构100可以通过桥接芯片110的内互连结构116以将至少两个有源芯片(如:第一有源芯片140或第二有源芯片150)电连接。并且,内互连结构116藉可以通过一般半导体制造中的后段工艺线路工艺所形成。因此,相较于一般常用的电路板,可以使桥接芯片110的内互连结构116内的线路或电性接点间的节距(pitch)可以与其所连接的有源芯片(如:第一有源芯片140或第二有源芯片150)相对应,且可以使桥接芯片110的内互连结构116内的线路或电性接点具有更好的细节距(fine pitch)。

139.在本实施例中,封装结构100的有源芯片(如:第一有源芯片140或第二有源芯片150)可以通过硅穿孔芯片120以与外界的电子组件电连接。并且,由于硅穿孔芯片120内的穿硅导体126基本上为垂直的导通路径。因此,通过硅穿孔芯片120内的穿硅导体126可以降低电子讯号传递的路径或时间,而可以提升电子讯号的传输质量。

140.一般而言,有源芯片(如:第一有源芯片140或第二有源芯片150)的价值或价格高于不具有有源器件的芯片(如:桥接芯片110或硅穿孔芯片120)。因此,在本实施例中,封装结构100的制造方法是先将已知合格的桥接芯片110及已知合格的硅穿孔芯片120以第一模

封体130包覆后,再配置电连接至桥接芯片110或硅穿孔芯片120的有源芯片(如:第一有源芯片140或第二有源芯片150)。如此一来,可以使封装结构100的制造良率提升,或可以使封装结构100的制造成本降低。

141.图2a是依照本发明的第二实施例的一种封装结构的部分剖视示意图。图2b是依照本发明的第二实施例的一种封装结构的部分下视示意图。图2a例如是对应于图2b中b-b’剖在线的剖视示意图。

142.在本实施例中,封装结构200的制造方法与封装结构100的制造方法相似,其类似的构件以相同的标号表示,且具有类似的功能、材质或形成方式,并省略描述。

143.请参照图2a及图2b,在本实施例中,封装结构200包括多个桥接芯片110、多个硅穿孔芯片120、第一模封体130、多个第一有源芯片140、第二有源芯片150、第二模封体160以及重布线路结构170。

144.在本实施例中,第一有源芯片140与第二有源芯片150之间可以是异质的芯片,且多个第一有源芯片140之间可以是同质的芯片。举例而言,第一有源芯片140可以是高带宽内存芯片,而第二有源芯片150可以是系统芯片。

145.图3是依照本发明的第三实施例的一种封装结构的部分剖视示意图。

146.在本实施例中,封装结构300的制造方法与封装结构100的制造方法相似,其类似的构件以相同的标号表示,且具有类似的功能、材质或形成方式,并省略描述。

147.在本实施例中,封装结构300包括桥接芯片110、硅穿孔芯片320、第一模封体130、第一有源芯片140、第二有源芯片150、第二模封体160以及重布线路结构170。第二模封体160覆盖第一有源芯片140及第二有源芯片150。第一模封体130覆盖多个硅穿孔芯片320及桥接芯片110。第一有源芯片140电连接于桥接芯片110及硅穿孔芯片320。重布线路结构170电连接于硅穿孔芯片320,其中硅穿孔芯片320位在第一有源芯片140及重布线路结构170之间。

148.在本实施例中,硅穿孔芯片320可以包括硅衬底125、穿硅导体126、连接垫127以及连接线路328。连接线路328位在硅衬底125上。

149.在本实施例中,连接垫127与连接线路328可以通过相同或相似的步骤所形成。也就是说,连接垫127的结构、材质或厚度可以相同或相似于连接线路328的结构、材质或厚度。举例而言,连接垫127的结构、材质或厚度基本上相同于连接线路328的结构、材质或厚度。

150.在本实施例中,连接线路328可以与穿硅导体126物理性地绝缘(physically isolated),但本发明不限于此。

151.在本实施例中,封装结构300可以更包括无源组件191。无源组件191可以通过连接线路328电连接第一有源芯片140或第二有源芯片150。

152.图4是依照本发明的第四实施例的一种封装结构的部分剖视示意图。

153.在本实施例中,封装结构400的制造方法与封装结构100的制造方法相似,其类似的构件以相同的标号表示,且具有类似的功能、材质或形成方式,并省略描述。

154.在本实施例中,封装结构400包括桥接芯片110、硅穿孔芯片120、第一模封体130、第一有源芯片140、第二有源芯片150、第二模封体460以及重布线路结构170。第二模封体460覆盖第一有源芯片140及第二有源芯片150。

155.在本实施例中,第二模封体460可以覆盖第一有源芯片140的第一侧面143及第二有源芯片150的第二侧面153,且第二模封体460可以暴露出第一有源芯片140的第一背面142及第二有源芯片150的第二背面152。

156.在本实施例中,封装结构400可以更包括散热件493。散热件493至少热耦接于第一有源芯片140或第二有源芯片150。

157.举例而言,请参照图1g及图4,于配置第一有源芯片140及第二有源芯片150之后,可以形成覆盖第一有源芯片140及第二有源芯片150的第二模封材料(如:类似于图1g所示出的步骤)。第二模封材料的材质或形成方式相同或相似于第一模封材料139(标示在图1b),故于此不加以重复。然后,在形成前述的第二模封材料之后,可以进行第二减薄工艺,以形成侧向覆盖第一有源芯片140及第二有源芯片150的第二模封体460,且暴露出第一有源芯片140及第二有源芯片150。第二减薄工艺相同或相似于前述的第一减薄工艺,故于此不加以重复。

158.在本实施例中,散热件493可以接触第一有源芯片140的第一背面142及第二有源芯片150的第二背面152,以使散热件493可以热耦接于第一有源芯片140或第二有源芯片150。

159.在一未示出实施例中,散热件493与第一有源芯片140的第一背面142或第二有源芯片150的第二背面152之间可以具有导热界面材料(thermal interface material,tim),以使散热件493可以热耦接于第一有源芯片140或第二有源芯片150。

160.综上所述,本发明的封装结构可以集成多个有源芯片。多个有源芯片之间可以通过桥接芯片彼此电连接,且有源芯片可以通过硅穿孔芯片与重布线路结构电连接。如此一来,可以提升封装结构的质量。并且,在封装结构的制造方法上,可以先将桥接芯片与硅穿孔芯片以第一模封体,再配置电连接至桥接芯片或硅穿孔芯片的有源芯片。如此一来,封装结构的制造良率可以提升,或可以使封装结构的制造成本降低。

161.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1