电子装置的线路的制作方法

[0001]

本发明涉及一种电子装置,尤其涉及一种电子装置的线路。

背景技术:

[0002]

目前一些电子装置,例如显示器,会具有多条线路来传输电信号,以使电子装置能正常运作。然而,上述电子装置的线路在制造过程中因受到工艺因素的影响而难免会有缺陷,进而导致线路出现像是短路等不好的状况,以至于线路的良率不容易再进一步地提升。

技术实现要素:

[0003]

本发明提出一种电子装置的线路,其利用修饰层可帮助修补表面的缺陷。

[0004]

本发明至少一实施例所提供的电子装置的线路形成于基板上,并包括缓冲层、第一导电层与修饰层。缓冲层形成于基板上。第一导电层形成于缓冲层上,其中第一导电层的电阻率小于缓冲层的电阻率。修饰层形成于基板上,并覆盖第一导电层的上表面与第一导电层的侧边,其中修饰层的标准还原电位大于缓冲层与第一导电层其中至少一个的标准还原电位。

[0005]

在本发明至少一实施例中,上述基板的内表面、缓冲层的侧边与第一导电层的下表面形成空腔,其中空腔从第一导电层的侧边沿着基板的内表面而延伸至缓冲层的侧边,而修饰层还从第一导电层的侧边填入于空腔中。

[0006]

在本发明至少一实施例中,上述修饰层的厚度介于10纳米至100纳米之间。

[0007]

在本发明至少一实施例中,上述电子装置的线路还包括绝缘层与第二导电层。绝缘层形成于基板上,并覆盖修饰层。第二导电层形成于绝缘层上,并与修饰层至少部分重叠。

[0008]

在本发明至少一实施例中,上述修饰层的标准还原电位大于缓冲层与第一导电层每一个的标准还原电位,且修饰层还覆盖缓冲层的侧边。

[0009]

在本发明至少一实施例中,上述线路为薄膜晶体管的电极、电容结构的电极或信号线。

[0010]

本发明另一实施例所提供的电子装置的线路形成于基板上,并包括缓冲层、第一导电层与修饰层。缓冲层形成于基板上。第一导电层形成于缓冲层上,其中第一导电层的电阻率小于缓冲层的电阻率。基板的内表面、缓冲层的侧边与第一导电层的下表面形成空腔,而空腔从第一导电层的侧边沿着基板的内表面而延伸至缓冲层的侧边。修饰层形成于基板上,并填入空腔中,其中修饰层的标准还原电位大于缓冲层与第一导电层其中至少一个的标准还原电位。

[0011]

在本发明至少一实施例中,上述修饰层的标准还原电位大于缓冲层的标准还原电位,小于第一导电层的标准还原电位。

[0012]

由于上述修饰层能填满上述空腔,因此修饰层能修补缓冲层与第一导电层之间的表面,以使缓冲层与第一导电层之间的表面变的较为平整,以降低后续工艺所造成的不良

影响,进而提升良率。

附图说明

[0013]

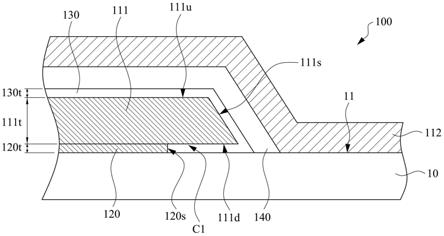

图1是本发明至少一实施例的电子装置的线路的剖面示意图。

[0014]

图2是本发明另一实施例的电子装置的线路的剖面示意图。

[0015]

附图标记如下:

[0016]

10:基板

[0017]

11:内表面

[0018]

100、200:线路

[0019]

111:第一导电层

[0020]

111d:下表面

[0021]

111s、120s:侧边

[0022]

111t、120t、130t:厚度

[0023]

111u:上表面

[0024]

112:第二导电层

[0025]

120;缓冲层

[0026]

130、230:修饰层

[0027]

140:绝缘层

[0028]

c1:空腔

具体实施方式

[0029]

在以下的内文中,为了清楚呈现本案的技术特征,附图中的元件(例如层、膜、基板以及区域等)的尺寸(例如长度、宽度、厚度与深度)会以不等比例的方式放大。因此,下文实施例的说明与解释不受限于附图中的元件所呈现的尺寸与形状,而应涵盖如实际工艺及/或公差所导致的尺寸、形状以及两者的偏差。例如,附图所示的平坦表面可以具有粗糙及/或非线性的特征,而附图所示的锐角可以是圆的。所以,本案附图所呈示的元件主要是用于示意,并非旨在精准地描绘出元件的实际形状,也非用于限制本案的权利要求。

[0030]

其次,本案内容中所出现的“约”、“近似”或“实质上”等这类用字不仅涵盖明确记载的数值与数值范围,而且也涵盖发明所属技术领域中技术人员所能理解的可允许偏差范围,其中此偏差范围可由测量时所产生的误差来决定,而此误差例如是起因于测量系统或工艺条件两者的限制。此外,“约”可表示在上述数值的一个或多个标准偏差内,例如

±

30%、

±

20%、

±

10%或

±

5%内。本案文中所出现的“约”、“近似”或“实质上”等这类用字可依光学性质、蚀刻性质、机械性质或其他性质来选择可以接受的偏差范围或标准偏差,并非单以一个标准偏差来套用以上光学性质、蚀刻性质、机械性质以及其他性质等所有性质。

[0031]

图1是本发明至少一实施例的电子装置的线路的剖面示意图。请参阅图1,线路100可应用于电子装置,其例如是手机、电脑、电脑周边装置或家电用品等,其中此电脑周边装置可以是输入装置、输出装置或输入/输出装置,例如鼠标、键盘、事务机、随身碟、显示器及触控垫。

[0032]

当线路100应用于显示器时,显示器可具有显示面板,而线路100可为显示面板内

的子像素的一部分。举例而言,上述子像素可具有薄膜晶体管,其中薄膜晶体管电性连接多条信号线,其包括扫描线与数据线。线路100可以是薄膜晶体管的电极或信号线。

[0033]

具体而言,线路100可以是薄膜晶体管的栅极、源极与漏极其中至少一个。当线路100为信号线时,线路100可以是显示面板内的扫描线、数据线、读取线、连接线与触控线其中至少一个,其中连接线可为显示区外的信号线。此外,线路100也可以是电容结构的上电极或下电极,其中此电容结构例如是液晶显示面板的储存电容。

[0034]

线路100形成于基板10上,并且位于基板10的内表面11(即图1所示的基板10上表面)上。基板10可以是玻璃板或半导体晶片。或者,基板10也可以是具有膜层的复合板材,其中基板10的内表面11可以是膜层的表面,而此膜层可以是绝缘层。此外,上述膜层可以是单一膜层(single layer)或多层膜(multilayer)。

[0035]

以线路100为显示面板的线路为例,基板10可包括玻璃板与绝缘层(玻璃板与绝缘层皆未示出)。绝缘层形成于玻璃板上,且可以是由氧化硅或氮化硅等无机材料所形成,而线路100可以形成于此绝缘层上。当然,在其他显示面板中,线路100也可以直接形成于玻璃板上。由此可知,线路100可直接形成于单一材料所构成的板材上,例如玻璃板或半导体晶片。或者,线路100也可形成于复合板材的膜层上,其中此膜层例如是绝缘层。

[0036]

线路100包括第一导电层111与缓冲层120,其中缓冲层120形成于基板10的内表面11上,而第一导电层111形成于缓冲层120上。在图1所示的实施例中,缓冲层120可以被夹置在基板10与第一导电层111之间,并接触基板10与第一导电层111,但本发明不以此特征为限制。第一导电层111的电阻率小于缓冲层120的电阻率,其中这里所述的电阻率是指20℃时的电阻率,其单位为欧姆

·

公尺(ω

·

m)。

[0037]

具体而言,在本实施例中,第一导电层111的材料的电阻率可小于100纳米欧姆

·

公尺(nω

·

m(20℃)),较佳地,小于30纳米欧姆

·

公尺(20℃)。例如,第一导电层111的主成分材料为铝、金、铜或银等金属材料,或是铝铜合金等合金材料。缓冲层120的材料的电阻率可大于30或100纳米欧姆

·

公尺,而缓冲层120的主成分材料为金属或合金,例如钽、钛、铬、钼、镍、钨或铬镍合金等。

[0038]

缓冲层120的材料也可包括上述金属的盐类,例如金属氧化物。具体而言,缓冲层120可采用物理气相沉积(physical vapor deposition,pvd)而形成,而在缓冲层120刚形成好之后,缓冲层120在其表面的一部分会因为接触空气而氧化,进而形成氧化物层。或者,缓冲层120在其表面的一部分因为后续工艺的影响而形成金属盐类膜层。例如,缓冲层120的表面因与蚀刻剂、光刻胶脱膜剂或其他化学药剂或气体反应而形成金属盐类膜层。

[0039]

同理,第一导电层111的材料不仅可以包括上述金属材料或合金材料,而且也可以包括上述金属的盐类,例如金属氧化物,其中此金属的盐类的形成方式可以相同或相似于前述缓冲层120金属盐类的形成方式。也就是说,第一导电层111的金属盐类材料可以是因为接触空气或是受后续工艺影响(例如与化学药剂或气体反应)而形成。

[0040]

虽然第一导电层111与缓冲层120可含有金属盐类,但由于第一导电层111与缓冲层120两者主成分为金属或合金材料,且上述金属盐类所形成的膜层通常很薄,因此第一导电层111与缓冲层120仍可导电,并能传输电信号。

[0041]

在本发明的一较佳实施例中,第一导电层111的材料为铜金属材料或主成份为铜的合金(例如铝铜合金),而缓冲层120的材料为钼金属材料或主成份为钼的合金,其中缓冲

层120的材料还可以包括钼的盐类,例如氧化钼。不过,在其他实施例中,第一导电层111的材料可为金、银或铝,或是以这些金属为主成分的合金材料,或是其他金属或合金材料。因此,第一导电层111与缓冲层120两者的材料不以铜(包括以铜为主成分的合金)与钼(包括以钼为主成分的合金)为限制。

[0042]

线路100还包括修饰层130,其中修饰层130形成于基板10上,并覆盖第一导电层111的上表面111u与侧边111s。以图1为例,修饰层130可以全面性覆盖第一导电层111未被缓冲层120覆盖的表面,其包括上表面111u与侧边111s,其中修饰层130可接触第一导电层111,但本发明不以此为限制。

[0043]

修饰层130的厚度130t可约介于10纳米至100纳米之间,而修饰层130的厚度130t可小于第一导电层111的厚度111t,其中这里的厚度130t可以是修饰层130在第一导电层111上表面111u、侧边111s及/或下表面111d处的厚度,如图1所示。

[0044]

基板10的内表面11、缓冲层120的侧边120s与第一导电层111的下表面111d会形成空腔c1,其中空腔c1从第一导电层111的侧边111s沿着基板10的内表面11而延伸至缓冲层120的侧边120s。换句话说,缓冲层120的侧边120s与第一导电层111的侧边111s不切齐,而缓冲层120内凹而形成空腔c1,其中第一导电层111下表面111d、基板10内表面11与缓冲层120侧边120s作为空腔c1的内壁。

[0045]

空腔c1为工艺过程中所形成的缺陷。举例而言,空腔c1可以是缓冲层120被光刻胶脱膜剂或蚀刻剂等化学药剂侵蚀而形成。因此,空腔c1其实是缺陷而非是原本要预设形成的空间。另外,须说明的是,在其他实施例中,缓冲层120的侧边120s与第一导电层111的侧边111s可以切齐,所以线路100不限制一定要有空腔c1。

[0046]

修饰层130可以还从第一导电层111的侧边111s填入于空腔c1中,以将空腔c1填满,其中修饰层130可用化学电镀来形成,其中化学电镀是利用两种材料之间所产生的自发性氧化还原反应来沉积膜层,所以不同于一般电镀(即有电电镀),化学电镀不使用外部电源所提供的电能来进行。

[0047]

修饰层130的标准还原电位(standard reduction potential)大于缓冲层120与第一导电层111其中至少一个的标准还原电位,以使上述化学电镀所进行的自发性氧化还原反应得以发生,其中这里的标准还原电位是指25℃时的标准还原电位,而标准还原电位也可以称为标准电极电位(standard electrode potential)。此外,标准还原电位是比较氢的还原电位而定义,其中氢的还原电位为0v,而根据不同材料的特性,标准还原电位可以是正值或负值。

[0048]

当修饰层130的标准还原电位为er,而缓冲层120或第一导电层111的标准还原电位为eo时,则电池标准电位(electrochemical cell potential)为ev,并等于修饰层130的标准还原电位(er)减去缓冲层120或第一导电层111的标准还原电位(eo),如以下数学式(1)所示。

[0049]

ev=er-eo

…………………………………………

(1)

[0050]

上述电池标准电位(ev)的负值正比于吉布斯自由能(gibbs free energy)变化量。也就是说,当上述电池标准电位(ev)为正值时,吉布斯自由能变化量为负值。反之,当上述电池标准电位(ev)为负值时,吉布斯自由能变化量为正值。根据基本热力学知识,当一化学反应的吉布斯自由能变化量为负值时,代表此化学反应是自发性反应。反之,当此化学反

应的吉布斯自由能变化量为正值时,代表此化学反应不是自发性反应。

[0051]

由于修饰层130的标准还原电位(er)大于缓冲层120或第一导电层111的标准还原电位(eo),因此电池标准电位(ev)为正值,即吉布斯自由能的变化量为负值,以至于用于形成修饰层130的氧化还原反应为自发性反应。如此,修饰层130得以利用化学电镀方式而形成。

[0052]

另外,在本实施例中,修饰层130的标准还原电位可大于缓冲层120与第一导电层111每一个的标准还原电位,以产生自发性氧化还原反应,让第一导电层111在其表面(例如上表面111u与侧边111s)的一部分以及缓冲层120在其表面(例如侧边120s)的一部分会被置换成构成修饰层130的材料,从而形成修饰层130。如此,修饰层130不仅可全面性地覆盖第一导电层111的上表面111u与侧边111s,而且更能延伸至空腔c1内,以覆盖缓冲层120的侧边120s与部分基板10的内表面11,进而填满空腔c1。

[0053]

在修饰层130的标准还原电位大于缓冲层120与第一导电层111其中至少一个的标准还原电位,以及第一导电层111的主成份材料为铜(包括含铜合金),缓冲层120的主成份材料为钼(包括含钼合金)的条件下,可用来制作修饰层130的材料包括钯、金、铂、银、锡或铅等金属。在修饰层130的标准还原电位大于缓冲层120与第一导电层111每一个的标准还原电位的条件下,可用来制作修饰层130的材料包括钯、金、铂或银等材料。

[0054]

另外,与前述第一导电层111及缓冲层120相同,修饰层130的材料也可包括上述金属(例如钯、金、铂、银、锡或铅)的盐类,例如氧化物。举例而言,修饰层130在其表面的一部分因接触空气而氧化,进而形成氧化物层。或者,修饰层130在其表面的部分因为后续工艺的影响而形成金属盐类膜层膜层。例如,修饰层130的表面因为与蚀刻剂或光刻胶脱膜剂反应而形成金属盐类膜层。

[0055]

上述修饰层130所形成的盐类膜层可以是很薄的膜层,且可具有偏低的光反射率,所以修饰层130能黑化线路100,以降低第一导电层111的光反射率。如此,修饰层130能降低因线路100反射光线而对显示器所造成的不良影响,从而有助于维持或提升显示器的图像品质。

[0056]

另外,线路100还可以包括绝缘层140与第二导电层112。绝缘层140形成于基板10上,并且覆盖修饰层130。以图1为例,绝缘层140全面性地覆盖修饰层130的上表面与侧边。第二导电层112形成于绝缘层140上,并与修饰层130至少部分重叠。在图1的实施例中,第二导电层112可与整个修饰层130重叠,但在其他实施例中,第二导电层112可与部分修饰层130重叠。

[0057]

由于修饰层130填满空腔c1,因此在后续工艺中,空腔c1内难以累积液体,或是水气或空气等气体,以至于在高温环境下,例如在高温炉内进行烘烤,修饰层130能让绝缘层140在空腔c1附近不易产生裂痕,以避免第一导电层111经由此裂痕而电性连接第二导电层112,造成短路。由此可知,修饰层130能修补缓冲层120与第一导电层111之间表面的缺陷(即空腔c1),以减少在后续工艺中,线路100发生例如短路等不好的状况,从而帮助良率的提升。

[0058]

图2是本发明另一实施例的电子装置的线路的剖面示意图。请参阅图2,本实施例的线路200与前述实施例相似,两者也包括相同的元件与配置,例如第一导电层111、缓冲层120、绝缘层140与第二导电层112,而且基板10的内表面11、缓冲层120的侧边120s与第一导

电层111的下表面111d也形成空腔c1,其从第一导电层111的侧边111s沿着基板10的内表面11而延伸至缓冲层120的侧边120s。然而线路100与200之间的差异在于:线路200所包括的修饰层230。

[0059]

与前述实施例相似,修饰层230也形成于基板10上,并填入空腔c1中。然而,修饰层230仅形成于空腔c1中。从图2来看,修饰层230未覆盖第一导电层111的上表面111u与侧边111s。此外,由于填满空腔c1的修饰层230仅形成于空腔c1中,因此修饰层230的厚度实质上可约等于缓冲层120的厚度120t,而修饰层230的厚度可约介于10纳米至100纳米之间。

[0060]

修饰层230的标准还原电位大于缓冲层120与第一导电层111其中至少一个的标准还原电位。在图2的实施例中,修饰层230的标准还原电位可大于缓冲层120的标准还原电位,但小于第一导电层111的标准还原电位。如此,在进行化学电镀的过程中,构成修饰层230的材料可以只从缓冲层120的侧边120s沉积,从而形成仅填满空腔c1的修饰层230。

[0061]

承上述,在第一导电层111的主成份材料为铜(包括含铜合金),而缓冲层120的主成份材料为钼(包括含钼合金)的条件下,可用来制作修饰层230的材料包括锡或铅等金属材料。因此,修饰层230的主成分材料可包括锡、铅或是以锡与铅至少一个为主成分的合金。此外,修饰层230的材料也可包括锡与铅其中一个的金属盐类,例如氧化锡或氧化铅,其中此金属盐类的形成可相同于前述实施例中修饰层130的金属盐类形成,故不再重复叙述。

[0062]

综上所述,利用上述修饰层,可帮助修补膜层表面的缺陷。例如,修饰层能填满因缓冲层被光刻胶脱膜剂或蚀刻剂等化学药剂侵蚀所形成的空腔,以修补缓冲层与第一导电层之间的表面,让缓冲层与第一导电层之间的表面变的较为平整。如此,修饰层能帮助避免上述空腔在后续工艺中所造成的问题,例如线路短路,进而提升良率。

[0063]

虽然本发明已以实施例公开如上,然而其并非用以限定本发明,本发明所属技术领域中技术人员,在不脱离本发明精神和范围内,当可作些许更动与润饰,因此本发明保护范围当视随附的权利要求所界定为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1