掺杂二维材料的阻变式随机存取存储器及其制备方法与流程

[0001]

本发明涉及一种掺杂二维材料的阻变式随机存取存储器及其制备方法,属于微电子技术领域。

背景技术:

[0002]

作为最具有潜力的非易失性存储器之一的阻变式随机存取存储器(rram),因其优异的性能已经收到越来越广泛的关注于研究。利用金属氧化物作为阻变层的rram通过施加电压对器件的影响,从而是的存储器在高低组态之间来回变化,实现数据的擦写和电流通道的阻断的操作,其低压、告诉、低功耗的特点使得rram器件极具研究价值。

[0003]

传统的阻变金属氧化层薄膜可以通过溅射、化学气相淀积(cvd)、原子层淀积(ald)等方法实现,但上述方法受限于设备或者环境影响,生产成本高,无法满足大批量低成本的工业化生产需求。

技术实现要素:

[0004]

本发明的目的在于提供一种掺杂二维材料的阻变式随机存取存储器及其制备方法,实现了低成本的rram制备,能满足大批量低成本的工业化生产需求。

[0005]

为达到上述目的,本发明提供如下技术方案:一种掺杂二维材料的阻变式随机存取存储器,包括由上至下设置的顶电极层,阻变氧化层和基底;所述阻变氧化层为掺杂二硫化钼粉末的氧化石墨烯层,所述基底包括上下层叠设置的底电极层和绝缘层。

[0006]

进一步地,所述顶电极在远离阻变氧化层的表面设有保护层,所述保护层为金属铝薄膜层或金属钨薄膜层中的任意一种。

[0007]

进一步地所述顶电极层包括若干个设置在阻变氧化层上的顶电极,所述顶电极为圆柱形金属银薄膜层或金属镍薄膜层或氮化钛薄膜层,厚度为20~60nm。

[0008]

进一步地所述底电极层为金属铂薄膜层或氧化铟锡薄膜层,厚度为50~150nm。

[0009]

进一步地所述绝缘层采用层叠设置的三层结构,包括由上至下设置的钛薄膜层、二氧化硅薄膜层和硅薄膜层叠层。

[0010]

进一步地所述绝缘层采用层叠设置的三层结构,包括由上至下设置的钛薄膜层、二氧化硅薄膜层和透明玻璃层叠层。

[0011]

一种根据所述的掺杂二维材料的阻变式随机存取存储器的制备方法,包括以下步骤:

[0012]

s1、提供基底,对所述基底进行预处理;

[0013]

s2、在所述基底上制备阻变氧化层,所述阻变氧化层为掺杂二硫化钼粉末的氧化石墨烯层;

[0014]

s3、在所述阻变氧化层上制备顶电极层;

[0015]

s4、在所述顶电极层的上表面制备保护层;

[0016]

进一步地,s2具体步骤如下:

[0017]

取氧化石墨烯粉末,配置成氧化石墨烯前驱体溶液,将mos2粉末和氧化石墨烯前驱体溶液进行掺杂得到mos2掺杂氧化石墨烯前驱体溶液,将静置后的mos2掺杂氧化石墨烯前驱体溶液滴加在所述基底上,进行旋涂,并退火至溶液凝固成膜,制得掺杂二硫化钼粉末的氧化石墨烯层。

[0018]

进一步地,步骤s2中,所述mos2掺杂氧化石墨烯前驱体溶液在20℃-30℃环境下进行配置,匀速搅拌至澄清,搅拌完毕后需在室温环境下静置5~10min,其中,氧化石墨烯的纯度为99.99%。

[0019]

进一步地,所述顶电极层和保护层采用蒸发镀膜法制备。

[0020]

与现有技术相比,本发明的有益效果在于:

[0021]

1)采用纯溶液法制备阻变氧化层,操作简单方便,实现了低成本的rram制备,设备和和原料投资较少可用于大面积rram器件的制备,实现大规模工业应用;

[0022]

2)相比于传统工艺制作单层或叠层纯金属氧化层的rram器件,阻变效果更好,针对置位(set)和复位(reset)过程所需要的电压较小,其绝对值小于2v,掺杂二维材料使得器件的耐受性和稳定性也有所提高;

[0023]

3)使用单质金属或单质金属化合物材料作为顶电极,替代了传统的氧化物材料上电极,进一步降低了成本和优化了制备工艺。

[0024]

上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,并可依照说明书的内容予以实施,以下以本发明的较佳实施例并配合附图详细说明如后。

附图说明

[0025]

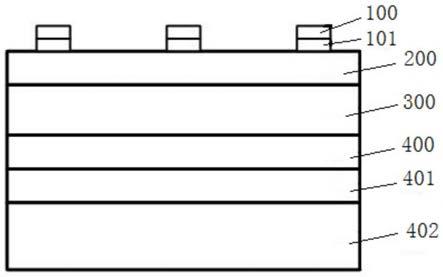

图1为本发明一实施例所示的掺杂二维材料的阻变式随机存取存储器的结构示意图;

[0026]

图2为本发明一实施例所示的掺杂二维材料的阻变式随机存取存储器在200~300℃范围内的阻变特性变化图。

具体实施方式

[0027]

下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。以下实施例用于说明本发明,但不用来限制本发明的范围。

[0028]

需要说明的是:本发明的“上”、“下”、“左”、“右”、“内”、“外”等用语只是参考附图对本发明进行说明,不作为限定用语。

[0029]

请参见图1,本发明一实施例所示的掺杂二维材料的阻变式随机存取存储器,包括由上至下设置的顶电极层,阻变氧化层200和基底,其中,顶电极层包括若干个设置在阻变氧化层200上的顶电极101,每个顶电极101在远离阻变氧化层200的表面均设有保护层100。在本申请中,阻变氧化层200为掺杂二维材料的氧化层,优选的,为掺杂二硫化钼粉末的氧化石墨烯层。

[0030]

在本实施例中,基底包括设置在上层的底电极层300和设置在下层的绝缘层,优选的,该绝缘层采用层叠设置的三层结构,包括由上至下依次设置的钛薄膜层400、二氧化硅薄膜层401和硅薄膜层402。

[0031]

在本实施例中,优选的,底电极层300为金属铂薄膜层,厚度为100nm;保护层100为

金属钨(w)薄膜层;顶电极101为圆柱形金属银薄膜层,厚度为40nm,直径为0.1mm。

[0032]

本实施例的阻变式随机存取存储器采用以下方法制备:

[0033]

a)基底预处理;

[0034]

将基底完全浸入盛放无水乙醇的烧杯中,将烧杯置于去离子水环境中进行第一次10min超声清洗;

[0035]

第一次超声清洗后,用去离子水冲洗基底去除残留的乙醇杂质,之后将基底完全浸入盛放丙酮的烧杯中,将烧杯置于去离子水环境中进行第二次10min超声清洗;

[0036]

第二次超声清洗后,用去离子水冲洗基底并用氮气吹干;

[0037]

将上述经超声清洗并干燥处理的基底放入表面等离子清洗机的真空腔内,进行表面等离子清洗以增强底电极层的亲水性;表面等离子清洗过程时间持续20min;

[0038]

b)制备阻变氧化层;

[0039]

在室温(优选25℃)条件下,取氧化石墨烯粉末,用去离子水配置成go前驱体溶液;取1.5mg、纯度为99.99%的go粉末置于烧杯中,并向烧杯中加入10ml去离子水,配置成0.15mg/ml的go前驱体溶液;匀速搅拌至溶液澄清,之后静置80min;

[0040]

在室温(优选25℃)条件下,将mos2粉末与go前驱体溶液按照1:25的比例进行掺杂;

[0041]

在完成表面等离子清洗后10min内,将掺杂完毕的go前驱体溶液通过0.45μm孔径、pes材质滤嘴的注射器滴加在底电极层300上,旋涂35s,转速为3500rpm;旋涂完毕后,置于200℃的加热板上退火0.5h,go前驱体溶液在底电极层上凝固成膜,制得掺杂阻变氧化层;

[0042]

c)制备顶电极层;

[0043]

将颗粒状金属材料ag放置于电子束蒸发镀膜机的坩埚中,将孔径为0.1mm的掩膜板覆盖于阻变氧化层上,掩膜板向下放入镀膜机腔体中的吸板上,关闭腔体进行蒸发镀膜操作,将金属材料ag镀制在阻变氧化层上,形成具有顶电极的半成品;

[0044]

d)制备保护层;

[0045]

顶电极制作完成后,将颗粒状金属材料w放置于电子束蒸发镀膜机的坩埚中,将孔径为0.1mm的掩膜板覆盖于顶电极上,掩膜板向下放入镀膜机腔体中的吸板上,关闭腔体进行二次蒸发镀膜操作,在顶电极上镀制形成金属w保护层。

[0046]

请参见图2,图示为本实施例rram器件的阻变效应测试结果,以横坐标0点为分界线,正轴为set(置位)过程,负轴为reset(复位)过程,其电压偏置绝对值都在2v以下,且阻变效应均保持在一定范围内,reset过程中出现一定概率的渐变现象,掺杂二维材料氧化层使得器件的耐受性和稳定性也有所提高。

[0047]

综上所述,本发明的掺杂二维材料的阻变式随机存取存储器及其制备方法具有以下效果:

[0048]

1)采用纯溶液法制备阻变氧化层,操作简单方便,实现了低成本的rram制备,设备和和原料投资较少可用于大面积rram器件的制备,实现大规模工业应用;

[0049]

2)相比于传统工艺制作单层或叠层纯金属氧化层的rram器件,阻变效果更好,针对置位(set)和复位(reset)过程所需要的电压较小,其绝对值小于2v,掺杂二维材料使得器件的耐受性和稳定性也有所提高;

[0050]

3)使用单质金属或单质金属化合物材料作为顶电极,替代了传统的氧化物材料上

电极,进一步降低了成本和优化了制备工艺

[0051]

以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0052]

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1