垂直结构MOS半导体器件的制作方法

垂直结构mos半导体器件

技术领域

1.本实用新型涉及mosfet器件技术领域,尤其涉及一种垂直结构mos半导体器件。

背景技术:

2.mosfet(金属氧化物半导体场效应晶体管)分为增强型和耗尽型,其中增强型是指当vgs(栅源电压)为0 时,管子呈截止状态,当加上合适的vgs 后,多数载流子被吸引到栅极,从而使多晶栅极下的载流子增强,形成导电沟道,这种mos管称为增强型mos管。

技术实现要素:

3.本实用新型的目的是提供一种垂直结构mos半导体器件,该垂直结构mos半导体器件缓和了沟槽拐角处的电场强度,提高了器件抗击穿的耐受能力。

4.为达到上述目的,本实用新型采用的技术方案是:一种垂直结构mos半导体器件,包括:位于硅片下表面的重掺杂n型漏极区和位于硅片上表面的中掺杂p型基极区,所述重掺杂n型漏极区和中掺杂p型基极区之间具有一轻掺杂n型漂移区,一位于中掺杂p型基极区中沟槽延伸至轻掺杂n型漂移区下部,所述中掺杂p型基极区上部内且位于沟槽的周边具有第一重掺杂n型源极区,一介质层覆盖于沟槽上并延伸至第一重掺杂n型源极区内侧边缘的上方;

5.所述沟槽内下部具有第二n型源极部,此沟槽内上部具有栅极部,所述栅极部与沟槽之间填充有第一氧化硅层,所述第二n型源极部与沟槽之间填充有第二氧化硅层,所述第二n型源极部和栅极部之间通过第三氧化硅层隔离;

6.所述第二n型源极部下端的左拐角处和右拐角处的第二氧化硅层内分别设置有第一弧形高介电层、第二弧形高介电层。

7.上述技术方案中进一步改进的方案如下:

8.1. 上述方案中,所述第一弧形高介电层的竖直部位于第二n型源极部外侧面与沟槽内壁之间,所述第一弧形高介电层的水平部位于第二n型源极部底部与沟槽底部之间。

9.2. 上述方案中,所述第二弧形高介电层的竖直部位于第二n型源极部外侧面与沟槽内壁之间,所述第二弧形高介电层的水平部位于第二n型源极部底部与沟槽底部之间。

10.3. 上述方案中,所述中掺杂p型基极区的深度与轻掺杂n型漂移区的深度之比在1:3~5之间的范围。

11.由于上述技术方案的运用,本实用新型与现有技术相比具有下列优点:

12.本实用新型垂直结构mos半导体器件,其沟槽内下部具有第二n型源极部,第二n型源极部下端的左拐角处和右拐角处的第二氧化硅层内分别设置有第一弧形高介电层、第二弧形高介电层,缓和了沟槽拐角处的电场强度,提高了器件抗击穿的耐受能力。

附图说明

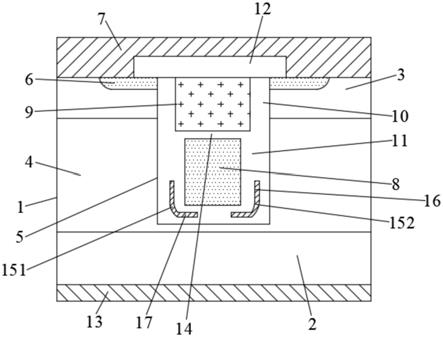

13.附图1为本实用新型垂直结构mos半导体器件结构示意图。

14.以上附图中:1、硅片;2、重掺杂n型漏极区;3、中掺杂p型基极区;4、轻掺杂n型漂移区;5、沟槽;6、第一重掺杂n型源极区;7、上金属层;8、第二n型源极部;9、栅极部;10、第一氧化硅层;11、第二氧化硅层;12、介质层;13、下金属层;14、第三氧化硅层;151、第一弧形高介电层;152、第二弧形高介电层;16、竖直部;17、水平部。

具体实施方式

15.在本实用新型的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制;术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性;此外,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本实用新型中的具体含义。

16.实施例1:一种垂直结构mos半导体器件,包括:位于硅片1下表面的重掺杂n型漏极区2和位于硅片1上表面的中掺杂p型基极区3,所述重掺杂n型漏极区2和中掺杂p型基极区3之间具有一轻掺杂n型漂移区4,一位于中掺杂p型基极区3中沟槽5延伸至轻掺杂n型漂移区4下部,所述中掺杂p型基极区3上部内且位于沟槽5的周边具有第一重掺杂n型源极区6,一介质层12覆盖于沟槽5上并延伸至第一重掺杂n型源极区6内侧边缘的上方;

17.所述沟槽5内下部具有第二n型源极部8,此沟槽5内上部具有栅极部9,所述栅极部9与沟槽5之间填充有第一氧化硅层10,所述第二n型源极部8与沟槽5之间填充有第二氧化硅层11,所述第二n型源极部8和栅极部9之间通过第三氧化硅层14隔离;

18.所述第二n型源极部8下端的左拐角处和右拐角处的第二氧化硅层11内分别设置有第一弧形高介电层151、第二弧形高介电层152。

19.上述中掺杂p型基极区3的深度与轻掺杂n型漂移区4的深度之比在1:3.5之间的范围。

20.实施例2:一种垂直结构mos半导体器件,包括:位于硅片1下表面的重掺杂n型漏极区2和位于硅片1上表面的中掺杂p型基极区3,所述重掺杂n型漏极区2和中掺杂p型基极区3之间具有一轻掺杂n型漂移区4,一位于中掺杂p型基极区3中沟槽5延伸至轻掺杂n型漂移区4下部,所述中掺杂p型基极区3上部内且位于沟槽5的周边具有第一重掺杂n型源极区6,一介质层12覆盖于沟槽5上并延伸至第一重掺杂n型源极区6内侧边缘的上方;

21.所述沟槽5内下部具有第二n型源极部8,此沟槽5内上部具有栅极部9,所述栅极部9与沟槽5之间填充有第一氧化硅层10,所述第二n型源极部8与沟槽5之间填充有第二氧化硅层11,所述第二n型源极部8和栅极部9之间通过第三氧化硅层14隔离;

22.所述第二n型源极部8下端的左拐角处和右拐角处的第二氧化硅层11内分别设置有第一弧形高介电层151、第二弧形高介电层152。

23.上述第一弧形高介电层151的竖直部16位于第二n型源极部8外侧面与沟槽5内壁之间,所述第一弧形高介电层151的水平部17位于第二n型源极部8底部与沟槽5底部之间。

24.上述第二弧形高介电层152的竖直部16位于第二n型源极部8外侧面与沟槽5内壁之间,所述第二弧形高介电层152的水平部17位于第二n型源极部8底部与沟槽5底部之间。

25.上述中掺杂p型基极区3的深度与轻掺杂n型漂移区4的深度之比在1:4.6。

26.采用上述垂直结构mos半导体器件时,其沟槽内下部具有第二n型源极部,第二n型源极部下端的左拐角处和右拐角处的第二氧化硅层内分别设置有第一弧形高介电层、第二弧形高介电层,缓和了沟槽拐角处的电场强度,提高了器件抗击穿的耐受能力。

27.上述实施例只为说明本实用新型的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本实用新型的内容并据以实施,并不能以此限制本实用新型的保护范围。凡根据本实用新型精神实质所作的等效变化或修饰,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1