一种适用于浅腔体芯片叠层电路的熔封工艺夹具及封帽方法与流程

1.本发明涉及一种适用于浅腔体芯片叠层电路的熔封工艺夹具及封帽方法,属于集成电路封装技术领域。

背景技术:

2.熔封封帽工艺是集成电路封装领域的一种高可靠气密性封帽工艺。集成电路熔封封帽过程中,集成电路置于熔封设备内,在特定温度和压力条件下,管帽上预制的金锡合金焊料环熔化,分别与盖板和陶瓷外壳封口环的镀金层相互溶解扩散形成固溶体结构,界面处形成稳定的金属间化合物,从而将管帽与陶瓷外壳钎焊到一起。

3.熔封封帽工艺传统的施加压力的方法通常是在管帽的上方压块,通过压块的重力为管帽提供熔封时所需的压力条件,但是对于浅腔体芯片叠层电路采用的带腔体的管帽而言,使用这种方法会导致管帽中间部位发生凹陷,造成外观缺陷,影响电路的长期使用可靠性,当管帽凹陷严重时甚至会触碰到电路腔体内部的键合丝造成电路失效。

技术实现要素:

4.本发明解决的技术问题是:针对目前现有技术中,熔封封帽工艺传统施加压力的工艺是通过压块实现,容易导致电路可靠性、外观缺陷、管帽凹陷的问题,提出了一种适用于浅腔体芯片叠层电路的熔封工艺夹具。

5.本发明解决上述技术问题是通过如下技术方案予以实现的:

6.一种适用于浅腔体芯片叠层电路的熔封工艺夹具,包括上盖、下定位板,所述上盖上设置有压槽、定位螺孔,下定位板上设置有定位槽、定位螺孔,上盖通过螺钉及定位螺孔与下定位板固定连接,待加工浅腔体芯片叠层电路的陶瓷外壳设置于定位槽中,待加工浅腔体芯片叠层电路的管帽扣置于陶瓷外壳的封口环上,上盖设置于管帽上,通过压槽边沿压住管帽设置有焊料环的帽沿,螺钉插入定位螺孔中实现上盖与下定位板固定。

7.所述螺钉拧紧压力根据管帽的尺寸确定,并通过扭力扳手进行调节。

8.所述待加工浅腔体芯片叠层电路在熔封前,通过管帽的金锡焊料环的长度确定待加工浅腔体芯片叠层电路与上盖、下定位板组成的夹具的摆放间隔,将上盖、下定位板组成的夹具与待加工浅腔体芯片叠层电路共同进行熔封。

9.所述夹具材质选用不锈钢或硬铝材料。

10.所述夹具通过扭力扳手可以实现压力调节,上盖压槽的边沿在熔封过程中压在待加工浅腔体芯片叠层电路的管帽帽沿的上方。

11.所述夹具施加的夹力f的范围为其中,x为管帽的长度,y为管帽的宽度,单位均为mm。

12.一种适用于浅腔体芯片叠层电路的熔封工艺夹具提出的适用于浅腔体芯片叠层电路的熔封工艺夹具的封帽方法,其特征在于步骤如下:

13.(1)将待加工浅腔体芯片叠层电路放置于夹具的下定位板上;

14.(2)通过扭力扳手、螺钉固定夹具及待加工浅腔体芯片叠层电路;

15.(3)将夹具及待加工浅腔体芯片叠层电路阵列摆放于熔封设备中完成密封。

16.所述夹具及待加工浅腔体芯片叠层电路摆放的间距d的范围为其中,p为管帽金锡合金焊料环的长度,单位为mm。

17.本发明与现有技术相比的优点在于:

18.本发明提供的一种适用于浅腔体芯片叠层电路的熔封工艺夹具,通过利用本发明中的特制夹具及封帽方法,能够对浅腔体芯片叠层电路进行熔封工艺封帽,可以实现对电路封帽压力的调节,利用本发明的夹具及封帽方法配合,可以保证浅腔体芯片叠层电路进行熔封后气密性和熔封空洞满足标准要求,解决了传统封帽工艺容易出现的各种问题。

附图说明

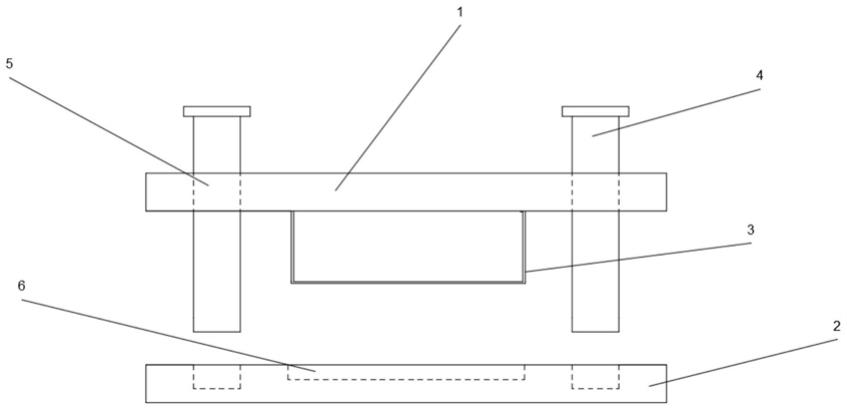

19.图1为发明提供的夹具结构示意图实施例一;

20.图2为发明提供的夹具与电路整体的剖面示意图实施例一;

21.图3为发明提供的夹具结构示意图实施例二;

22.图4为发明提供的夹具与电路整体的剖面示意图实施例二;

具体实施方式

23.一种适用于浅腔体芯片叠层电路的熔封工艺夹具及封帽方法,以完成对浅腔体芯片叠层电路的熔封工艺封帽,且封帽前能够根据管帽尺寸对封帽压力进行调整,熔封工艺夹具包括上盖、下定位板,其中:

24.上盖上设置有压槽、定位螺孔,下定位板上设置有定位槽、定位螺孔,上盖通过螺钉及定位螺孔与下定位板固定连接,待加工浅腔体芯片叠层电路的陶瓷外壳设置于定位槽中,待加工浅腔体芯片叠层电路的管帽扣置于陶瓷外壳的封口环上,上盖设置于管帽上,通过压槽边沿压住管帽设置有焊料环的帽沿,螺钉插入定位螺孔中实现上盖与下定位板固定;

25.螺钉拧紧压力根据管帽的尺寸确定,并通过扭力扳手进行调节;

26.待加工浅腔体芯片叠层电路在熔封前,通过管帽的金锡焊料环的长度确定待加工浅腔体芯片叠层电路与上盖、下定位板组成的夹具的摆放间隔,将上盖、下定位板组成的夹具与待加工浅腔体芯片叠层电路共同进行熔封;

27.夹具材质选用不锈钢或硬铝材料;

28.夹具通过扭力扳手可以实现压力调节,上盖压槽的边沿在熔封过程中压在待加工浅腔体芯片叠层电路的管帽帽沿的上方;

29.夹具施加的夹力f的范围为其中,x为管帽的长度,y为管帽的宽度,单位均为mm。

30.通过上述夹具结构,进行适用于浅腔体芯片叠层电路的熔封工艺夹具的封帽方法,具体步骤如下:

31.(1)将待加工浅腔体芯片叠层电路放置于夹具的下定位板上;

32.(2)通过扭力扳手、螺钉固定夹具及待加工浅腔体芯片叠层电路;

33.(3)将夹具及待加工浅腔体芯片叠层电路阵列摆放于熔封设备中完成密封。

34.其中,夹具及待加工浅腔体芯片叠层电路摆放的间距d的范围为其中,p为管帽金锡合金焊料环的长度单位为mm。

35.下面根据具体实施例进行进一步说明:

36.在当前实施例中,如图1所示,夹具主要由上盖1、下定位板2和螺钉4组成。上盖1包括压槽3和定位螺孔5,下定位板2包括定位槽6和定位螺孔5。如图2所示,出了本发明实施例一夹具与电路整体的剖面示意图,在进行熔封工艺前,首先,将浅腔体芯片叠层电路的陶瓷外壳7放置在定位槽6中,用防静电吸笔将管帽8吸起,扣置在陶瓷外壳7的封口环上;随后,将上盖1放置在管帽8的上面,使压槽3的边沿压住管帽8带有焊料环的帽沿;接着,将螺钉4插入定位螺孔5中,根据管帽8的尺寸,利用扭力扳手调整到适当的压力;最后,根据管帽8的金锡焊料环的长度,选择适当的摆放间隔,将夹具和电路整体一起放置在熔封设备中完成密封。

37.本发明实施例二的夹具示意图如图3所示,夹具主要由上盖9、下压板10和砝码13组成。上盖9带有压槽11,下压板10带有定位槽12。本发明实施例二夹具与电路整体的剖面示意图如图4所示,在进行熔封工艺前,首先,将浅腔体芯片叠层电路的陶瓷外壳7放置在定位槽12中,用防静电吸笔将管帽8吸起,扣置在陶瓷外壳7的封口环上;随后,将上盖9放置在管帽8的上面,使压槽12的边沿压住管帽8带有焊料环的帽沿;接着,根据管帽8的尺寸将适当重量的砝码13放置在上盖9的上面;最后,根据管帽8的金锡焊料环的长度,选择适当的摆放间隔,将夹具和电路整体一起放置在熔封设备中完成密封。

38.根据本发明特制的熔封工艺夹具和封帽方法,能够对浅腔体芯片叠层电路进行熔封工艺封帽,且可以根据管帽尺寸对封帽压力进行调节,使封帽后电路的气密性和焊料空洞能够满足设计要求。

39.本发明虽然以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

40.本发明说明书中未作详细描述的内容属于本领域专业技术人员的公知技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1