一种IPD吸收式高通滤波器的制作方法

一种ipd吸收式高通滤波器

技术领域

[0001]

本发明涉及一种ipd吸收式高通滤波器,属于滤波器技术领域。

背景技术:

[0002]

常规的滤波器设计电路,是通过把不需要的信号反射回源,达到滤波的目的。在大部分应用中,反射回源的信号会对电路的性能造成很大的影响。例如,滤波器经常会用在混频器的前面和后面,而常规滤波器反射的阻带信号会在混频器中产生一些不必要的谐波;在高增益放大器电路中,反射回源的阻带信号可能会使放大器不稳定和振荡。设计接近或满足电路要求的滤波器,是一项巨大的挑战。

技术实现要素:

[0003]

本发明的目的在于克服现有滤波器存在的上述缺陷,提供了一种ipd吸收式高通滤波器,基于ipd工艺和新型电路拓扑结构形成,达到尺寸小和带外无反射的效果。

[0004]

本发明是采用以下的技术方案实现的:一种ipd吸收式高通滤波器,包括基体层和其上表面的金属层,金属层上形成有电路结构,电路结构包括高通通路单元和信号吸收单元,高通通路单元包括串联在输入端口和输出端口之间的第一电容,第一电容和输入端口之间连接有第一电感,第一电感连接有第一接地电容,第一电容和输出端口之间连接有第二电感,第二电感连接有第二接地电容,所述信号吸收单元为三个电阻形成的π型衰减器。

[0005]

进一步地,第一电容由两个子电容串联形成。

[0006]

进一步地,第一电感和第二电感采用平面螺旋结构。

[0007]

进一步地,第一电容、第一接地电容和第二接地电容均采用薄膜平行板电容。

[0008]

进一步地,信号吸收单元的电阻由82%ni和18%cr组成。

[0009]

进一步地,电阻通过磁控溅射共沉积方法获得精准电阻值。

[0010]

进一步地,第一电感的电感值与第二电感的电感值相等,所述第一接地电容的电容值与第二接地电容的电容值相等。

[0011]

进一步地,所述基体层为为砷化镓、氮化硅或硅。

[0012]

进一步地,高通通路单元和信号吸收单元可以作为子单元进行多级级联。

[0013]

本发明的有益效果是:(1)本发明的第一电容由两个子电容串联而成,通过电容串联的方式增大工艺的容差,增加电容的耐压值;(2)本发明通过信号吸收单元吸收阻带信号,阻止反射信号回信号源来实现滤波器的无反射特性,防止反射回源的信号对电路性能的影响;(3)本发明具有很好的可扩展性,可根据需求进行直接级联设计,通过牺牲插入损耗,提供更高的带外衰减;(4)本发明基于ipd工艺和新型电路拓扑结构形成,最终达到尺寸小和带外无反射的效

果。

附图说明

[0014]

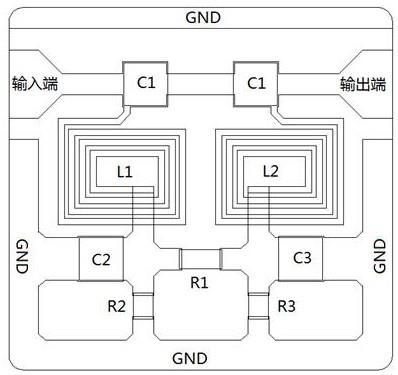

图1为本发明的电路拓扑图;图2为本发明的内部结构示意图;图3为本发明的封装外壳结构示意图;图4为本发明的三维电路结构示意图;图5为本发明的s参数仿真结果图中标记:1封装外壳;11 输入端口;12输出端口。

具体实施方式

[0015]

下面结合附图对本发明作进一步说明。

[0016]

如图1所示,本实施例的吸收式高通滤波器包括基体层和大地层,基体层的上表面有金属层,金属层上形成有电路结构,电路结构包括高通通路单元和信号吸收单元,高通通路包含输入端、输出端、端口地、第一电容c1、第一电感l1、第二电感l2、第一接地电容c2、第二接地电容c3;其中输入端连接第一电容c1,第一电容c1另一端连接输出端,输入端和第一电容c1之间连接第一电感l1,第一电感l1另一端连接信号吸收单元,输出端和第一电容c1之间连接第二电感l2,第二电感l2另一端连接信号吸收单元,第一电感l1和信号吸收单元之间连接第一接地电容c2,第一接地电容c2另一端接地,第二电感l2和信号吸收单元之间连接第二接地电容c3,第二电容c3另一端接地;其中信号吸收单元包含电阻r1、电阻r2、电阻r3、端口地,其中三个电阻形成一个π型衰减器。

[0017]

如图2、图3、图4所示,本实施例的吸收式高通滤波器包括封装外壳1和ipd滤波器本体,封装外壳1可采用铝金属或者合金制备,该封装外壳1作为滤波器的安装底座,本实施案例的整体封装尺寸为(1.1mm

×

1.0mm

×

0.5mm),封装外壳1的厚度为100um,在滤波器对应输入端口11和输出端口12作开口处理如图中11和12所示,从而实现滤波器输入端和输出端的引出,同时封装外壳1作为电路的接地端使用;ipd滤波器本体采用ipd硅工艺,通过光刻、金属沉积、干法刻蚀、高温氧化刻蚀等工序制备,等效电感采用平面螺旋结构;等效电容采用薄膜平行板电容;等效电阻采用82%ni和18%cr组成通过磁控溅射共沉积方法获得精准电阻值,ipd滤波器的尺寸为(0.9mm

×

0.8mm

×

0.25mm)。

[0018]

如图5所示,本实施例的吸收式高通滤波器3db截止频率为3.0ghz,4ghz~8ghz通带内插入损耗小于1.0db;dc~6ghz驻波小于15db;阻带内,在dc到1.5ghz范围内抑制大于20db。

[0019]

以上显示和描述了本发明的基本原理和主要特征和本发明的优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的只是说明本发明的原理,在不脱离本发明精神和范围的前提下,本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明范围内。本发明要求保护范围由所附的权利要求书及其等效物界定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1