一种图形化h-BN薄膜及MIS半导体器件的制备方法

一种图形化h-bn薄膜及mis半导体器件的制备方法

技术领域

1.本发明涉及二维材料生长和半导体器件技术领域,尤其涉及一种图形化h-bn薄膜及mis半导体器件的制备方法。

背景技术:

2.h-bn(即六方氮化硼)薄膜具有非常高的透明度、导热性和机械强度,高度的抗氧化性,在高温下具有良好的稳定性。此外,由于h-bn薄膜具有超光滑平面、没有悬挂键和电荷陷阱以及与石墨烯分子结构相似等性质。h-bn薄膜可用于多种应用,如介电层、透明和可弯曲的电子器件、深紫外发射器、电容储能装置、保护层和多功能纳米孔等。对于这些应用,所使用的h-bn薄膜需具备尺寸大、厚度均匀、无缺陷等特点。然而,即使生长出了高质量,大面积,均匀性良好的单晶h-bn薄膜,依然要面临着刻蚀工艺,将生长出的高质量,大面积,均匀性良好的单晶h-bn薄膜刻蚀出所需形状和尺寸,而这些工艺会破坏h-bn薄膜的结构,尤其是h-bn薄膜的边缘,会引入不可避免的晶界,缺陷和污染物,导致载流子复合和漏电等问题,制约了h-bn薄膜的应用,降低了h-bn薄膜的可用性。

3.制备h-bn薄膜的方法有许多种,包括机械剥离、液相剥离、展开bn纳米管、取代反应、射频磁控溅射、电子束照射和化学气相沉积(cvd)。其中,cvd方法已被确定为合成大型纳米片的常用途径。最近,常压cvd和低压cvd系统已经被开发出来,以用来生长大面积的h-bn薄膜。

4.此外,由于h-bn薄膜具有超光滑平面、没有悬空键和电荷陷阱,具有~6ev的禁带宽度等性质,使h-bn在半导体器件中作为绝缘层有着巨大的优势,可应用于高性能mis型电子器件。在cvd系统中,cu箔常被用作生长h-bn薄膜的催化金属衬底。基于cu催化金属衬底易于刻蚀的特性,便于制造出微图形化cu衬底,并在此之上可以实现微图形化的h-bn薄膜的生长。同时,由于在cu衬底上生长后的h-bn的薄膜有转移的需求,在转移的过程中,有诸多步骤的存在,包括清除衬底四边的光刻胶,溶液配制(快速腐蚀),缓慢腐蚀,清洗工艺,转移工艺,去光刻胶和清洗等工艺,其中难以避免h-bn薄膜破损。

5.基于目前h-bn薄膜的制备方法存在的缺陷,有必要对此进行改进。

技术实现要素:

6.有鉴于此,本发明提出了一种图形化h-bn薄膜及mis半导体器件的制备方法,以解决或至少部分解决现有技术中存在的问题。

7.第一方面,本发明提供了一种图形化h-bn薄膜的制备方法,包括以下步骤:

8.提供衬底;

9.在所述衬底上制备图形化gan;

10.在所述图形化gan上制备cu以形成图形化cu;

11.利用氮化硼前驱体,在图形化cu上生长得到h-bn薄膜,即得图形化h-bn薄膜。

12.优选的是,所述的图形化h-bn薄膜的制备方法,在所述衬底上制备图形化gan具体

包括:

13.在所述衬底上生长gan薄膜;

14.在所述gan薄膜上生长sio2薄膜;

15.在所述sio2薄膜上涂覆第一光刻胶,曝光出与图形化gan相适配的图案,显影,刻蚀sio2薄膜,移除第一光刻胶,形成图形化sio2;

16.刻蚀gan薄膜后,再刻蚀掉图形化sio2,即得到图形化gan。

17.优选的是,所述的图形化h-bn薄膜的制备方法,在所述图形化gan上制备cu以形成图形化cu具体包括:

18.在所述图形化gan上涂覆第二光刻胶,曝光出与图形化cu相适配的图案,再于第二光刻胶上生长cu薄膜,去除第二光刻胶和第二光刻胶上的cu薄膜,即得图形化cu。

19.优选的是,所述的图形化h-bn薄膜的制备方法,利用氮化硼前驱体,在图形化cu上生长得到h-bn薄膜具体包括:

20.将形成有图形化cu的衬底于h2流下,以950~1070℃下退火0.5~3h;

21.将退火后的衬底置于化学气相沉积设备中,加热生长腔室至1030~1070℃,通入氮化硼前驱体,前驱体加热区温度设置为70~90℃,氮化硼前驱体的分解物在图形化cu上生长得到h-bn薄膜。

22.优选的是,所述的图形化h-bn薄膜的制备方法,所述氮化硼前驱体包括bh3nh3、(hbnh)3、bf3nh3、bcl3nh3中的至少一种。

23.优选的是,所述的图形化h-bn薄膜的制备方法,在所述衬底上制备图形化gan具体包括:

24.以nh3和tmga分别作为gan生长的n源和ga源,在所述衬底上生长得到gan。

25.优选的是,所述的图形化h-bn薄膜的制备方法,所述衬底包括蓝宝石衬底、碳化硅衬底、氮化镓衬底、硅衬底、蓝宝石/氮化镓衬底、碳化硅/氮化镓衬底中的一种;

26.在所述图形化gan上制备cu的步骤中,cu的厚度为40~60nm。

27.第二方面,本发明还提供了mis半导体器件的制备方法,包括以下步骤:

28.采用所述的方法制备得到图形化h-bn薄膜;

29.利用cu金属腐蚀液将h-bn薄膜下方的铜腐蚀,使h-bn薄膜沉淀在图形化gan上;

30.在h-bn薄膜上涂覆第三光刻胶,曝光出与图形化h-bn薄膜相适配的图案,然后于第三光刻胶上生长金属薄膜,去除第三光刻胶和第三光刻胶上的金属薄膜,得到图形化mis半导体器件。

31.优选的是,所述的mis型半导体器件的制备方法,所述cu金属腐蚀液包括水、hcl和h2o2的混合物,其中,所述水、hcl和h2o2的体积比为(140~160):(20~30):(20~30)。

32.优选的是,所述的mis型半导体器件的制备方法,所述金属薄膜包括ni薄膜、ti薄膜、al薄膜、v薄膜、au薄膜、cu薄膜中的一种。

33.本发明的一种图形化h-bn薄膜及mis半导体器件的制备方法相对于现有技术具有以下技术效果:

34.本发明的图形化h-bn薄膜的制备方法,由于在图形化的gan衬底上的图形内沉积cu薄膜,利用cu、gan两种衬底的催化特性的区别,实现h-bn在cu衬底上生长而无法在gan上生长,达到原位生长微图案化h-bn的目的,从而避免传统二维材料图形刻蚀工艺带来的边

缘缺陷,导致载流子复合和漏电等问题;将本发明制备的h-bn薄膜作为电介质层制备mis半导体器件,可以提高半导体器件的性能和工作稳定性。

附图说明

35.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

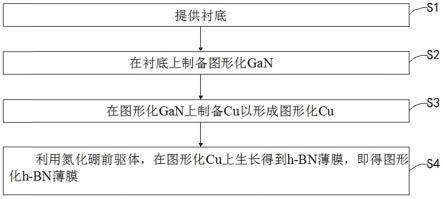

36.图1为本发明的图形化h-bn薄膜的制备方法流程示意图;

37.图2为本发明在衬底上制备图形化gan的示意图;

38.图3为本发明在图形化gan上制备cu以形成图形化cu的示意图;

39.图4~5为本发明的mis半导体器件的制备方法示意图。

具体实施方式

40.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。

41.因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

42.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

43.在本发明的描述中,需要理解的是,如“上”等指示方位或位置的关系为基于附图所示的方位或位置关系,或者是该发明产品使用时惯常摆放的方位或位置关系,或者是本领域技术人员惯常理解的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的设备或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

44.下面将结合本发明实施方式,对本发明实施方式中的技术方案进行清楚、完整的描述,显然,所描述的实施方式仅仅是本发明一部分实施方式,而不是全部的实施方式。基于本发明中的实施方式,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施方式,都属于本发明保护的范围。

45.本技术实施例提供了一种图形化h-bn薄膜的制备方法,如图1所示,包括以下步骤:

46.s1、提供衬底;

47.s2、在衬底上制备图形化gan;

48.s3、在图形化gan上制备cu以形成图形化cu;

49.s4、利用氮化硼前驱体,在图形化cu上生长得到h-bn薄膜,即得图形化h-bn薄膜。

50.本技术的图形化h-bn薄膜的制备方法,由于在图形化的gan衬底上的图形内沉积cu薄膜,利用两种衬底的催化特性的区别,实现h-bn在cu衬底上生长而无法在gan上生长,达到原位生长微图案化h-bn的目的,从而避免传统二维材料图形刻蚀工艺带来的边缘缺陷,导致载流子复合和漏电等问题,提高微尺寸半导体器件的性能和工作稳定性。

51.在一些实施例中,请参考图2所示,步骤s2中在衬底上制备图形化gan具体包括:

52.在衬底10上生长gan薄膜11,如图2中s20所示;

53.在gan薄膜11上生长sio2薄膜12,如图2中s21所示;

54.在sio2薄膜12上涂覆第一光刻胶13,如图2中s22所示,然后曝光出与图形化gan相适配的图案,显影,刻蚀sio2薄膜12,如图2中s23~s24所示,移除第一光刻胶13,形成图形化sio2,如图2中s25所示;

55.刻蚀gan薄膜11后,再刻蚀掉图形化sio2,如图2中s26~27所示,即得到图形化gan。

56.具体的,上述实施例中,采用mocvd在衬底上生长一定厚度(例如厚度为350~450nm)的gan薄膜;之后,采用pecvd法在衬底/gan上生长一定厚度(例如厚度为150~250nm)的sio2薄膜;然后在衬底/gan/sio2上涂覆第一光刻胶,利用掩膜板曝光出与图形化gan相适配的图案,显影,采用rie设备,利用ar和氟碳化合物(chf3或cf4),刻蚀掉sio2薄膜;采用丙酮和乙醇去除第一光刻胶,形成图形化衬底/gan/sio2模板;采用icp刻蚀,利用cl2/bcl3混合气体,刻蚀一定厚度的gan;最后,在采用上述相同的rie工艺,利用ar和氟碳化合物(chf3或cf4),移除图形化sio2薄膜剩下的部分,最终得到图形化gan。

57.在一些实施例中,请参考图3所示,步骤s3中在图形化gan上制备cu以形成图形化cu具体包括:

58.在图形化gan上涂覆第二光刻胶14,如图3中s30所示,曝光出与图形化cu相适配的图案,再于第二光刻胶14上生长cu薄膜15,如图3中s31所示,去除第二光刻胶14和第二光刻胶上的cu薄膜15,如如3中s32所示,即得图形化cu。

59.具体的,上述实施例中,在图形化衬底/gan上涂敷第二光刻胶,曝光相应的图案;之后,采用电子束蒸镀设备,选取cu金属蒸发源,基于膜厚仪监测,生长40~60nm厚度的cu薄膜;然后,采用丙酮去除光刻胶和光刻胶上的cu薄膜,形成了图形化衬底/gan/cu。

60.在一些实施例中,请参考图4所示,利用氮化硼前驱体,在图形化cu上生长得到h-bn薄膜具体包括:

61.将形成有图形化cu的衬底于h2流下,以900~1200℃下退火0.5~2h;

62.将退火后的衬底置于化学气相沉积设备中,通入氮化硼前驱体,前驱体加热区温度设置为70~90℃,氮化硼前驱体的分解物在图形化cu上生长得到h-bn薄膜16。

63.具体的,在上述实施例中,在生长之前,将图形化衬底/gan/cu在每分钟250~350标准立方厘米(sccm)的h2流下,以950~1070℃下退火0.5~3h;再将退火后的衬底/gan/cu置于化学气相沉积设备中,加热生长腔室至1030~1070℃(优选的,加热生长腔室至1050℃),通入氮化硼前驱体,前驱体加热区温度设置为70~90℃,将氮化硼前驱体的分解物引入h-bn生长区,生长25~35min,以便在图形化衬底/gan/cu上生长h-bn,而无法在gan上生长h-bn薄膜;h-bn薄膜生长之后,关闭前驱体和生长区加热程序,h-bn薄膜的生长区在25~35sccm的h2流下自然冷却到室温。

64.在一些实施例中,氮化硼前驱体包括bh3nh3、(hbnh)3、bf3nh3、bcl3nh3中的至少一种。

65.在一些实施例中,在衬底上制备图形化gan具体包括:

66.以nh3和tmga分别作为gan生长的n源和ga源,在衬底上生长得到gan。

67.具体的,利用mocvd在衬底上生长gan薄膜,nh3和tmga(三甲基镓)分别作为gan生长的n源和ga源;h2作为载气;反应室衬底托盘的温度固定在1000~1100℃,并且以5~15r/min的速率旋转;反应室顶壁的温度固定在300~400℃,tmga的流量固定在100~200μmol/min;利用上述条件生长350~450nm的gan薄膜。

68.在一些实施例中,衬底包括蓝宝石衬底、碳化硅衬底、氮化镓衬底、硅衬底、蓝宝石/氮化镓衬底、碳化硅/氮化镓衬底中的一种;其中,衬底如果是蓝宝石(sapphire)、碳化硅(sic)、硅si等材料,利用金属有机化学气相沉积(mocvd)的方法生长了sapphire/gan、sic/gan模板衬底材料,其中主要是利用gan宽禁带半导体的性质;优选的,利用sapphire/gan模板衬底材料,在sapphire/gan模板表面采用沉积催化金属cu薄膜,用于选择性催化生长h-bn微图形阵列。

69.在一些实施例中,在图形化gan上制备cu的步骤中,cu的厚度为40~60nm;尽管电子束蒸镀的cu薄膜是沉积在图形化gan衬底上,会有因为cu薄膜超出图形化gan上部分的边缘产生的多余的h-bn薄膜,从而使腐蚀了图形化cu衬底之后的图形化h-bn薄膜降落在gan上时,使h-bn边缘产生晶界,从而影响半导体器件的质量;图形化cu衬底的厚度有必要控制,使其不会产生过多的h-bn薄膜。本技术是利用在gan和cu衬底上生长h-bn薄膜之间的不同的生长机制,提高了生长图形化h-bn薄膜的可能;同时,由于生长机制的区别和cu衬底厚度的控制,在对于h-bn薄膜尺寸大小和形状的控制上有着至关重要的作用,从而实现了一种图形化h-bn薄膜的半导体器件,该器件可以极大的提高器件的性能和稳定性。主要解决了目前在制备半导体器件中,使用h-bn薄膜需要特定的尺寸和形状时而不可避免引入一定可能的缺陷的问题。本发明具有工艺简单,效果显著,应用前景广阔等优点。

70.基于同一发明构思,本技术实施例还提供了一种mis半导体器件的制备方法,包括以下步骤:

71.采用上述的方法制备得到图形化h-bn薄膜;

72.利用cu金属腐蚀液将h-bn薄膜下方的铜腐蚀,使h-bn薄膜沉淀在图形化gan上;

73.在h-bn薄膜上涂覆第三光刻胶,曝光出与图形化h-bn薄膜相适配的图案,然后于第三光刻胶上生长金属薄膜,去除第三光刻胶和第三光刻胶上的金属薄膜,得到图形化mis半导体器件。

74.本技术的mis半导体器件为半导体-绝缘-金属(mis)型半导体器件,以h-bn薄膜作为电介质层并以该微图案化h-bn作为电介质层,制备高性能的mis型半导体器件阵列。具体的,参考图4~5所示,利用cu金属腐蚀液将h-bn薄膜16下方的铜薄膜15腐蚀,如图4中s41所示,腐蚀后的h-bn薄膜16降落在图形化gan上,利用了h-bn薄膜与图形化gan表面之间的相互作用,以确保h-bn薄膜可以在cu腐蚀完后,能够遗留在图形化gan的顶部,如图4中s42所示;在h-bn薄膜16上涂覆第三光刻胶17,如图5中s50所示,曝光出与图形化h-bn薄膜相适配的图案,然后于第三光刻胶17上生长金属薄膜18,如图5中s51所示,去除第三光刻胶17和第三光刻胶上的金属薄膜18,如图5中s52所示,得到图形化mis半导体器件。

75.在一些实施例中,cu金属腐蚀液包括水、hcl和h2o2的混合物,其中,水、hcl和h2o2的体积比为(140~160):(20~30):(20~30)。

76.具体的,图形化h-bn薄膜中的cu衬底的腐蚀:包括快速腐蚀和缓慢腐蚀;快速腐蚀溶液的配制:150ml的去离子水+25ml的hcl+25ml的h2o2;(可以适当多加hcl和h2o2,确保1:1体积比例);缓慢腐蚀溶液的配制方法为:在1000ml的去离子水中,加入足够多的na2(so4)2粉末,配制得到饱和的na2(so4)2溶液,即为缓慢腐蚀溶液。

77.快速腐蚀到类似于纸厚的程度即可;缓慢腐蚀时,要将通风橱的风机关闭,当cu腐蚀完,剩下的材料很薄,极易因为振动而破损;其中,快速腐蚀溶液的高度与衬底/gan/cu/h-bn的高度大致相平行,腐蚀后的h-bn薄膜漂浮在图形化gan上方,便于之后的捞取操作;此处的缓慢腐蚀液的高度也需要与衬底/gan/cu/h-bn的高度大致相平行;将腐蚀cu后的衬底/gan和h-bn薄膜缓慢转移到去离子水中,清洗;清洗后的材料薄膜在去离子水中,用衬底/gan将h-bn薄膜缓慢兜起来,放置自然干燥(不能使用加热蒸发干燥,否则会产生特别的褶皱),h-bn薄膜可以沉淀在图形化衬底/gan上。

78.具体的,图形化h-bn薄膜中的cu衬底的腐蚀时,快速腐蚀时间为30s,缓慢腐蚀时间为5min。

79.在一些实施例中,采用光刻工艺,在h-bn薄膜上涂覆第三光刻胶,曝光图形化的蓝宝石衬底/gan/h-bn和衬底/第三光刻胶;之后,采用电子束蒸镀的工艺在图形化的蓝宝石衬底/gan/h-bn沉积90~110nm厚度的金属薄膜(作为金属电极),蒸镀的金属可以有:ni,ti,al,v,au,cu等金属;然后,使用丙酮洗去第三光刻胶和其上的金属薄膜,形成图形化衬底/gan/h-bn金属结构,进而形成mis型半导体器件阵列。

80.在一些实施例中,本技术所采用的第一光刻胶、第二光刻胶、第三光刻胶均可采用现有常规的光刻胶,比如可采用az703光刻胶、su-8光刻胶等。

81.以下进一步以具体实施例说明本技术的图形化h-bn薄膜的制备方法的制备方法、mis半导体器件的制备方法。本部分结合具体实施例进一步说明本发明内容,但不应理解为对本发明的限制。如未特别说明,实施例中所采用的技术手段为本领域技术人员所熟知的常规手段。除非特别说明,本发明采用的试剂、方法和设备为本领域常规试剂、方法和设备。

82.实施例1

83.本技术实施例提供了一种图形化h-bn薄膜的制备方法,包括以下步骤:

84.s1、提供蓝宝石衬底;

85.s2、利用mocvd在蓝宝石衬底上生长gan薄膜,nh3和tmga(三甲基镓)分别作为gan生长的n源和ga源;h2作为载气;反应室衬底托盘的温度固定在1050℃,并且以10r/min的速率旋转;反应室顶壁的温度固定在350℃,tmga的流量固定在150μmol/min;利用上述条件生长400nm厚度的gan薄膜;

86.s3、采用pecvd法在蓝宝石衬底/gan上生长200nm厚度的sio2薄膜;然后在蓝宝石衬底/gan/sio2上涂覆第一光刻胶,利用掩膜板曝光出与图形化gan相适配的图案,显影,采用rie设备,利用ar和氟碳化合物(chf3或cf4),刻蚀掉sio2薄膜;采用丙酮和乙醇去除第一光刻胶,形成图形化衬底/gan/sio2模板;采用icp刻蚀,利用cl2/bcl3混合气体,刻蚀400nm厚度的gan;最后,在采用上述相同的rie工艺,利用ar和氟碳化合物(chf3或cf4),移除图形化sio2薄膜剩下的部分,最终得到图形化蓝宝石衬底/gan;

87.s4、在图形化蓝宝石衬底/gan上涂敷第二光刻胶,曝光相应的图案;之后,采用电子束蒸镀设备,选取cu金属蒸发源,基于膜厚仪监测,生长50nm厚度的cu薄膜;然后,采用丙酮去除光刻胶和光刻胶上的cu薄膜,形成了图形化蓝宝石衬底/gan/cu;

88.s5、将图形化蓝宝石衬底/gan/cu在每分钟300标准立方厘米(sccm)的h2流下,以1050℃下退火1h;再将退火后的衬底/gan/cu置于化学气相沉积设备中,加热生长腔室至1050℃,通入氨硼烷(h3n-bh3)前驱体,前驱体加热区温度设置为80℃,将氮化硼前驱体的分解物引入h-bn生长区,生长30min,以便在图形化蓝宝石衬底/gan/cu上生长h-bn薄膜;h-bn薄膜生长之后,关闭前驱体和生长区加热程序,h-bn薄膜的生长区在30sccm的h2流下自然冷却到室温。

89.实施例2

90.本技术实施例提供了一种mis半导体器件的制备方法,包括以下步骤:

91.s1、采用实施例1中的方法得到图形化h-bn薄膜;

92.s2、利用cu金属腐蚀液将h-bn薄膜下方的铜腐蚀,使h-bn薄膜沉淀在图形化gan上;cu金属腐蚀液包括150ml水、25mlhcl和25ml h2o2的混合物;

93.s3、在h-bn薄膜上涂覆第三光刻胶,曝光出与图形化h-bn薄膜相适配的图案,采用电子束蒸镀的工艺在图形化的蓝宝石衬底/gan/h-bn上沉积100nm厚度的金属薄膜ni;然后,使用丙酮洗去光刻胶和其上的金属薄膜ni,形成图形化的蓝宝石衬底/gan/h-bn/金属结构,即得mis半导体器件。

94.上所述仅为本发明的较佳实施方式而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1