一种基于原子层沉积的ZrxHf(1-x)O2薄膜的制备方法与流程

本发明属于半导体领域,涉及用于dram电容器介电层的薄膜制备技术,具体涉及一种基于原子层沉积的zrxhf(1-x)o2薄膜的制备方法。

背景技术:

1、动态随机存取内存(dram)是过去几十年来半导体行业中的重要存储器件。随着技术的发展,为了实现更高的性能和更低的功耗,单元大小需要进一步缩小。因此,对于dram电容介质层,已经进行了大量关于高介电常数(k)材料的研究。其中,基于zro2的薄膜,特别是zro2/al2o3/zro2(zaz),由于其适当的k值、低泄漏电流和与tin的兼容性,在最近的dram技术中得到了应用。然而,尽管在zaz薄膜中泄漏电流得到了良好控制,但这些薄膜的k值与其他材料相比降低,这是由于al2o3的低k值(k≈9)。因此,已经进行了研究替代zaz的介电材料和结构。

2、金红石型tio2(k≈100)和srtio3(k≈150)已被广泛研究作为高介电常数材料。然而,这些材料具有很小的带隙(约为3.0-3.2ev),导致高泄漏电流,并需要开发新的电极材料来替代主要用作电极材料的tin。hfo2已作为代表性的高介电常数材料在栅极介电层和dram电容器介电层应用中得到了广泛研究。已经进行了许多研究来提高hfo2的介电常数值,例如使用碳、硅和al2o3等掺杂剂。hfo2可以存在不同晶体结构,具有不同的介电常数值,如单斜结构(k≈20),正交结构(k≈30),立方结构和四方结构(k>40)。一般来说,单斜结构比立方结构和四方结构具有更高的表面能。因此,hfo2的四方结构在约3nm的小晶粒尺寸下是稳定的,这被称为临界晶粒尺寸。同时,zro2在四方相中比hfo2更稳定,并且具有20nm的临界晶粒尺寸以及与hfo2相似的化学结构和性能。因此,已经进行了大量关于hfxzr(1-x)o2混合结构和hfo2/zro2层状结构的电介质应用研究。

3、同时,所采用的薄膜沉积方法也会影响晶体结构。对于dram应用而言,原子层沉积(ald)是唯一适用于高介电常数薄膜沉积的沉积技术,是由于dram电容结构具有较高的纵横比。为了在ald中实现掺杂或混合结构,通常利用包含掺杂剂循环的超周期来代替常规循环。通过这种方法沉积的薄膜具有层状结构,因为它具有逐层ald沉积的特点。但是通过这个过程获得的杂质或混合物剖面在深度方向上不可避免地具有局部浓度梯度,这导致了不均匀的薄膜。这会导致薄膜的部分区域可能部分未掺杂。

4、现有技术在制备zrxhf(1-x)o2薄膜时也存在一些问题或限制。首先,采用zro2和hfo2交替沉积的方式制备薄膜流程复杂,需要多次沉积和热处理步骤,增加了制备成本和时间。其次,这种方法无法实现薄膜中不同元素的均匀分布,可能导致薄膜性能不均一。另外,晶界漏电流是栅介质材料中常见的问题,而现有技术中的薄膜容易产生晶界漏电流,限制了器件的性能和可靠性。

技术实现思路

1、发明目的:为了克服现有技术中存在的不足,提供一种基于原子层沉积的zrxhf(1-x)o2薄膜的制备方法。

2、技术方案:为实现上述目的,本发明提供一种基于原子层沉积的zrxhf(1-x)o2薄膜的制备方法,包括如下步骤:

3、s1:对基片进行清洗,然后将基片推入原子层沉积设备反应室;

4、s2:准备zr前驱体cpzr和hf前驱体cphf,按照指定zr摩尔浓度进行混合,得到混合前驱体cphfzr;

5、s3:将混合前驱体cphfzr输送到原子层沉积设备的反应室内,对混合前驱体cphfzr执行原子层沉积处理;

6、s4:重复步骤s2和s3,直至在基片上沉积获得指定厚度的zrxhf(1-x)o2薄膜。

7、进一步地,薄膜沉积时需要有较高洁净度的晶片表面,否则会影响薄膜沉积质量,导致器件漏电流增加等一些不理想的特性。所述步骤s1中基片的清洗方法为:

8、a1:将晶片切割为3cm×3cm大小,并用n2枪吹掉切片过程中边缘处上的碎渣;

9、a2:将切割好的基片正面朝上先后浸泡在丙酮、无水乙醇、去离子水中超声清洗5分钟,以去除表面杂质;

10、a3:用n2吹干基片,立即送入到真空系统中。

11、进一步地,所述步骤s2中zr摩尔浓度分别为40、50、60、70mol%,得到4种不同浓度比的混合前驱体cphfzr。

12、进一步地,所述步骤s3中混合前驱体cphfzr输送到原子层沉积设备的反应室内的方法为:将混合前驱体cphfzr加热至指定温度,利用ar作为运载混合前驱体的气体,输送到原子层沉积设备的反应室内。

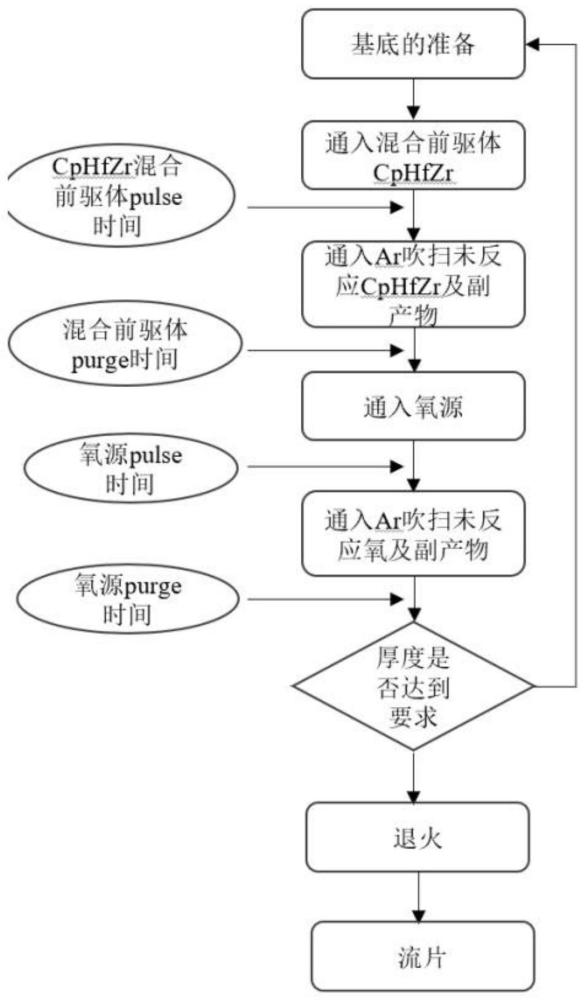

13、进一步地,所述步骤s3中原子层沉积处理的执行过程为:

14、b1:保持反应室温度,对混合前驱体cphfzr进行脉冲,待混合前驱体cphfzr脉冲时间到后,停止脉冲;

15、b2:进行ar吹扫,带走未反应的混合前驱体cphfzr及副产物;

16、b3:吹扫结束后,通入o2作为等离子体的源气体,用ar作为运载氧源,在指定温度下及等离子气体形成的情况下进行脉冲;

17、b4:进行ar吹扫,带走未反应的氧原子及副产物。

18、进一步地,所述步骤s3中混合前驱体cphfzr加热至60℃~80℃。

19、进一步地,所述步骤b1中保持反应室温度在280℃~320℃。

20、进一步地,所述步骤b1中脉冲时间为13~17s,所述步骤b3中脉冲时间为9~11s。

21、进一步地,所述步骤b2中ar吹扫的时间为22~27s,所述步骤b4中ar吹扫的时间为12~18s。

22、进一步地,所述步骤s2中采用环戊二烯基三(二甲氨基)锆(zrcp[nme2]3,cpzr)作为zr前驱体,环戊二烯基三(二甲氨基)铪(hfcp[nme2]3,cphf)作为hf前驱体,其中cp代表环戊二烯基,me为甲基。

23、本发明通过原子层沉积(ald)使用两种前体的混合前体混合物,研究了均匀的zrxhf(1-x)o2(x<1)薄膜在动态随机存取存储器(dram)电容器介电层中的沉积,研究了zr/hf浓度比变化对电性能的影响。与层状zro2/hfo2和单层薄膜相比,提高了电性能。

24、本发明制备的zrxhf(1-x)o2薄膜具有高介电常数、尺寸小、热稳定性好和不易产生晶界漏电流等优点,因此在半导体器件中具有广阔的应用前景。该薄膜可以作为栅介质材料在金属氧化物半导体场效应晶体管(mosfet)中使用,用于隔离栅极和通道之间的电荷,从而实现更高的电子迁移率和更低的功耗。

25、此外,zrxhf(1-x)o2薄膜的高介电常数还使其在电子器件领域中具有潜力。例如,在电容器、电阻器和电感器等元件中,利用高介电常数可以实现更高的电容、电阻和感应效果,从而提高电子器件的性能和效率。

26、在集成电路领域,zrxhf(1-x)o2薄膜可以用于制造高性能的存储器、逻辑电路和射频器件等。其高介电常数和热稳定性使得zrxhf(1-x)o2薄膜可以在集成电路中实现更高的电容比、更低的电路功耗和更好的热稳定性能。

27、有益效果:本发明与现有技术相比,具备如下优点:

28、1、本发明制备的zrxhf(1-x)o2薄膜具有高介电常数,可以有效提高栅介质材料的综合性能。

29、2、本发明通过使用环戊二烯基三(二甲氨基)锆和环戊二烯基三(二甲氨基)铪作为混合前驱体,不需要使用zro2/hfo2交替沉积的方式,可以实现薄膜中不同元素的均匀分布。

30、3、相对于传统方法,本发明的制备流程更简化,无需进行复杂的交替沉积步骤,从而降低了制备的复杂度和成本,工艺效率也得到了提升。

31、4、由于环戊二烯基(cp)为环形结构,结构稳定,zrxhf(1-x)o2薄膜具有良好的热稳定性,能够在高温环境下保持稳定的介电性能。

32、5、解决了现有薄膜容易产生晶界漏电流的问题,应用器件的性能和可靠性能够得到保障。

- 还没有人留言评论。精彩留言会获得点赞!