相关电源产生电路的实现方法与流程

本发明涉及一种相关电源产生电路的实现方法。

背景技术:

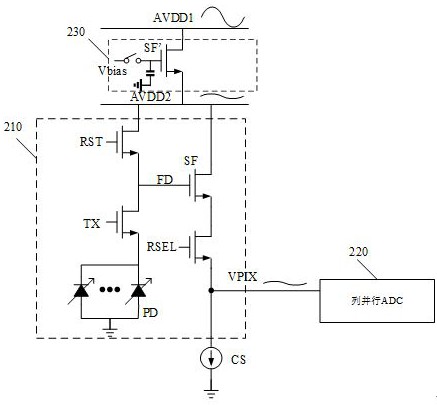

1、图像传感器芯片是把光信号转换为电信号的芯片。通常芯片中间区域是起到感光作用的像素阵列(pixel array),像素阵列周围是外围电路。像素阵列包含阵列排布的多个像素单元,每个像素单元包括光电二极管和多个像素晶体管,如图1所示,像素单元100为目前普遍采用的4t像素结构,其中包括光电二极管pd、转移晶体管tx、复位晶体管rst、源跟随晶体管sf、行选择晶体管rsel。

2、相关双采样(correlated double sampling,cds)技术已经被普遍用于消除图像传感器像素内的固定模式噪声(fixed pattern noise,fpn),即在每个像素读出过程中进行两次采样,测量两次输出电压:第一次测量是在复位晶体管进行复位操作后采样,第二次测量是在信号释放结束后采样,最终输出的是这两次采样测量的电压差值,由于在两次采样时间间隔里,复位晶体管和电路相关的差异均维持不变,那么两次采样值相减即可消除复位晶体管的热噪声(ktc噪声)和列fpn干扰,有效提高了信噪比。

3、然而,除了fpn,图像传感器信号中还叠加了电源噪声等随机噪声,这部分会随时间变化的噪声影响是无法通过相关双采样进行消除的。随着高像素图像传感器的发展与应用对电源噪声提出了更加严峻的要求与挑战,电源噪声成为影响图像质量的主要因素之一。

4、如图1所示,像素阵列的供电电源avdd上的干扰会经过选中行像素单元的源跟随晶体管传到像素单元的输出电压vpix上,进而进入列并行模数转换器(adc)进行ad量化,由于在一个行时间内,选中行所有像素单元的源跟随晶体管都连接在avdd上,从而avdd上的干扰会通过这些源跟随晶体管传到所有的列并行adc上,而由于在每一个行时间上avdd上干扰的大小不尽相同,从而会在图像上产生电源噪声。

5、为降低电源噪声影响,目前业界主流做法:

6、1. 通过引进和avdd相关的干扰至像素单元的源跟随晶体管的偏置电路(如图2)或者列并行adc(如图3)上进行叠加消除,但是前者这种消除方法需要像素单元的源跟随晶体管和其偏置电路做相应的匹配,难以把控;而后者这种叠加消除办法一般是通过采样avdd相关的干扰经过处理后,从列并行adc的一端将该处理后的干扰叠加在adc上进行消除,从而就整个adc阵列来说,引入至adc的干扰可能有空间上的差异而降低衰减效果。另一方面为了进行有效的衰减或者消除电源噪声,电源噪声消除电路对电源噪声的增益和相位的控制要相对比较精准,这就需要消耗大量的面积和功耗。

7、2.通过在电源的供电焊盘(pad)上增加较大的片外滤波电容进而从源头上衰减电源噪声。缺点是占用面积,增加成本。

技术实现思路

1、本发明的目的在于提供一种相关电源产生电路的实现方法,以较小的面积和成本,消除电源噪声对相关双采样的影响。

2、基于以上考虑,本发明提供一种相关电源产生电路的实现方法,其特征在于,包括:提供第一电源电压;通过相关电源产生电路接收所述第一电源电压并输出第二电源电压,以使得所述第二电源电压在不同时刻具有相关性,从而消除电源噪声对相关双采样的影响。

3、优选的,所述相关电源产生电路包括源跟随器。

4、优选的,所述源跟随器包括至少一个源跟随晶体管,所述源跟随晶体管漏极连接第一电源电压输出端,所述源跟随晶体管源极连接像素电路输入端,所述源跟随晶体管栅极连接偏置电压。

5、优选的,每列像素电路对应一个相关电源产生电路。

6、优选的,多列像素电路对应一个相关电源产生电路。

7、优选的,每个相关电源产生电路分别独立地输出至对应的像素电路。

8、优选的,多个相关电源产生电路并联后一起输出至对应的像素电路。

9、优选的,通过连接于所述源跟随晶体管栅极的开关电容采样保持结构,进行逐行或逐帧的采样保持。

10、优选的,所述偏置电压大于或等于所述第一电源电压。

11、优选的,通过低阈值电压工艺形成所述源跟随晶体管。

12、优选的,通过连接于所述像素电路输出端的电流源,为所述相关电源产生电路提供偏置电流。

13、优选的,通过连接于所述像素电路输出端的模数转换器,在不同时刻分别采样所述像素电路输出的电压信号。

14、优选的,通过所述相关电源产生电路对所述第一电源电压进行滤波降噪。

15、与现有技术相比,本发明相关电源产生电路的实现方法具有如下有益效果:

16、(1)本申请通过相关电源产生电路接收第一电源电压并输出第二电源电压,以使得所述第二电源电压在不同时刻具有相关性,从而消除电源噪声对相关双采样的影响。

17、(2)可采用列并行电路的做法,一列或多列像素电路对应一个相关电源产生电路,以提高局部噪声消除效果。

18、(3)既可以每个相关电源产生电路分别独立地输出供给对应列的像素电路以离散各列的电源干扰,也可以将多个相关电源产生电路并联在一起输出以增强输出的驱动能力。

19、(4)相关电源产生电路通过源跟随晶体管的方式实现,电路结构简单,面积消耗小,输出电压易编程可控处理。

20、(5)源跟随晶体管栅极连接开关电容采样保持结构,可通过逐行或逐帧地采样保持以消除其栅极电压的共模干扰。

21、(6)通过采用高于第一电源电压的偏置电压或者采用低阈值电压工艺制成的低阈值电压晶体管,以降低第二电源电压相较于第一电源电压的压降,以免影响供电能力和驱动带载能力。

22、(7)可直接借用像素电路输出的偏置电流对该相关电源产生电路进行偏置,无需消费额外的电流,增加额外的功耗。

23、(8)此外,相关电源产生电路还对第一电源电压进行了滤波降噪,并将滤波降噪后的第二电源电压提供至像素电路,进一步降低了电源噪声的影响。

24、(9)在此基础上,还可复用传统的电源噪声消除电路进行进一步的衰减和消除。

技术特征:

1.一种相关电源产生电路的实现方法,其特征在于,包括:

2.如权利要求1所述的相关电源产生电路的实现方法,其特征在于,所述相关电源产生电路包括源跟随器。

3.如权利要求2所述的相关电源产生电路的实现方法,其特征在于,所述源跟随器包括至少一个源跟随晶体管,所述源跟随晶体管漏极连接第一电源电压输出端,所述源跟随晶体管源极连接像素电路输入端,所述源跟随晶体管栅极连接偏置电压。

4.如权利要求3所述的相关电源产生电路的实现方法,其特征在于,每列像素电路对应一个相关电源产生电路。

5.如权利要求3所述的相关电源产生电路的实现方法,其特征在于,多列像素电路对应一个相关电源产生电路。

6.如权利要求3所述的相关电源产生电路的实现方法,其特征在于,每个相关电源产生电路分别独立地输出至对应的像素电路。

7.如权利要求3所述的相关电源产生电路的实现方法,其特征在于,多个相关电源产生电路并联后一起输出至对应的像素电路。

8.如权利要求3所述的相关电源产生电路的实现方法,其特征在于,通过连接于所述源跟随晶体管栅极的开关电容采样保持结构,进行逐行或逐帧的采样保持。

9.如权利要求3所述的相关电源产生电路的实现方法,其特征在于,所述偏置电压大于或等于所述第一电源电压。

10.如权利要求3所述的相关电源产生电路的实现方法,其特征在于,通过低阈值电压工艺形成所述源跟随晶体管。

11.如权利要求3所述的相关电源产生电路的实现方法,其特征在于,通过连接于所述像素电路输出端的电流源,为所述相关电源产生电路提供偏置电流。

12.如权利要求3所述的相关电源产生电路的实现方法,其特征在于,通过连接于所述像素电路输出端的模数转换器,在不同时刻分别采样所述像素电路输出的电压信号。

13.如权利要求1所述的相关电源产生电路的实现方法,其特征在于,通过所述相关电源产生电路对所述第一电源电压进行滤波降噪。

技术总结

本发明提供一种相关电源产生电路的实现方法,通过相关电源产生电路接收第一电源电压并输出第二电源电压,以使得所述第二电源电压在不同时刻具有相关性,从而消除电源噪声对相关双采样的影响。可采用列并行电路的做法,一列或多列像素电路对应一个相关电源产生电路,以提高局部噪声消除效果。既可以每个相关电源产生电路分别独立地输出供给对应列的像素电路以离散各列的电源干扰,也可以将多个相关电源产生电路并联在一起输出以增强输出的驱动能力。相关电源产生电路通过源跟随晶体管的方式实现,电路结构简单,面积消耗小,输出电压易编程可控处理。

技术研发人员:赵立新,乔劲轩,范爱鹏

受保护的技术使用者:格科微电子(上海)有限公司

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!