一种双核心的域控制器的制作方法

1.本实用新型属于电子技术和域控制器领域,具体涉及一种双核心的域控制器。

背景技术:

2.随着汽车智能网联的发展,传统的整车电子电气架构和车内网络通讯方式已经难以满足越来越多样化的功能需求。电子电气架构方面,域控制器+区域控制器的集中式架构正逐渐取代分布式架构成为主流,车内功能逐渐集中融合到域控制器中。车内通讯方面,不同于传统基于信号的通讯架构,soa(service-oriented architecture)架构采用基于服务发布调用的方式,通过配置服务发布列表和调用列表来实现功能更新,不再需要更改整车通讯矩阵实现变更。作为整车电子电气架构的核心部件和soa架构载体,域控制器相较于传统车载控制器在硬件上需要更为强大的处理芯片以提供更高的算力,同时在软件开发上也更注重降低耦合度,提高软件的复用度降低开发量。

3.现有技术常常采用一块主芯片进行控制,如cn213715751u公开了一种域控制器,该域控制器采用一块主芯片实现域控制器功能,现有技术中还有大量采用一块主芯片进行控制的技术方案(如cn112440904b),此处不再一一赘述。因此,现有技术可能存在算力不够的情况,并且当该主芯片发生故障时,该域控制器随即失去控制能力,也没有对该域控制器进行心跳监控,导致可靠性不足。

技术实现要素:

4.针对现有技术中的上述不足,本实用新型提供的一种双核心的域控制器解决了现有技术中存在的问题。

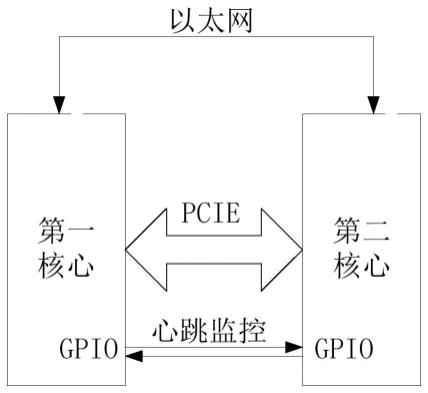

5.为了达到上述实用新型目的,本实用新型采用的技术方案为:一种双核心的域控制器,包括第一核心以及第二核心,所述第一核心与第二核心通过三条通信线路电性连接;

6.第一条所述通信线路为以太网线路,所述第一核心通过以太网线路电性连接至第二核心;第二条所述通信线路为pcie线路,所述第一核心的pcie接口通过pcie线路电性连接至第二核心的pcie接口;第三条所述通信线路为通用数据传输线路,所述第一核心的gpio接口通过通用数据传输线路电性连接至第二核心的gpio。

7.在一种可能的实施方式中,所述第一核心包括型号为s32g274a的控制芯片u1,所述第二核心包括型号为s32g274a的控制芯片u2,所述控制芯片u1与控制芯片u2通过三条通信线路电性连接。

8.在一种可能的实施方式中,所述控制芯片u1的gpio1引脚与控制芯片u2的gpio1引脚电性连接,所述控制芯片u1的gpio2引脚与控制芯片u2的gpio2引脚电性连接,以形成通用数据传输线路。

9.在一种可能的实施方式中,所述控制芯片u1的rgmii功能引脚上设置有4个均由型号为bcm89883的phy芯片u7构成的第一以太网接口,所述控制芯片u2的rgmii功能引脚上设置有4个均由型号为bcm89883的phy芯片u14构成的第二以太网接口;

10.任一所述第一以太网接口通过rj45接口与任一所述第二以太网接口电性连接,以形成以太网线路。

11.在一种可能的实施方式中,所述控制芯片u1的can功能引脚上设置有12个型号均为tja1043的can芯片u8,所述控制芯片u2的can功能引脚上设置有12个型号均为tja1043的can芯片u15,以提供多路can接口。

12.在一种可能的实施方式中,所述控制芯片u1通过i2c总线与型号为vr5510的电源芯片u3电性连接,所述控制芯片u2通过i2c总线与型号为vr5510的电源芯片u10电性连接。

13.在一种可能的实施方式中,所述控制芯片u1通过sdio总线电性连接至第一emmc存储器,所述控制芯片u1的ddr功能引脚上设置有第一lpddr4内存;所述控制芯片u2通过sdio总线电性连接至第二emmc存储器,所述控制芯片u2的ddr功能引脚上设置有第二lpddr4内存。

14.在一种可能的实施方式中,所述控制芯片u1通过spi总线电性连接至型号为xdsm3276的加密芯片u4,所述控制芯片u2通过spi总线电性连接至型号为xdsm3276的加密芯片u11。

15.在一种可能的实施方式中,所述控制芯片u1通过uart总线分别电性连接至第一lin芯片u5和第二lin芯片u6,所述第一lin芯片u5和第二lin芯片u6所采用的型号均为tja1021;所述控制芯片u2通过uart总线分别电性连接至第三lin芯片u12和第四lin芯片u13,所述第一lin芯片u12和第二lin芯片u13所采用的型号均为tja1021。

16.在一种可能的实施方式中,所述控制芯片u1通过i2c总线电性连接至第一rtc芯片,所述控制芯片u2通过i2c总线电性连接至第二rtc芯片。

17.本实用新型的有益效果为:

18.本实用新型提供了一种双核心的域控制器,包括通过三条通信线路连接的第一核心与第二核心;其中两条通信线路为以太网线路和pcie线路,第一核心通过以太网线路以及pcie线路与第二核心连接,从而在一个核心为主核心,另一个核心为备用核心时,可以通过以太网线路以及pcie线路进行主核心的数据备份以及算力扩展,主核心失效时,则可以启用备用核心及其备份数据,保证域控制器的正常工作,提高域控制器的可靠性;第三条通信线路为通用数据传输线路,第一核心的gpio接口通过通用数据传输线路连接至第二核心的gpio,从而使得第一核心与第二核心之间可以相互发送心跳,以监控核心是否故障,进一步提高域控制器的可靠性。

附图说明

19.为了更清楚地说明本发明示例性实施方式的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

20.在附图中:

21.图1为本实用新型提供的一种双核心的域控制器的框图。

22.图2为本实用新型提供的一种双核心的域控制器的电路图。

具体实施方式

23.为使本实用新型的目的、技术方案和优点更加清楚明白,下面结合实施例和附图,对本实用新型作进一步的详细说明,本实用新型的示意性实施方式及其说明仅用于解释本实用新型,并不作为对本实用新型的限定。

24.下面结合附图详细说明本实用新型的实施例。

25.如图1所示,一种双核心的域控制器,包括第一核心以及第二核心,第一核心与第二核心通过三条通信线路电性连接;应当理解的是,本实施例中,第一核心也可称之为第一核心处理模块,第二核心也可称之为第二核心处理模块;第一条通信线路为以太网线路,第一核心通过以太网线路电性连接至第二核心;第二条通信线路为pcie(peripheral component interconnect express,高速串行计算机扩展总线标准)线路,第一核心的pcie接口通过pcie线路电性连接至第二核心的pcie接口;第三条通信线路为通用数据传输线路,第一核心的gpio接口通过通用数据传输线路电性连接至第二核心的gpio。

26.本实施例提供的域控制器,设置有第一核心和第二核心,在必要情况下,可以提供的算力的扩展,保障域控制的算力充足。其次,第一核心与第二核心之间设置高速通信的pcie线路以及低速通信的以太网线路,保障算力扩展时的信息交互。当算力充足时,设置的pcie线路还可以为第一核心与第二核心的相互备份提供高速信息交互,保证域控制器正常功能的同时,实现核心的数据备份,当一个核心损坏时,可以快速启动另一个核心,以保证域控制器的正常使用,提高域控制器的可靠性。除此之外,本实施例还提供了一条以太网线路为第一核心与第二核心之间提供低速备份通道,当高速备份通道出现损坏或者异常时,保证两个核心之间仍然可以正常进行数据交互。

27.最后,本实施例提供了一条通用数据传输线路,可以使两个核心之间相互发送和接收心跳脉冲信号,并接收心跳响应脉冲信号,从而实时监测是否有核心存在损坏。

28.如图2所示,第一核心包括型号为s32g274a的控制芯片u1,第二核心包括型号为s32g274a的控制芯片u2,控制芯片u1与控制芯片u2通过三条通信线路电性连接。

29.s32g274a芯片是nxp为适应整车电子电气架构的变革在2021年推出的高性能域控制器处理器,s32g274a芯片可以提供高达15900dmips的算力,相较于传统车载处理器算力提升了十几倍。为了在提升算力的同时满足实时性和功能安全等级要求,s32g274a采用异构架构(arm a53 linux+arm m7 rtos)相较于传统只支持一种架构的车载处理器具有更广阔的应用空间,便于实现平台化开发。

30.控制芯片u1的pcie接口通过pcie线路电性连接至控制芯片u2的pcie接口。

31.在一种可能的实施方式中,控制芯片u1的gpio1引脚与控制芯片u2的gpio1引脚电性连接,控制芯片u1的gpio2引脚与控制芯片u2的gpio2引脚电性连接,以形成通用数据传输线路。

32.可以以控制芯片u1的gpio1引脚与控制芯片u2的gpio1引脚之间的线路作为心跳脉冲信号发送线路/心跳响应脉冲信号发送线路,以控制芯片u1的gpio2引脚与控制芯片u2的gpio2引脚之间的线路作为心跳响应脉冲信号发送线路/心跳脉冲信号发送线路,从而进行心跳监测。

33.在一种可能的实施方式中,控制芯片u1的rgmii功能引脚上设置有4个均由型号为bcm89883的phy芯片u7构成的第一以太网接口,控制芯片u2的rgmii功能引脚上设置有4个

均由型号为bcm89883的phy芯片u14构成的第二以太网接口;任一第一以太网接口通过rj45接口与任一第二以太网接口电性连接,以形成千兆的以太网线路,即使在高速pcie线路出现故障时,也能够保证两个核心之间的信息交互,同时其他的以太网接口可以供其他器件与域控制器进行通信交互。

34.在一种可能的实施方式中,控制芯片u1的can功能引脚上设置有12个型号均为tja1043的can芯片u8,控制芯片u2的can功能引脚上设置有12个型号均为tja1043的can芯片u15,以提供多路can接口,方便连接其他外设电子器件。

35.在一种可能的实施方式中,控制芯片u1通过i2c总线与型号为vr5510的电源芯片u3电性连接,控制芯片u2通过i2c总线与型号为vr5510的电源芯片u10电性连接。

36.芯片vr5510是一款汽车级多输出电源管理芯片,主要用于网关、车内网络、域控制器、远程通信和v2x通信。该pmic芯片包括多种高效开关模式和线性电压调节器。vr5510提供了在debug模式下评估设备的方法,调试模式允许用户通过i2c接口访问otp寄存器集、修改寄存器和测试设备功能。在调试模式期间,所有调节器保持关闭状态。

37.在一种可能的实施方式中,控制芯片u1通过sdio总线电性连接至第一emmc存储器,控制芯片u1的ddr功能引脚上设置有第一lpddr4内存;控制芯片u2通过sdio总线电性连接至第二emmc存储器,控制芯片u2的ddr功能引脚上设置有第二lpddr4内存。从而为第一核心和第二核心提供数据存储空间以及运行所需的内存。

38.在一种可能的实施方式中,控制芯片u1通过spi总线电性连接至型号为xdsm3276的加密芯片u4,控制芯片u2通过spi总线电性连接至型号为xdsm3276的加密芯片u11,从而保证了信息的安全。

39.在一种可能的实施方式中,控制芯片u1通过uart总线分别电性连接至第一lin芯片u5和第二lin芯片u6,第一lin芯片u5和第二lin芯片u6所采用的型号均为tja1021;控制芯片u2通过uart总线分别电性连接至第三lin芯片u12和第四lin芯片u13,第一lin芯片u12和第二lin芯片u13所采用的型号均为tja1021。

40.在一种可能的实施方式中,控制芯片u1通过i2c总线电性连接至第一rtc芯片,控制芯片u2通过i2c总线电性连接至第二rtc芯片,通过设置rtc芯片以实现定时心跳监控功能。

41.此外,控制芯片u1上还设置有io扩展接口j1以及adc扩展接口j2,以方面数据的传输,控制芯片u2类似。

42.本实用新型的工作原理包括算力扩展原理、核心备份原理以及心跳监控原理。

43.算力扩展原理:在使用该域控制器时,可以以第一核心或者第二核心作为主核心,以另一核心作为备用核心,当主核心的算力不足时,可以将数据交互至备用核心中,以使备用核心进行数据处理,最后将结果返回,完成算力扩展。

44.核心备份原理:当算力充足时,通过pcie线路或者以太网线路进行数据备份。若主核心发生故障,既可以启用备用核心进行工作,由于备用核心具备主核心同样的算力,并且对主核心的数据进行了备份,因此可以快速从故障中恢复。值得说明的是,连接主核心的器件,也应当连接至备用核心,以保证备用核心启用时能够正常运行,或者备用核心连接主要器件,保证主要功能的同时(如电子换挡),还可以预留算力进行算力扩展。但是,在主核心正常工作时,备用核心不接受其他器件的信号,或者通过电子开关通道屏蔽其他器件的信

号,当备用核心启动后,再由其控制打开电子开关通道,以实现数据流转。

45.心跳监控原理为:以控制芯片u1的gpio1引脚与控制芯片u2的gpio1引脚之间的线路作为心跳脉冲信号发送线路/心跳响应脉冲信号发送线路,以控制芯片u1的gpio2引脚与控制芯片u2的gpio2引脚之间的线路作为心跳响应脉冲信号发送线路/心跳脉冲信号发送线路。一核心通过心跳脉冲信号发送线路定时发送心跳脉冲信号,当另一核心接收到心跳脉冲信号后,通过心跳响应脉冲信号发送线路反馈心跳响应脉冲信号,从而实现心跳监测。

46.以上所述的具体实施方式,对本实用新型的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本实用新型的具体实施方式而已,并不用于限定本实用新型的保护范围,凡在本实用新型的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1