宽电源范围的电荷泵电路的制作方法

本技术涉及电子电路及半导体、电源管理类芯片,具体涉及一种宽电源范围的电荷泵电路。

背景技术:

1、cmos低压差线性稳压器(ldo)是一个应用非常广泛的电路,根据功率管的类型,有nmos管和pmos管两种。和pmos功率管相比,nmos功率管的迁移率大,同样电流的情况下,面积比pmos功率小,但nmos有个缺陷,要求nmos的栅极比输出要大一个阈值电压,在低压差的应用情况下,要求nmos管的栅极电压要高于电源电压。因此,需要一个电荷泵电路来提升nmos管的栅极电压。

2、以5v应用的nmos ldo为例,输入电源电压要求1.2v到5.5v,为了适应这个应用场景,电荷泵选用的器件,必须是5v耐压的nmos,这类器件的阈值电压相对较高,给低压应用造成一定的困难,因此,有必要开发一种宽电源范围的电荷泵电路。

技术实现思路

1、本技术实施例提供一种宽电源范围的电荷泵电路,可以解决目前功率管的栅极电压低的技术问题。

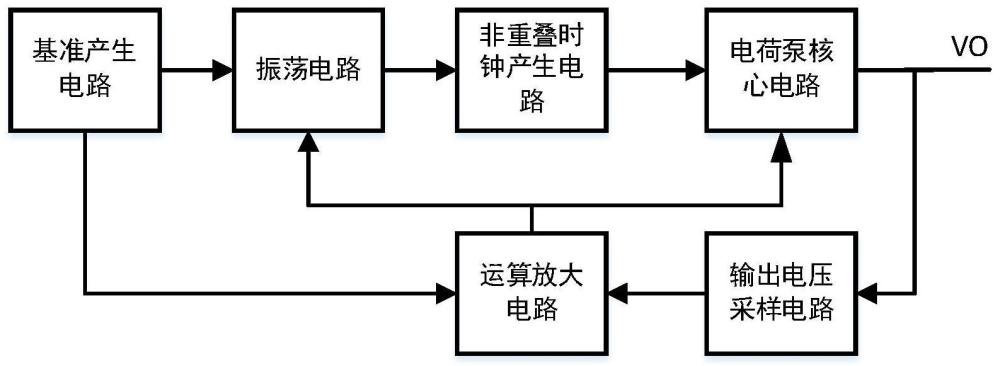

2、本技术实施例提供一种宽电源范围的电荷泵电路,包括基准产生电路、振荡电路、非重叠时钟产生电路、电荷泵核心电路、输出电压采样电路和运算放大电路;

3、所述基准产生电路连接至所述振荡电路及所述运算放大电路,所述振荡电路通过所述非重叠时钟产生电路连接至所述电荷泵核心电路,所述电荷泵核心电路输出输出电压且通过所述输出电压采样电路连接至所述运算放大电路,所述运算放大电路连接至所述振荡电路及所述电荷泵核心电路;

4、所述基准产生电路用来产生基准电压,作为所述振荡电路的参考电源,来控制所述振荡电路的震荡幅度和频率;

5、所述振荡电路产生的时钟信号,送入所述非重叠时钟产生电路,产生非重叠时钟信号,作为所述电荷泵核心电路的输入;

6、所述电荷泵核心电路输出的输出电压通过所述输出电压采样电路后产生采样电压,所述采样电压和所述基准电压作为所述运算放大电路的差分输入;

7、当所述采样电压大于所述基准电压时,表示所述电荷泵核心电路输出的输出电压已超过需要的电压范围,降低所述运算放大电路的输出来减少所述电荷泵核心电路的输入电压及时钟信号的幅度,以减小所述电荷泵核心电路输出的输出电压。

8、进一步的,所述电荷泵核心电路包括第一开关管m1、第二开关管m2、第三开关管m3、第四开关管m4、第五开关管m5、第六开关管m6、第七开关管m7、第八开关管m8、第九开关管m9、第十开关管m10、第十一开关管m11、第十二开关管m12、第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5、第六电容c6、第七电容c7;

9、输入电源vin连接至所述第一开关管m1的第一电极、所述第二开关管m2的第一电极,所述第一开关管m1的第二电极、所述第二开关管m2的栅极、所述第三开关管m3的第一电极、所述第四开关管m4的栅极连接至第一节点a,所述第一开关管m1的栅极、所述第二开关管m2的第二电极、所述第三开关管m3的栅极、所述第四开关管m4的第一电极连接至第二节点b,所述第三开关管m3的第二电极、所述第四开关管m4的第二电极连接至第三节点c;

10、所述非重叠时钟产生电路产生的非重叠时钟信号clk1和非重叠时钟信号clk3的交替开通,所述非重叠时钟信号clk1通过所述第一电容c1连接至第一节点a,所述非重叠时钟信号clk3通过所述第二电容c2连接至第二节点b;

11、所述第三节点c连接至所述第五开关管m5的第一电极、所述第六开关管m6的第一电极,所述第五开关管m5的第二电极、所述第六开关管m6的栅极、所述第七开关管m7的第一电极、所述第八开关管m8的栅极连接至第四节点d,所述第五开关管m5的栅极、所述第六开关管m6的第二电极、所述第七开关管m7的栅极、所述第八开关管m8的第一电极连接至第五节点e,所述第七开关管m7的第二电极、所述第八开关管m8的第二电极连接至第六节点f;

12、所述非重叠时钟产生电路产生的非重叠时钟信号clk2和非重叠时钟信号clk4的交替开通,所述非重叠时钟信号clk2通过所述第三电容c3连接至第四节点d,所述非重叠时钟信号clk4通过所述第四电容c4连接至第五节点e;

13、所述第六节点f连接至所述第九开关管m9的第一电极、所述第十开关管m10的第一电极,所述第九开关管m9的第二电极、所述第十开关管m10的栅极、所述第十一开关管m11的第一电极、所述第十二开关管m12的栅极连接至第七节点g,所述第九开关管m9的栅极、所述第十开关管m10的第二电极、所述第十一开关管m11的栅极、所述第十二开关管m12的第一电极连接至第八节点h,所述第十一开关管m11的第二电极、所述第十二开关管m12的第二电极连接至第九节点i;所述第九节点i输出输出电压v0;

14、所述非重叠时钟信号clk1通过所述第五电容c5连接至第七节点g,所述非重叠时钟信号clk3通过所述第六电容c6连接至第八节点h。

15、进一步的,所述电荷泵核心电路包括第七电容c7;所述第九节点i通过所述第七电容c7接地。

16、进一步的,所述振荡电路包括基准电路、充放电回路、整形器;

17、所述基准电路产生振荡电路所需的高门限电平vh、低门限电平vl;

18、所述充放电回路包括第一控制管mos1、第二控制管mos2、第三控制管mos3、第四控制管mos4、第五控制管mos5、第六控制管mos6及电容c0,所述第一控制管mos1的第一电极输入第一电压,所述第一控制管mos1的栅极连接至所述第一控制管mos1的第二电极及所述第二控制管mos2的栅极,所述第一控制管mos1的第二电极连接通过所述第三控制管mos3接地,所述第二控制管mos2的第一电极输入第二电压,所述第二控制管mos2的第二电极连接第九节点,所述第九节点通过所述电容c0接地,所述第九节点串联所述第六控制管mos6、所述第五控制管mos5并接地,所述第四控制管mos4的第一电极输入第一电流ib并连接至所述第四控制管mos4的栅极,所述第四控制管mos4的第二电极接地,所述第四控制管mos4的栅极连接至所述第三控制管mos3的栅极及所述第五控制管mos5的栅极。

19、进一步的,所述整形器包括第一比较器cmp1、第二比较器cmp2、第一rs触发器,所述第一比较器cmp1及所述第二比较器cmp2的基极连接至所述第一rs触发器,所述第一rs触发器连接至所述第六控制管mos6的栅极;所述第一比较器cmp1的阳极输入高门限电平vh,所述第一比较器cmp1的阴极连接至所述第二比较器cmp2的阳极和所述第九节点连接,所述第二比较器cmp2的阴极输入低门限电平vl。

20、进一步的,所述基准电路包括放大器、管mos0、电阻r1、电阻r2,基准电压vref输入至所述放大器的阳极,所述放大器的基极连接至所述管mos0的栅极,所述管mos0的第一电极输入第三电压,所述管mos0的第二电极输出高门限电平vh,所述管mos0的第二电极串联连接电阻r1、电阻r2并接地,所述电阻r1和所述电阻r2的连接点连接至所述放大器的阴极并输出低门限电平vl。

21、进一步的,所述第一rs触发器包括与非门nand1、与非门nand2、倒相器inv1、倒相器inv2、倒相器inv3、倒相器inv4;所述第一比较器cmp1的基极连接至所述与非门nand1的第一输入端,所述第二比较器cmp2的基极连接至所述与非门nand2的第二输入端,所述与非门nand1的输出端串联连接所述倒相器inv1、所述倒相器inv2并连接至所述第六控制管mos6的栅极,所述倒相器inv2的输出端输出时钟信号clk,所述倒相器inv2的输出端连接至所述与非门nand2的第一输入端,所述倒相器inv4的输出端连接至所述与非门nand1的第二输入端。

22、进一步的,所述基准产生电路包括第一分压电阻r01、第二分压电阻r02,电荷泵的输出电压pump串联连接所述第一分压电阻r01及所述第二分压电阻r02并接地,所述第一分压电阻r01及所述第二分压电阻r02的连接位置输出基准电压vref。

23、进一步的,所述基准产生电路还包括限幅电路,所述限幅电路包括第三比较器、控制开关管m0,所述第三比较器的正极连接至所述第一分压电阻r01及所述第二分压电阻r02的连接位置,所述第三比较器的阴极输出参考电压,所述三比较器的输出端连接至所述控制开关管m0的栅极,第四电压通过所述控制开关管m0输出输入电源vin。

24、进一步的,所述非重叠时钟产生电路包括第二rs触发器、倒相器inv5、倒相器inv6、倒相器inv7、倒相器inv8、倒相器inv9,所述第二rs触发器包括与非门nand3、与非门nand4、四个第一子倒相器、四个第二子倒相器;

25、时钟信号clk输入至所述与非门nand3的第一输入端及所述倒相器inv5的输入端,所述与非门nand3的输出端串联连接四个第一子倒相器作为第一输出端并连接至所述与非门nand4的第一输入端,所述倒相器inv5的输出端连接至所述与非门nand4的第二输入端,所述与非门nand4的输出端串联连接四个第二子倒相器作为第二输出端并连接至所述与非门nand3的第二输入端;所述第二rs触发器的第一输出端连接至所述倒相器inv6的输入端,所述倒相器inv6的输出端输出非重叠时钟信号clk1,所述倒相器inv6的输出端连接至所述倒相器inv7的输入端,所述倒相器inv7的输出端输出非重叠时钟信号clk2;所述第一rs触发器的第二输出端连接至所述倒相器inv8的输入端,所述倒相器inv8的输出端输出非重叠时钟信号clk3,所述倒相器inv8的输出端连接至所述倒相器inv9的输入端,所述倒相器inv9的输出端输出非重叠时钟信号clk4。

26、本技术实施例提供的宽电源范围的电荷泵电路,输出电压通过采样电路产生的电压和基准电压作为运算放大电路的差分输入,当采样电压大于基准电压时,表示电荷泵的输出已经超过需要的电压范围,运算放大电路的输出来减少电荷泵的输入电压及时钟信号的幅度,这种结构的优势是电荷泵输出电压的纹波相对较小。基准产生电路和振荡电路相结合,使振荡电路在宽电源范围可以正常工作,以提升功率管的栅极电压。

- 还没有人留言评论。精彩留言会获得点赞!