时序产生器、时序产生方法以及控制芯片与流程

1.本发明涉及时序信号的产生,尤涉及一种时序产生器、时序产生方法以及控制芯片,其能产生任意的数字信号波形。

背景技术:

2.目前能产生数字信号波形的方法有很多种,例如通过控制通用型输入输出(general-purpose input/output,gpio)、通过通用异步收发传输器(universal asynchronous receiver/transmitter,uart)等。然而,这些方法都存在各自的缺点。例如:通用型输入输出受限于硬件本身的精度,无法达到奈秒(nanosecond)级别的精度;此外,若有高精度的要求时,需要在禁用中断的情况下通过某类型的循环(例如特定指令诸如while等所控制的循环)不断切换状态,而这会大量地占用中央处理单元(central processing unit,cpu)的运算资源。又例如:通过通用异步收发传输器也有占用中央处理单元的运算资源的问题;此外,由于通用异步收发传输器本身的协议特性,其无法产生任意的数字信号波形。

3.因此,需要一种新颖的时序产生器以及时序产生方法,以在没有副作用或较不会带来副作用的情况下,解决相关技术的问题。

技术实现要素:

4.本发明的一目的在于提供一种时序产生器、时序产生方法以及控制芯片,以在不需占用大量运算资源的情况下产生任意的数字信号波形。

5.本发明至少一实施例提供一种时序产生器,其中该时序产生器包含一接收电路、耦接至该接收电路的一传送电路、以及分别耦接至该接收电路以及该传送电路的一控制单元。该接收电路可用来自一储存装置接收一个或多个时序数据组;该传送电路可用来依据该一个或多个时序数据组中的一个时序数据组选择多个信号类型中的一特定信号类型,并且以一特定时间长度输出具有该特定信号类型的一输出信号,其中该时序数据组指出该特定信号类型以及该特定时间长度;以及该控制单元可用来控制该接收电路以及该传送电路的运行。

6.本发明至少一实施例提供一种时序产生方法,其中该时序产生方法包含:利用一接收电路自一储存装置接收一个或多个时序数据组;以及利用一传送电路依据该一个或多个时序数据组中的一个时序数据组选择多个信号类型中的一特定信号类型,并且以一特定时间长度输出具有该特定信号类型的一输出信号,其中该时序数据组指出该特定信号类型以及该特定时间长度。另外,该接收电路以及该传送电路的运行是藉由利用一控制单元来控制。

7.本发明至少一实施例提供一种控制芯片,其中该控制芯片包含一储存装置、耦接至该储存装置的一时序产生器、以及耦接至该时序产生器的一处理电路。具体来说,该时序控制器可包含一接收电路、耦接至该接收电路的一传送电路、以及分别耦接至该接收电路

以及该传送电路的一控制单元。在该控制芯片的运行中,该储存装置可用来储存一个或多个时序数据组(例如一系列时序数据组),而该处理电路可用来传送至少一指令至该控制单元以控制该时序产生器的运行。在该时序产生器的运行中,该接收电路可用来自该储存装置接收该一个或多个时序数据组;该传送电路可用来依据该一个或多个时序数据组中的一个时序数据组选择多个信号类型中的一特定信号类型,并且以一特定时间长度输出具有该特定信号类型的一输出信号,其中该时序数据组指出该特定信号类型以及该特定时间长度;以及该控制单元可用来控制该接收电路以及该传送电路的运行。

8.本发明能自一储存装置读取一个或多个时序数据组(例如一系列时序数据组),再依据该一个或多个时序数据组中的一个时序数据组产生对应的数字信号。由于该数字信号是基于可任意编辑的该时序数据组来产生,因此本发明能通过修改该时序数据组来产生任意的数字信号波形,而不会大量地占用中央处理单元的运算资源。

附图说明

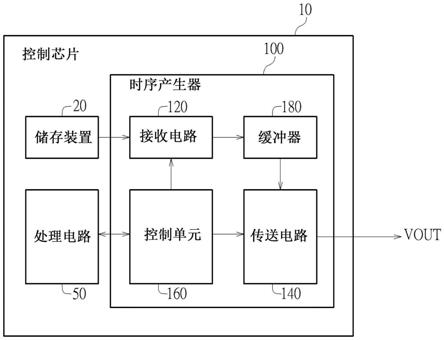

9.图1为依据本发明一实施例的一控制芯片的示意图。

10.图2为依据本发明一实施例的一时序数据组的示意图。

11.图3为依据本发明一实施例的图1所示的控制芯片的某些实施细节。

12.图4为依据本发明一实施例的一种时序产生方法的工作流程。

13.图5为依据本发明一实施例的因应一系列时序数据组产生的输出信号的示意图。

具体实施方式

14.图1为依据本发明一实施例的一控制芯片10的示意图。控制芯片10可包含一储存装置20、耦接至储存装置20的一时序产生器100、以及耦接至时序产生器100的一处理电路50,其中储存装置20可由使用双倍数据率(double data rate,ddr)技术的存储器诸如双倍数据率同步动态随机存取存储器(synchronous dynamic random access memory,sdram)来实施,而处理电路50可由一中央处理单元(central processing unit,cpu)来实施,但本发明不限于此。在本实施例中,时序产生器100可包含一接收电路120、耦接至接收电路120的一传送电路140、以及分别耦接至接收电路120以及传送电路140的一控制单元160。另外,时序产生器100可还包含耦接于接收电路120与传送电路140之间的一缓冲器180(例如,传送电路140是通过缓冲器180耦接至接收电路120)以缓冲自接收电路120传送至传送电路140的数据,其中缓冲器180可包含一先进先出(first input first output,fifo)存储器,但本发明不限于此。

15.在控制芯片10的运行中,储存装置20可用来储存一个或多个时序数据组(例如一系列时序数据组),而处理电路50可用来传送至少一指令至控制单元160以控制时序产生器100的运行。在时序产生器100的运行中,接收电路120可用来自储存装置20接收该一个或多个时序数据组(例如该系列时序数据组),例如,缓冲器180可自接收电路120接收该系列时序数据组,并且将该系列时序数据组中的每一时序数据组依序地传送至传送电路140;传送电路140可用来依据该一个或多个时序数据组(例如该系列时序数据组)中的一个时序数据组(例如该系列时序数据组中的每一时序数据组)选择多个信号类型中的一特定信号类型,并且以一特定时间长度输出具有该特定信号类型的一输出信号vout,其中该时序数据组指

出该特定信号类型以及该特定时间长度;以及控制单元160可用来控制接收电路120以及传送电路140的运行。

16.在本实施例中,该多个信号类型可至少包含脉冲宽度调制(pulse width modulation,pwm)、一第一固定电平、以及异于该第一固定电平的一第二固定电平中的一个或多者。另外,控制单元160可依据处理电路50传送的指令控制该脉冲宽度调制的一频率以及一工作周期(duty cycle)等设定,其中该脉冲宽度调制的该频率以及该工作周期可载有(carry)某些信息或依据某些设计需求来决定。

17.图2为依据本发明一实施例的一时序数据组200的示意图,其中时序数据组200可作为该时序数据组的一个例子,且时序数据组200可由32位的数据诸如数据{bit31,

…

,bit2,bit1,bit0}组成,但本发明不限于此。在本实施例中,时序数据组200可包含第一局部数据(例如数据{bit1,bit0})以及第二局部数据(例如数据{bit31,

…

,bit2}),而该第一局部数据以及该第二局部数据分别对应于该特定信号类型以及该特定时间长度。

18.图3为依据本发明一实施例的控制芯片10的某些实施细节。在本实施例中,传送电路140可包含多个信号源、耦接至该多个信号源的一传送控制电路142、以及耦接至该传送控制电路的一选择电路144(例如一多任务器(multiplexer))。该多个信号源可分别用来产生具有该多个信号类型的多个信号,例如用来产生脉冲宽度调制信号的脉冲宽度调制产生器146、用来产生具有该第一固定电平诸如电压电平vh的信号源(未显示)、以及用来产生具有该第二固定电平诸如电压电平vl的信号源(未显示)。传送控制电路142可用来以特定时间长度输出该多个信号的至少一者(例如依据图2所示的时序数据组200中的数据{bit31,

…

,bit2}产生具有对应的信号时间长度的信号),而选择电路144可用来依据该时序数据组选择该多个信号类型中的该特定信号类型(例如依据图2所示的时序数据组200中的数据{bit1,bit0}来决定输出哪一个信号源产生的信号)。

19.在本实施例中,当数据{bit1,bit0}为{0,0}(可表示为数值0)时,选择电路144可输出具有电压电平vl的信号;当数据{bit1,bit0}为{0,1}(可表示为数值1)时,选择电路144可输出具有电压电平vh的信号;而当数据{bit1,bit0}为{1,0}(可表示为数值2)时,选择电路144可输出脉冲宽度调制产生器146产生的信号。需注意的是,传送电路140的实施方式不限于图3所示的架构,凡是能依据自缓冲器180取得的时序数据组输出具有一特定时间长度及一特定信号类型的信号者,均隶属于本发明的范畴。例如,传送控制电路142可依据数据{bit1,bit0}(例如数据bit0)决定将具有电压电平vl与电压电平vh的其中一者的信号以一特定时间长度传送给选择电路144,而选择电路144再接着依据数据{bit1,bit0}(例如数据bit1)选择输出来自传送控制电路142的信号(例如具有电压电平vh及电压电平vl其中一者的信号)或来自脉冲宽度调制产生器146的信号;又例如,传送控制电路142可一并将具有电压电平vh及电压电平vl的信号分别以该特定时间长度传送至选择电路144,而选择电路144再接着依据数据{bit1,bit0}选择具有该特定时间长度及电压电平vh的信号、具有该特定时间长度及电压电平vl的信号、及脉冲宽度调制产生器146的信号的其中一者以供输出。

20.图4为依据本发明一实施例的一种时序产生方法的工作流程,其中该时序产生方法可应用于(applicable to)图1(或图3)所示的控制芯片10。若整体工作流程能得到相同或类似的结果,图4所示的工作流程中的一个或多个步骤的执行顺序可予以变化,或者,该

工作流程中的一个或多个步骤可被新增、删除、或修改。

21.在步骤410中,处理电路50通过控制单元160设定脉冲宽度调制产生器146的频率以及工作周期。

22.在步骤420中,处理电路50通过控制单元160设定时序数据组的实体地址与长度(例如一系列时序数据组中的时序数据组的数量)。

23.在步骤430中,处理电路通过控制单元160启用(enable)时序产生器100以开始产生信号。

24.在步骤440中,接收电路120自储存装置20中的该实体地址读取/接收一系列时序数据组,并且将该系列时序数据组传送至缓冲器180,此时i=1。

25.在步骤450中,传送控制电路142自缓冲器180读取/接收该系列时序数据组中的第i个时序数据组,其中该第i个时序数据组中的第一局部数据以及第二局部数据分别对应于一信号类型以及一时间长度。

26.在步骤460中,选择电路144可依据该第i个时序数据组中的该第一局部数据选择多个信号类型中的一特定信号类型,并且输出具有该特定信号类型的信号。例如,当图2所示的{bit1,bit0}为数值0时,选择电路144输出传送控制电路142产生的具有电压电平vl的信号;当图2所示的{bit1,bit0}为数值1时,选择电路144输出传送控制电路142产生的具有电压电平vh的信号;而当图2所示的{bit1,bit0}为数值2时,选择电路144输出脉冲宽度调制产生器146产生的信号。

27.在步骤470中,传送控制电路142可通过其内的一定时器开始计时,在输出信号的时间长度达到该第i个时序数据组中的第二局部数据所对应的时间长度时进入步骤480。

28.在步骤480中,传送控制电路142可判断信号是否已全部产生完毕(例如,该系列时序数据组中的全部的时序数据组所对应的信号是否均已产生完毕)。若是,进入步骤490;否则,i的数值增加1并且进入步骤450。

29.在步骤490中,控制单元160传送中断信号给处理电路50,流程结束。

30.在图4所示的实施例中,由于传送控制电路142可依据各个时序数据组中的第二局部数据所对应的时间长度决定下一个时序数据组的读取时间,因此可实现以特定时间长度(各个时序数据组中的第二局部数据所对应的时间长度)传送具有特定信号类型(各个时序数据组中的第一局部数据所对应的信号类型)的信号。

31.在某些实施例中,图1(或图3)所示的控制芯片10(例如其内的时序产生器)可应用于一红外线信号传送器,其中该特定信号类型在一时期内所占的一特定时间比例(例如,在一时期内时序产生器100可依序产生脉冲宽度调制信号以及具有固定电压电平诸如电压电平vl的信号,而该特定时间比例可由输出这个脉冲宽度调制信号的时间长度与输出这个具有电压电平vl的信号之间的比例推算得到)代表该红外线信号传送器在该时期所传送的编码后数据。以图5为例,该红外线信号传送器可依据一预定通信协议将逻辑值1编码为脉冲宽度调制信号在一时期内所占的一第一时间比例,例如在2.25毫秒(millisecond,简称为ms)中占有560微秒(microsecond,简称为μs);或者依据该预定通信协议将逻辑值0编码为脉冲宽度调制信号在一时期内所占的一第二时间比例,例如在1.12毫秒中占有560微秒。

32.总结来说,本发明利用读取一系列的可任意编辑的时序数据,以分别产生具有不同时间长度以及不同信号类型的输出信号,据以达到产生任意信号波形的目的。另外,相较

于相关技术,本发明的实施例不会占用大量的中央处理单元的运算资源。因此,本发明能在没有副作用或较不会带来副作用的情况下解决相关技术的问题。

33.以上所述仅为本发明的优选实施例,凡依本发明权利要求范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

34.【符号说明】

35.10 控制芯片

36.20 储存装置

37.50 处理电路

38.100 时序产生器

39.120 接收电路

40.140 传送电路

41.142 传送控制电路

42.144 选择电路

43.146 脉冲宽度调制产生器

44.160 控制单元

45.180 缓冲器

46.200 时序数据组

47.vout 输出信号

48.bit0、bit1、bit2、

…

、bit31 数据

49.410、420、430、440、450、460、470、480、490 步骤。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1