包括选择/差分阈值电压特征的非易失性存储器感测的系统和方法与流程

1.本案是申请号:201610837183.1,发明名称为:包括选择/差分阈值电压特征的非易失性存储器感测的系统和方法的分案申请。本发明涉及mos电路的阈值电压特性,并且更具体地涉及与诸如闪速存储器阵列中的那些的mos器件的差分阈值电压条件相关联的感测系统和方法。

背景技术:

2.常规mos系统和电路常常使用以指定阈值电压和饱和特性为特征的mos器件。此外,某些模拟信号处理系统、诸如与阵列感测有关的那些、通电电路、比较器、比率相关锁存、缓冲器驱动及其它电路常常具有诸如增强型裕度、增加的位线/漏泄控制等的需要,这与其mos器件特性紧密地相关联。例如,在闪速存储器中,用于感测操作的读出和放大电路可以作为此类阈值电压特性的函数进行操作以在存在于相关晶体管节点上的期望范围处或整个范围内保持线性操作。

3.此外,许多现有模拟闪速存储器系统包括以不能令人满意的操作点和裕度为特征的mos电路。

4.总而言之,需要一种可以通过例如提供差分阈值电压特性、改善电压操作裕度或其它电压条件和/或以其它方式致使性能更加稳健来提供充分的操作条件的感测系统和方法。

技术实现要素:

5.依照本文中的创新的感测系统和方法是针对经由具有差分阈值电压的mos器件来提供选择性阈值电压特性。

6.在一个示例性实施例中,提供了一种金属氧化物半导体器件,其包括具有源极区、漏极区和在其之间的沟道区、在沟道区之上的绝缘层以及绝缘层的栅极部分的半导体材料的衬底。此外,关于该器件,绝缘层的形状和/或结区的形状或注入具有在栅极至漏极与栅极至源极结之间的变化维度,以在其之间提供差分阈值电压。

7.应理解的是前述一般描述和以下详细描述是仅仅是示例性和说明性的,并且不限制本发明,如所述。除在本文中所阐述的那些之外,可以提供其它特征和/或变体。例如,本发明可以针对公开特征的各种组合和子组合和/或在以下详细描述中公开的多个其它特征的组合和子组合。

附图说明

8.构成本说明书的一部分的附图图示出本发明的各种实施例和方面并连同描述一起解释本发明的原理。在所述附图中:图1是常规感测系统的示意图。

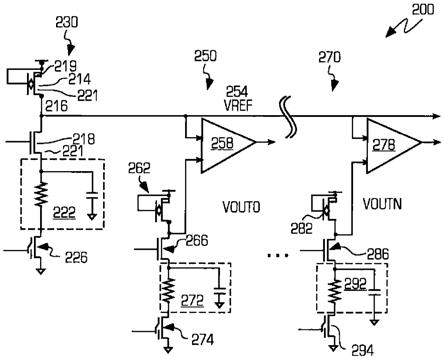

9.图2是图示出依照关于本创新的某些方面的示例性系统的示意图。

10.图3a和3b是图示出依照关于本创新的某些方面的示例性系统的示意图。

11.图4是图示出依照关于本创新的某些方面的示例性系统的示意图。

12.图5是图示出依照关于本创新的某些方面的示例性系统的示意图。

13.图6是图示出依照关于本创新的某些方面的示例性系统的示意图。

14.图7a和8a是图示出依照关于本创新的某些方面的示例性系统的示意图。

15.图7b和8b是图示出依照关于本创新的某些方面的示例性系统的性能特征/特性的图表。

16.图9是图示出依照关于本创新的某些方面的示例性系统的示意图。

17.图10a和10b是图示出依照关于本创新的某些方面的示例性系统的示意图。

18.图11a是依照关于本创新的某些方面的示例性器件的透视(侧视)图。

19.图11b是图示出依照关于本创新的某些方面的示例性器件的性能特征/特性的图表。

20.图12是依照关于本创新的某些方面的示例性器件的透视(侧视)图。

21.图13是依照关于本创新的某些方面的示例性器件的透视(顶视和侧视)图。

22.图14是图示出依照关于本创新的某些方面的示例性器件的性能特征/特性的图表。

23.图15是依照关于本创新的某些方面的示例性器件的透视(顶视)图。

24.图16是依照关于本创新的某些方面的示例性器件的透视(顶视)图。

25.图17是依照关于本创新的某些方面的示例性器件的透视(顶视)图。

具体实施方式

26.现在将详细地对本发明进行参考,其示例在附图中被图示出。在以下描述中阐述的实施方式不表示依照要求保护的发明的所有实施方式。替代地,其仅仅是依照关于本发明的某些方面的某些示例。只要可能,相同的附图标记将遍及各图用来指示相同或类似的部分。

27.在闪速存储器系统和方法的上下文内,可以经由对阈值电压条件敏感的布置来实现许多关联电路。特别地,此类布置的示例是差分感测放大器、通电电路、差分比较器、比率相关锁存器电路以及缓冲器驱动电路。这些布置可以用多种部件来实现,包括mos晶体管,并且可以包括利用此类mos晶体管的阈值条件的多种模拟电路和概念。关于此类mos晶体管的特定特征,基本构造和示例性制造方面对于本领域的技术人员来说是众所周知的。此类晶体管和关联制造特征的示例包括美国专利号5,045,488、6,258,645和6,329,685,其被整体地通过引用结合到本文中。

28.图1图示出常规系统100的方框图。参考图1,常规感测系统100包括基准列130、多个数据列,例如列0 150至列n 170,以及多个比较器158、178等。基准列130包括基准存储器存储单元126、mos晶体管118(级联晶体管)和二级管连接的mos晶体管114(上拉或负载晶体管)。位线rc部件122被示为指示位线上的电阻和电容。未示出的是ymux(例如位线选择电路),其可以是例如n:1 ymux(即包括n个mos晶体管,其使全部的n个漏极被链接在一起且n个源极连接到n个单独位线),其中,可以选择n个位线之中的1个,例如,n=16、64或512。在

某些示例性实施方式中,ymux可以与晶体管118和位线rc部件122级联,并且可以将ymux mos晶体管的栅极从解码器(未示出)中解码。对于基准列130而言,ymux通常仅充当假ymux(其栅极始终导通,通常被连接到vdd),因为通常仅存在一个基准单元126,因此不需要选择。晶体管118可以提供用于感测的级联功能,意味着通常通过在晶体管118的vblbias+vt下调制其栅极来在偏压vblbias(例如0.8~1.4v)下调节其源极,其中vt是其nmos阈值电压。晶体管118的漏极是关于感测的输出节点,其依照来自存储器存储单元126的单元电流的量值而变。晶体管118的级联功能用于将rc部件122从感测节点154隔离。基准列130在基准线上提供电压基准,vref、154,其被施加于比较器158至178中的每一个的第一输入端。每个数据列150至170可以包括数据存储器存储单元、mos晶体管和二极管连接的mos晶体管。另一位线rc部件表示位线上的电阻和电容。未示出数据列150~170的ymux。数据列150至170中的每一个向各比较器158至178的第二输入端提供数据输出电压v

out0

至v

outn

,从而使得比较器提供指示相应数据列中的所存储的数据的输出。

29.常规感测系统100具有非最佳操作,诸如源自于各种mos晶体管(例如,基准列130内的二极管连接的mos晶体管114)。诸如由于饱和区中的负载而引起的非线性操作的错误然后可以导致例如不能提供晶体管114单元饱和电流(icell

‑

sat)到输出信号(vout)的期望线性或近线性转换。依照本文所阐述的原理,诸如这样的缺陷以及对高度准确的性能的需求(诸如在动态读取中)转换成对用于晶体管和关联电路的操作参数的甚至更大改进的需要。

30.图2是图示出依照关于本创新的某些方面的实现差分mos晶体管的示例性系统200的示意图。参考图2,感测系统200包括基准列230、多个数据列,例如列0 250至列n 270,以及多个比较器258、278等。基准列230包括基准存储器存储单元226、差分阈值mos晶体管218(例如级联晶体管)以及二极管连接的差分阈值mos晶体管214(例如上拉、负载晶体管等),其可以是nmos或本位nmos晶体管,其中其栅极和漏极被连接在一起并充当用于基准列的输出电压节点(例如基准))。rc部件222被示为指示基准列上的电阻和电容。未示出与基准列230相关联的ymux。基准列230在基准线上提供电压基准,vref、254,其被施加于比较器258至278中的每一个的第一输入端。每个数据列250至270可以包括数据存储器存储单元274、294、mos(例如级联)晶体管266、286以及二极管连接的差分阈值nmos(例如上拉、负载等)晶体管262、282,其中栅极和漏极端子被连接在一起,并充当用于其各列的(例如数据)输出电压节点。还示出了位线rc部件272、292,表示位线上的电阻和电容。未示出数据列250~270的ymux,即分别从位线部件272、292和存储器存储单元274、294至晶体管266、286的耦合。数据列250至270中的每一个向各比较器258至278的第二输入端提供数据输出电压vout0至voutn,从而使得比较器提供指示相应数据列中的所存储的数据的输出。

31.示例性系统200的差分阈值mos晶体管214、262、282可以是被制造成使得漏极区/结构和源极区/结构之间的物理或电物理差跨漏极区产生与跨源极区的阈值电压vtns不同的阈值电压vtnd的晶体管。(在本文中,vtn指的是nmos晶体管的阈值电压vt,vtnd指的是跨漏极区的nmos的vt,并且vtns指的是跨源极区的nmos的vt。) 结合图11~17和关联的所写描述来阐述用来提供此类器件的结构和制造过程的某些示例性细节。返回至本图示,在没有本创新的情况下,示例性操作条件可以提供例如1.3伏的基准电压。(例如,假设当vdd=1.6v、vt=0.1、deltavgs(ids)=0.2、vref(或vout)=1.6

ꢀ‑ꢀ

0.3=1.3伏时,阈值mos晶体

管214(或262、282)=0.1v。) 然而,特别地,依照图2的示例性实施方式,可以将mos结构的物理性质/结构制造成改变在电压确定中涉及的差分阈值电压mos器件214、262、282的阈值电压/饱和特性。因此,关于基准电压,可以制造具有改善的阈值电压差分,即漏极阈值电压vtnd(例如0.1伏)和相应的源极阈值电压vtns(例如,0.0伏),其赋予与典型结构(即vtnd=0.1伏、vtns=0.1伏)相比的优点。用此类差分阈值mos器件,操作条件在更宽的(一个或多个)电压范围方面有所改善,例如,vref(或vout)=1.6

ꢀ‑ꢀ

0.0

ꢀ‑ꢀ

0.2=1.4伏,因此将该范围改善(加宽)0.1v。通常可以受益于此类创新的mos电路/器件包括但不限于具有对输出电压值/水平有所贡献的mos晶体管的那些、对偏移进行修整的那些以及基于其节点处的小电压摆动而向或从开/关状态进行过渡的那些。同样地,使得能够具有设置诸如vtnd和/或vtns的不同阈值电压的能力的创新使得能够具有类似于改善的位线操作的优点,并且下文详述其进一步示例。

32.图3a是图示出实现差分mos晶体管和/或以其它方式依照关于本创新的某些方面的示例性系统300的示意图。参考图3a,示例性感测系统300可以包括其中其栅极和漏极被连接在一起并充当输出电压节点的(上拉或负载)二级管连接的晶体管314(其可以与图2的nmos晶体管214类似地运行)、级联差分阈值晶体管318以及多个存储器列330、350、370。级联晶体管318可以受益于如下的差分阈值电压构造。为了保持晶体管318作为级联时的功能,其vds必须大于vgs小于vt(vds > vgs

ꢀ‑ꢀ

vt),意味着操作条件使得晶体管318处于饱和区中。例如,假设vt=0.2v、deltavgs(ids)=0.2、vs(晶体管318的源极处的电压=位线电压)=0.6v,则vgs=vs+vt+deltavgs(ids)= 0.6+0.2+0.2=1v。因此,vds > vgs

ꢀ‑ꢀ

vt=1v

ꢀ‑ꢀ

0.2v=0.8v。用差分阈值构造,例如vtnd=0.2v且vtns=0.1v,vgs=vs+vtns+delatvgs(ids)=0.6+0.1+0.2=0.9v,vds > vgs

ꢀ‑ꢀ

vtnd=0.9v

ꢀ‑ꢀ

0.2v=0.7v。因此,晶体管318的漏极电压可以在0.1v以下操作,而操作仍处于饱和条件。因此,其将操作电压范围改善(加宽)了0.1v。每个存储器列可以包括ymux、rc部件、存储器存储单元以及多个ymux晶体管320/324/328、340/344/348、360/364/368。此类ymux电路可以例如用来从8个位线中选择一个位线来连接到级联晶体管318和负载晶体管314。rc元件322被示为表示第一位线上的电阻和电容并被耦合到ymux 321。还可以将存储器存储单元326耦合到rc部件322。(本文所使用的存储器列指的是ymux、rc元件和存储器存储单元的此类组合。) 此外,可以将附加rc元件以及存储器存储单元连接到其它的七个位线bl [1:7]。具有差分(较高漏极)阈值电压的图3a中所图示出的布置可以具有开/关状态,其减少漏泄,即饱和或使电压从所选位线通过直至感测电路以使损耗最小化。参考图3a,当例如选择了第一示例性存储器列330时,差分阈值晶体管320、324将处于线性操作中,并使电压从位线(位线0)通过直至感测电路。此外,当示例性位线0未被选择时,晶体管328将晶体管320和324之间的节点上拉以在晶体管320上施加反偏压并将其关断。存储器列330、350至370中的每一个提供数据输出信号以使得能够提供指示相应的存储器列中的所存储的数据的输出。

[0033]

图3b是图示出实现差分mos晶体管和/或以其它方式依照关于本创新的某些方面的示例性系统380的示意图。参考图3b,示例性感测系统380可以包括其中其栅极和漏极被连接在一起并充当输出电压节点的(例如上拉、负载等)差分阈值pmos晶体管389、级联差分阈值nmos晶体管388和依照本文所阐述的那些的多个差分阈值nmos晶体管382、384和386。在这里,晶体管382、384、386可以例如是用来选择八个位线之中的位线以连接到(上拉、负

载)晶体管389的ymux 8:1的一部分。晶体管382、384和396可以是属于各存储器列的ymux电路的一部分,其中每个存储器列包括ymux、rc元件和存储器存储单元的晶体管。第一存储器列包括nmos晶体管382、rc元件322和所示存储器存储单元。其它存储器列包括晶体管384和386(作为ymux电路的一部分)、rc元件(未示出)和存储器存储单元(未示出)。此外,如上文所阐述的,示例性数据列可以包括晶体管389、级联晶体管388和多个存储器列。同样地,依照图3b的那个的感测系统可以利用跨源极的较高阈值电压vts例如来启用创新功能,诸如在图3a的情况下的改善的位线/漏泄控制、更宽的操作条件或电压范围和/或其它此类基于阈值的增强。例如,示例性晶体管388(其可以与图3a的晶体管318类似地运行)和389(其可以与图3a的晶体管314或图2的214类似地运行)可以具有较高的vtd以使得能够实现改善的数据输出线路电压,例如被改善至较宽的操作电压范围,并且晶体管382、384、386可以具有较高的vts以在较少漏泄的情况下将未被选择的位线关断。此外,晶体管382、384、386可以具有降低的漏极阈值电压以在较少延迟的情况下增强其电压通过功能。

[0034]

图4是图示出依照关于本创新的某些方面的示例性系统的示意图。参考图4,另一示例性感测系统可以包括差分感测放大器400,其包括基准列410和多个输出列440、460。(再次地,如图1和2的情况一样,未示出关联ymux电路。) 基准列410可以包括基准存储器存储单元432、其中其栅极和漏极被连接在一起并充当输出基准电压节点的二极管连接的差分阈值pmos(例如上拉、负载等)晶体管412以及附加基准列电路420,可以将其表征为具有例如至少一个差分阈值nmos(例如级联)晶体管422和表示基准列410或电路420上的电阻和电容的rc部件430。晶体管412和422可以分别与图3a的晶体管314和318类似地运行。基准列410设置refout线路上的电压基准416,其被供应给差分输入级440的输入端。差分输入级440的另一输入端dataout 452来自与具有数据存储器存储单元的基准列210类似的数据列(未示出)。输出列包括多种放大器电路和/或级以提供期望的输出,其可以包括一个或多个差分阈值mos(pmos/nmos)晶体管,诸如图4所示的示例性晶体管442、446、444、448、450、454、456。每个输出列可以提供指示在相应数据列中的所存储的数据的被相应地放大的输出电压,诸如saout、saoutb(参见例如447)等。在此图示中,此类说明性差分阈值电压mos晶体管的使用可以例如通过减小此类晶体管的总阈值电压来改善动态余量(即与晶体管422等相关联)。同样地,在具有大约0.2伏左右的阈值电压的典型nmos布置中,可以通过将总阈值电压从例如0.2减小至约0.1至0来改善性能。此类改善可以经由本文中的创新的利用来实现,例如使用差分阈值nmos晶体管422,其具有被固定以使源极阈值电压426偏移并提供约0.1至0的总有效阈值电压的较高漏极阈值电压424。关于感测操作,晶体管422可以充当类似于图2的晶体管218的级联晶体管,因此可以受益于与图3a的晶体管318的那个类似的差分阈值构造。同样地,可以以与图2的晶体管214一致的方式来实现晶体管412(例如上拉、负载等晶体管)的特征,其中vtd高于vts(例如约0.2v)以改善操作条件。同样地,可以使用与晶体管422的那个类似的输入对444和448。还可以以与晶体管412的那个类似的方式来实现晶体管442、446、454。此外,可以以与晶体管422的那个类似的方式来实现晶体管450、456。在这里,然后,此类特征导致放大器电路的(一个或多个)操作范围的全面改善。

[0035]

图5是图示出依照关于本创新的某些方面的示例性系统的示意图。参考图5,图示出了两个示例性阈值电压指示布置520、560。第一布置520图示出使得能够测量源极阈值电压vtns 530的示例性布置。为此,第一布置520可以包括源524、输入信号控制元件、跨其漏

极528被二极管连接的差分阈值mos晶体管522以及被接地的接收器(sink)526。经由输入信号控制元件的控制和将漏极和栅极置于相同的电压,可以经由用于晶体管522的总阈值电压的测量来获取源极阈值电压vtns的准确测量结果。同样地,图5还图示出使得能够测量漏极阈值电压vtnd 568的第二示例性布置560。为此,第二布置560可以包括源564、输入信号控制元件、跨其源极568被二极管连接的差分阈值mos晶体管562以及被接地的接收器566。经由输入信号控制元件的控制和将漏极和栅极置于相同的电压,可以经由用于晶体管562的总阈值电压的测量来获取漏极阈值电压vtnd 570的准确测量结果。

[0036]

图6是图示出依照关于本文中的创新的某些方面的示例性系统的示意图。图6图示出包括差分阈值mos晶体管612的差分通过门电路(differential pass gate circuit)600,其中例如漏极区608具有比源极610的阈值电压vtns高的漏极阈值电压vtnd。此类布置提供优点,例如当使高电压通过时(高电压将有效地促使高vt经由漏极引发的势垒(barrier)下降而下降)以及由于高vt区的存在而引起的更有效关断。

[0037]

图7是图示出依照关于本创新的某些方面的示例性系统的示意图。参考图7,图示出了上电复位系统700,其包括多个差分阈值mos晶体管704、734、744和输出节点746 vtrip。常规上电复位系统常常遭受缺点,即上电输出vtrip水平在低vdd下过高,因为其必须大于或等于例如完成电路的晶体管(即对应于将被二极管连接在常规电路中的晶体管704和晶体管744的晶体管)的阈值电压的和。然而,根据依照本文中的创新的方面,可以利用差分阈值电压mos晶体管704、734、744来在改善的操作裕度内操作输出vtrip。例如,第一差分晶体管704(当操作时在线性区中;并且未被二级管连接)可以被设置具有较高源极阈值电压714,并且一对输出晶体管734、744每个还可以包括被设置为高于其漏极阈值电压中的一个或两个或高于相应的常规上电系统中的相当(标准逻辑)晶体管的源极阈值电压738、748。此类布置使得能够在输出的上界vtrip处实现较低的“导通”值,因为输出高点(图8中的vtriph 766)只需要大于第一晶体管704的阈值电压vtp或跨输出端746与地线之间的输出晶体管744的现在较高源极阈值748的阈值电压以便使上电复位功能跳闸(trip)。换言之,当晶体管704、744导通时,实现高复位vtriph,其中设定点是其之间的较高阈值电压。同样地,经由对此输出有所贡献的晶体管的增加的源极阈值电压714、748的使用来改善操作范围。以这种方式,可以简单地在与此类晶体管相关联的最高阈值电压而不是阈值电压的和处使上电复位跳闸。在其它示例性实施方式中,可以用用于启用或禁用por、即用于测试以防止小故障的与非门对此类系统700进行“与”,以允许在小于por跳闸点(诸如用寄存器位或命令)等的值处进行读取。

[0038]

图7b是图示出根据关于本创新的某些方面的依照图7的示例性系统的性能特性的图表。参考图7b,示出了针对一定范围的vdd电压762进行绘图以图示出用于por vtriph 766的输出高点中的示例性波动的上电复位(“por”)水平768。在没有本文创新的益处的情况下,作为两个阈值电压的和的vtriph将过高而使得电路不能在低vdd(即作为接近于vtriph 766的电压)下适当地操作。然而,本创新使得vtriph能够在晶体管导通时实现其复位操作。同样地,可以使vtriph在两个阈值电压中的较高的一个处跳闸,使得例如能够在低vdd下实现改善的操作裕度。可以经由差分阈值mos晶体管来实现此功能。在其它实施方式中,可以将物理维度配置成实现由于源自于维度变化或效应(诸如由于短沟道效应、短宽度效应、反宽度效应、石相关效应(litho

‑

related effect)、井邻近效应、od(源极/漏极扩散

维度)等)的较高阈值电压而引起的较高跳闸点电压。例如,这可以经由对峰值周围的不同维度(宽度和长度)进行采样来实现,所述峰值诸如用于相关晶体管(在这里,诸如晶体管704和744)的阈值电压对比宽度、沟道长度或od(源极/漏极扩散维度)。

[0039]

图8a和8b是图示出依照图7a和7b的另一示例性电路/系统的示意性图表的图,但是反应在此类电路中的不同位置处具有变化阈值电压的不同方面(源极和/或漏极)。

[0040]

图9是图示出依照关于本创新的某些方面的示例性系统的示意图。参考图9,公开了包括mos器件差分对920、940的系统900。当使用依照本文中的创新的一个或多个低阈值电压晶体管来实现输出器件940时,可以实现改善的操作。根据某些示例性方面,可以经由多个mos晶体管来实现低阈值电压器件940,其中晶体管中的至少两个或多个具有不同的长度。例如,可以用如图16中所示的3个mos晶体管子部件来实现输出器件940,每个具有不同的长度,例如5/0.3、5/0.35、5/0.4等。可以经由不同的宽度来实现附加方面,并且可以经由差分阈值晶体管来实现其它方面,如上文所阐述的。根据其它方面,还可以用复合器件来实现输出器件,如下文所阐述的,以实现对于输出器件940而言所期望较低阈值电压参数。此类示例性实施方式还具有依照跨源极对阈值电压求平均值以使差分对的偏移最小化的总体优点。

[0041]

图10a和10b是图示出依照关于本创新的某些方面的示例性系统的示意图。参考图10a,公开了示例性系统1010,其包括多个晶体管1012、1014、1018及包括第一电路1022和第二电路1034的基于比率的锁存器件。系统1010图示出用以改善反馈相关操作裕度的差分阈值mos器件或晶体管的一个示例性使用。例如,系统1010示出了差分阈值mos晶体管1024、1036,其包括与其相应的漏极阈值电压不同(在本示例中,高于)(并因此高于标准晶体管的(一个或多个)阈值电压)以提供相关反馈和锁存操作的更好控制的源极阈值电压1026、1038。具体地,示例性系统1010使得能够经由用以根据电路输出来控制例如较早电路的锁存的差分阈值电压的使用来实现用于反馈操作的改善电压操作裕度(在这里,为改善的电压比或范围)。第二示例性电路1050示出了使用差分阈值电压来控制漏泄的第一和第二电路1052、1062的另一典型图示。在这里,例如,差分阈值mos晶体管1054、1064包括源极阈值电压1060、1066,其被设置成与其相应的漏极阈值电压不同(在本示例中,高于)(提供高于标准晶体管的(一个或多个)阈值电压)以提供开/关状态的更好控制以特别地减少漏泄。具体地,差分mos晶体管1054、1064将在比更高标准阈值电压晶体管少的过渡和延迟的情况下饱和或传递电压,从而使损耗最小化。具体地,两个mos晶体管1054、1064中的较高源极(和较低漏极)阈值电压1060、1066将提供较窄裕度内的开关、更紧缩的过渡范围和/或更少的漏泄。

[0042]

图11a是依照关于本文中的创新的某些方面的示例性mos晶体管器件的横截面图。此类器件的底层制造过程对于本领域的技术人员来说是众所周知的;这些过程的示例包括美国专利号5,045,488和6,258,645和6,329,685,其被整体地通过引用结合到本文中。如图11a的示例性器件中所示,mos晶体管1100可以包括第一导电性类型的半导体材料的衬底1110,诸如p衬底,该衬底包括源极和漏极区1144、1142。在所示的示例性器件中,源极和漏极区1144、1142可以包括第二导电性类型的区,诸如例如经由砷(as)注入过程提供的上n+掺杂区1144a、1144b、例如经由磷(p)注入过程提供的下n+掺杂区1142a、1142b。源极和漏极区1144、1142被相互间隔开,在其之间限定沟道区1140。绝缘层1120被设置在衬底的沟道区

之上,包括接近于第一源极/漏极区的第一绝缘部分1120a和接近于相对源极/漏极区的第二绝缘部分1120b。另外,栅极部分1130被设置在绝缘层之上。此外,沟道区1140包括相对结区,其包括邻近于一个源极/漏极区1144a、1142a的第一结区1160a和邻近于互补源极/漏极区1144b、1142b的第二结区1160b。mos晶体管还可以包括反转区1146。此外,根据依照本文中的创新的方面,第一结区1160a或第二结区1160b的形状或注入(即注入的类型或组成、注入的密度、注入的浓度和/或通过过渡区的变化等)中的一个或两个具有变化的维度以提供与结区相关联的第一阈值电压,其不同于与相对结区相关联的第二阈值电压。例如,包括该区的半导体材料可以具有与相对区不同的形状或尺寸以赋予此不同的阈值电压,注入可以是不同类型或组成的(用不同的离子/化合物、剂量、过程和角度等进行掺杂)、不同的密度/浓度、变化的尺寸、位置、强度或此类差别中的两个或更多的变化,和/或可以基于以上各项的组合来不同地设置阈值电压。

[0043]

在图11a所示的示例性器件中,可以经由较大补充注入物1148a的产生来在第一结区1150a处形成较高耗尽的区,诸如,例如硼(b)、其它halo材料等的p+注入物。虽然先前的注入已包括一般地被用来抑制短沟道效应的袋注入物的产生,但依照本创新的方面的补充注入物提供可应用于本文中公开的电路的特殊化势垒加载特征。同样地,可以基于上文所阐述的变化(诸如剂量和角度)经由此类漏极引发的势垒加载来将第一结区(例如漏极)的阈值电压设置成比相对结区的高(例如50mv~500mv等)。例如,还可以经由补充注入物来改变第一结区或第二结区的形状和注入中的一个或两个,以根据补充注入物来提供具有不同阈值电压的器件。同样地,可以经由一个或多个补充注入物来改变第一结区或第二结区的形状和/或注入,以根据一个或多个补充注入物来提供具有不同阈值电压的器件。

[0044]

图11b是图示出依照关于本创新的某些方面的示例性器件的示例性性能特征的图表。图表1150是漏极至源极电流ids 1122对比漏极至源极电压vds 1110的图表,其图示出具有此类示例性补充注入物的结的特性。图表1150描述了此类结的各种性能特性,例如,经由电流和电压之间的关系提供的较高rout,ids = i /(1 + λ)*vds。同样地,rout将随着1/ λ的斜率减小而成反比地增加,如一系列斜率1114、1116、1118所示,其图示出具有随着增加的掺杂而增加的增益(rout)。

[0045]

图12是依照关于本创新的某些方面的示例性器件的透视(侧视)图。图12的mos器件1200包括与图12的特征相同或类似的特征中的某些,但是图示出与氧化物或绝缘层相关联以便为与另一个相对的一个源极/漏极提供不同的阈值电压的某些特征。如图12的示例性器件中所示,mos晶体管1200可以包括第一导电性类型的半导体材料的衬底1210,诸如p衬底,该衬底包括源极和漏极区1244、1242。在所示的示例性器件中,源极和漏极区1244、1242可以包括第二导电性类型的区,诸如例如经由砷(as)注入过程提供的上n+掺杂区1244a、1244b、例如经由磷(p)注入过程提供的下n+掺杂区1242a、1242b。源极和漏极区1244、1242被相互间隔开,在其之间限定沟道区1240。氧化物/绝缘区1220被设置在衬底的沟道区之上。另外,栅极部分1230被设置在氧化物/绝缘区1220之上。此外,沟道区1240包括相对结区,其包括邻近于一个源极/漏极区1244a、1242a的第一结区1260a和邻近于互补源极/漏极区1244b、122b的第二结区1260b。mos晶体管还可以包括反转区1246。

[0046]

转到与氧化物/绝缘层相关联的特征,依照本文中的创新的示例性氧化物/绝缘区1220可以包括一个或多个氧化物或其它绝缘/电介质层1222以及氮化物层1224,其利用在

源极和漏极区处具有轨迹的氮化物电荷俘获(参见例如出于图示的目的在图12中示出的俘获电荷1226)来控制源极阈值电压vts和漏极阈值电压vtd。用于制造采用氮化物电荷俘获的器件的过程对于本领域的技术人员来说是众所周知的。特别地,在通过引用结合到本文中并随附于此的由william d. brown和joe brewer在1998年所编辑的nonvolatile semiconductor memory technology,ieee中阐述了此类器件和过程的某些示例(参见例如pp. 47~50,特别是第1.4.2.2节sonos器件pp. 49~50部分)。再次地,虽然出于图示的目的在图12中描述了俘获电荷1226,但还可以将电荷俘获的一个或多个区表征为邻近于源极或漏极以控制相应的阈值电压。此外,本示例是在氮化物的背景下描述的,可以以其它方式利用其它组成的电荷俘获区。同样地,虽然在层的背景下描述了本示例性电荷俘获区,但还可以使用材料的其它形状和布置。返回本创新,在本文所阐述的示例性系统中可以使用源极处的俘获电荷的轨迹或区的产生或源极阈值电压的操纵,包括但不限于修整比较器或运算放大器中的差分对的偏移。在本文所阐述的示例性系统中,还可以使用漏极处的俘获电荷的此类轨迹或区或漏极阈值电压的操纵,包括但不限于修整例如比较器或运算放大器中的差分对的漏极侧处的操作点。

[0047]

图13a和13b是依照关于本创新的某些方面的示例性器件的透视(顶视和侧视)图。图13a和13b中所示的示例性mos半导体器件1300可以包括第一导电性类型1310的半导体材料的衬底、衬底中的源极/漏极区1344,其中,源极区和漏极区是第二导电性类型的并被相互间隔开,在其之间定义了沟道区、设置在衬底的沟道区之上的绝缘层1322以及绝缘层之上的栅极部分。出于描述的目的,可以将绝缘层1322视为包括相对的绝缘区或“部分”,包括邻近于第一源极/漏极区的第一绝缘部分1322和邻近于相对源极/漏极区的第二绝缘部分1326,其中,每个绝缘部分定义或表征栅极与源极/漏极之间的与每个绝缘部分相关联的阈值电压。

[0048]

此外,根据依照本文中的创新的某些方面,可以用变化的维度(包括厚度1334)来制造第一绝缘部分或第二绝缘部分,以提供第一阈值电压,其不同于与相对绝缘部分相关联的第二阈值电压。在绝缘层中可以改变以实现这些优点的维度包括第一绝缘部分1324和第二绝缘部分1326的厚度1334以及宽度(跨沟道的距离或维度)1333、1331。在示例性系统中,其中此第二绝缘部分表示小于第一绝缘部分的厚度的氧化物区,可以减小宽度1331的线性维度以减小阈值电压,在功能上与耗尽区的维度变化类似,其可以对电压特性赋予变化。还可以经由第一和/或第二绝缘部分的宽度的(一个或多个)减小来实现阈值电压减小。此外,用于第二绝缘部分1326的较厚氧化物的使用将导致跨关联(相邻)源极/漏极的较高阈值电压。还可以将氧化物尺寸确定表征为采取总体绝缘层1322中的偏移区或偏移1336的形式。例如,该偏移可以是由诸如源极/漏极区(期望差分阈值电压)上的基本上直线的形状定义的区。根据某些示例性方面,依照上述内容的尺寸标注可以在源极与漏极之间赋予大约0.1伏至大约0.5伏左右的差分阈值电压条件。

[0049]

图14是图示出依照关于本创新的某些方面的示例性器件的性能特征/特性的图表。图14的图表1400是用于诸如图13中所示的mos晶体管的示例性器件的阈值电压1462对比长度1464的示例性图表。图表1400帮助图示出随着其长度1331维度变化而与例如第二绝缘部分1326相关联的阈值电压之间的典型关系。如所示,当长度维度在其较小范围内(特别地经由线lmin 1471来表征)时,用正斜率的曲线或随着长度增加而增加的阈值电压(也称

为sce或短沟道效应)来表征电压对比长度的图表。然而,随着长度增加超过某个阈值1472,该关系具有负斜率,阈值电压随着长度进一步增加而开始减小1476(也称为rsce或反短沟道效应点1474)。基于这些特性,可以根据设计和制造参数来确立和移动最大阈值电压,并且可以根据短长度特性来确定或确立最小阈值电压。例如,这些特征向诸如要求差分对的偏移的那些应用提供优点,尤其是在其中可以根据短长度和最小阈值电压特性来确定设计、制造和操作特征的情况下。关于依照本文中的创新的示例性器件的窄宽度效应和反窄宽度效应,存在类似的关系和优点。

[0050]

图15是依照关于本创新的某些方面的示例性器件的透视(顶视)图。参考图15,示出了包括具有源极/漏极区以及变化维度的氧化物区1530的衬底1510的复合器件1500。依照此类示例性方面,金属氧化物半导体器件可以包括第一导电性类型的半导体材料的衬底1510、在衬底中的源极区和漏极区,其中,源极区和漏极区具有第二导电性类型并被相互间隔开而在其之间限定沟道区、设置在衬底的沟道区上的绝缘层1530以及在绝缘层之上的栅极部分。可以将氧化物区1530表征为具有与上文所阐述的那些类似的第一和第二部分或“绝缘部分”,每个与互补源极和漏极区相关联。在图15的示例性图示中,第一绝缘部分或第二绝缘部分被制造成具有变化的长度和宽度并具有与相对绝缘部分不同的维度,以提供第一阈值电压,其不同于与相对绝缘部分相关联的第二阈值电压。在图15中,为了图示出作为维度的函数的不同阈值电压的产生,示出了具有不同宽度(即跨沟道距离)的3个部分1550、1554、1558的示例性氧化物区1530。还可以用反映与每个区的不同长度和宽度相比的变化的过渡区1552、1556来表征这些部分中的每一个。关于所图示出的示例性器件,然后通常将用不同的阈值电压来表征3个总体区中的每一个,用于每个源极或每个漏极的总体或复合阈值电压是作为每个阈值电压子分量确定的。

[0051]

图16是依照关于本创新的某些方面的示例性器件的透视(顶视)图。参考图16,示出了包括具有源极/漏极区以及变化长度的氧化物区1630的衬底1610的串联器件1600。依照此类示例性方面,金属氧化物半导体器件可以包括被串联地电布置的两个或更多晶体管子部件,每个晶体管子部件包括第一导电性类型的半导体材料的衬底1610、衬底中的源极区和漏极区,其中,源极区和漏极区是第二导电性类型的且被相互间隔开而在其之间定义沟道区、设置在衬底的沟道区之上的一个或多个绝缘层1630,每个具有位于绝缘层上的栅极部分。图16的图示描绘了3个晶体管子部件,虽然具有两个或具有超过3个的实施例也可以是依照本文中的创新。如所示,示例性mos器件1600包括第一晶体管子部件的第一氧化物区1632(“第一绝缘部分”)、第二晶体管子部件的第二氧化物区1634(“第二绝缘部分”)以及第三晶体管子部件的第三氧化物区1636(“第三绝缘部分”)。例如可以将具有两个晶体管元件的结构表征为使第一晶体管的第一绝缘部分被制造成具有与第二晶体管子部件的第二绝缘部分的第二长度不同的第一长度(即跨第一沟道的距离)。被相互以此类串联关系放置的氧化物区定义了用于每个子部件的各种阈值电压,其中最高阈值电压确定器件的总体或复合阈值电压,并且可以从而提供与器件的第二阈值电压不同的器件的第一阈值电压。以类似方式,具有三个或更多晶体管元件的结构可以在全部的各种晶体管氧化物区之间包括类似的关系。

[0052]

图17是依照关于本创新的某些方面的示例性器件的透视(顶视)图。参考图17,示出了包括具有源极/漏极区以及变化维度的氧化物区1768的衬底1710的复合器件1700。依

照此类示例性方面,金属氧化物半导体器件可以包括第一导电性类型的半导体材料的衬底1710、在衬底中的源极区和漏极区,其中,源极区和漏极区具有第二导电性类型并被相互间隔开而在其之间限定沟道区、设置在衬底的沟道区上的绝缘层1768以及在绝缘层之上的栅极部分。可以将氧化物区1768表征为具有与上文所阐述的那些类似的第一和第二部分或“绝缘部分”,每个与互补源极和漏极区相关联。如在图17的图示中以示例的方式所示,第一绝缘部分或第二绝缘部分被制造成具有变化长度和/或与相对绝缘部分不同的沿长度方向的表面面积或体积维度,以提供第一阈值电压,其不同于与相对绝缘部分相关联的第二阈值电压。在图17中,为了图示出作为此类长度尺寸变化的函数的不同阈值电压的一个示例性实施方式,可以通过延长或缩短邻近于源极/漏极的氧化层的两个长度尺寸l1、l2来在邻近于源极或漏极区的一侧或绝缘部分1770上改变示例性氧化物区1768。然后通常将用不同的阈值电压来表征两个不同的绝缘部分,在沟道的每侧上一个。

[0053]

应理解的是先前的描述意图举例说明而不是限制本发明的范围,其是由所附权利要求的范围来定义的。其它实施例在以下权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1