一种半导体存储器及其上存储块的容量配置方法与流程

1.本技术涉及半导体技术领域,涉及但不限于一种半导体存储器及其上存储块的容量配置方法。

背景技术:

2.相关技术中,为了同一款芯片实现不同的容量,可以采用一组修剪(trim)命令,使整个芯片(chip)上所有存储块(bank)的相同存储区域(存储阵列(array))被修剪掉,以得到不同容量。

3.由于不同的存储块,损坏的存储阵列完全有可能是不一样的,而为了利用只坏掉部分存储阵列的芯片,对整个芯片都选取相同的存储阵列进行修剪的方法,存在明显的缺陷,对半导体存储器上存储块的容量配置的有效利用率较低。

技术实现要素:

4.有鉴于此,本技术实施例提供一种半导体存储器及其上存储块的容量配置方法,能够灵活选取待修剪的存储区域,提升对半导体存储器上存储块的容量配置的有效利用率。

5.第一方面,本技术实施例提供一种半导体存储器上存储块的容量配置方法,所述方法包括:

6.确定所述存储器上的待配置的目标存储块;

7.确定所述目标存储块的容量配置参数,所述容量配置参数用于表征所述目标存储块的待配置容量;

8.基于所述目标存储块的容量配置参数,从所述目标存储块的一组编码中,确定目标编码;所述目标编码对应所述目标存储块中待修剪的存储区域;

9.基于所述目标编码,生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号;

10.基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置。

11.第二方面,本技术实施例提供一种半导体存储器,所述半导体存储器包括:

12.目标存储块,包括至少两个存储区域;

13.地址处理单元,用于输出所述目标存储块的地址;所述地址处理单元的输出端连接所述目标存储块;

14.编码获取单元,用于接收目标编码,所述目标编码对应所述目标存储块中的至少一个待修剪的存储区域;

15.区域选择信号生成单元,用于基于所述目标编码,生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号;所述区域选择信号生成单元的输出端连接修剪单元的输入端;

16.所述修剪单元,用于基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置;所述修剪单元的输出端连接所述目标存储块。

17.本技术实施例中,由于对于不同待配置的目标存储块的容量配置参数可以是不同的,基于不同的容量配置参数所确定的目标编码也可以不同,进而基于不同的目标编码所生成的区域选择信号也不同。如此,通过不同的区域选择信号,可以实现对不同待配置的目标存储块的不同待修剪的存储区域进行修剪;进而,能够灵活选取待修剪的存储区域,提升对半导体存储器上存储块的容量配置的有效利用率。

附图说明

18.在附图(其不一定是按比例绘制的)中,相似的附图标记可在不同的视图中描述相似的部件。具有不同字母后缀的相似附图标记可表示相似部件的不同示例。附图以示例而非限制的方式大体示出了本文中所讨论的各个实施例。

19.图1为相关技术中动态随机存取存储器(dynamic random access memory,dram)的组成结构示意图;

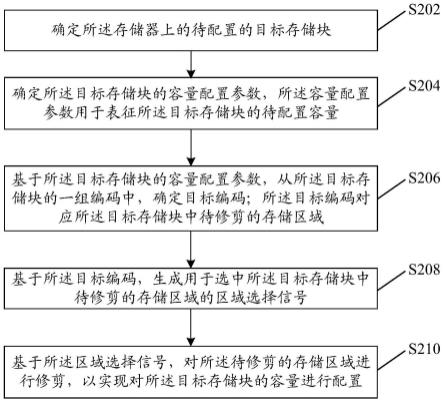

20.图2为本技术实施例提供的一种半导体存储器上存储块的容量配置方法的实现流程框图;

21.图3a为本技术实施例提供的一种全芯片存储区域和地址的结构示意图;

22.图3b为本技术实施例提供的对图3a中的存储块8进行放大后所展现的结构示意图;

23.图3c为本技术实施例提供的对存储块8进行修剪后的结构示意图;

24.图3d为本技术实施例提供的一种对目标编码进行逻辑非运算的逻辑电路图;

25.图3e为本技术实施例提供的一种对ra《15:14》进行逻辑非运算的逻辑电路图;

26.图3f为本技术实施例提供的一种对densitytrim《0》和densitytrim《1》进行逻辑运算的逻辑电路图;

27.图3g为本技术实施例提供的对densitytrimb《0》和densitytrimb《1》进行逻辑运算的逻辑电路图;

28.图3h为本技术实施例提供的通过目标编码和高两位元地址得到区域选择信号ra1514《0》的逻辑电路图;

29.图3i为本技术实施例提供的通过目标编码和高两位元地址得到区域选择信号ra1514《1》的逻辑电路图;

30.图3j为本技术实施例提供的通过目标编码和高两位元地址得到区域选择信号ra1514《2》的逻辑电路图;

31.图4为本技术实施例提供的一种适用于对半导体存储器上存储块的容量进行配置的系统结构图;

32.图5为本技术实施例提供的一种半导体存储器的结构示意图。

具体实施方式

33.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对发明的具体技术方案做进一步详细描述。以下实施例用于说明本技术,但不用

来限制本技术的范围。

34.在后续的描述中,使用用于表示元件的诸如“模块”或“单元”的后缀仅为了有利于本技术的说明,其本身没有特定的意义。因此,“模块”或“单元”可以混合地使用。

35.相关技术中,由于存储芯片的每套掩膜的费用很高,同时为了快速占领市场,往往在一款芯片的设计中用trim实现不同的容量。在实际生产中还会遇到有一部分的芯片只坏掉了部分的存储阵列,这时可以把这部分的芯片用作低容量的芯片来出售,达到增加良率的目的,比如,8兆比特(gigabit,gb)的芯片可以当作4gb/2gb的芯片来使用。同一款芯片实现不同的容量,通常的做法是用一组trim,使整个芯片所有存储块选取相同的存储阵列进行trim。这种实现方法设计上比较简单,但是不够灵活。为了利用只坏掉部分存储阵列的那部分芯片,整个芯片所有存储块都选取相同存储阵列的做法,显然是有缺陷的,因为不同的存储块,损坏的存储阵列完全有可能是不一样的。

36.可以理解的是,存储块是指动态随机存储器中包含的物理存储体或逻辑存储库的数量,一个芯片中可以包含多个存储块,例如,可以包含8个存储块;每一存储块中可以包含多个存储阵列,存储块中存储阵列的数量代表芯片的数据位宽;一个存储阵列里面包含多个存储单元。

37.在一种可能的实施方式中,半导体存储器可以是dram。图1为相关技术中dram的组成结构示意图,如图1所示,控制器10控制两个多个双列直插式存储模块(dual-inline-memory-modules,dimm)101,每一dimm 101上包括至少两个dram颗粒(die)1011。

38.基于上述技术问题,本技术实施例提供了一种半导体存储器上存储块的容量配置方法,如图2所示,所述方法包括以下步骤:

39.步骤s202:确定所述存储器上的待配置的目标存储块;

40.可以理解的是,存储器可以是指单片存储容量已进入兆位级水平的dram或支持trim功能的其它半导体存储器;目标存储块可以是存储器上的任意一个待配置的存储块。在一个示例中,bank可以是存储块的一种实现方式。以包含16个bank的芯片为例来进行说明,在16个bank分别为bank0至bank15的情况下,目标存储块可以是bank0至bank15中的任一个,例如,目标存储块可以是bank8或bank0。

41.在一些可能的实施方式中,确定所述存储器上的待配置的目标存储块,可以是在需要对存储器上的每一存储块进行配置的情况下,将存储器上的每一存储块确定为待配置的目标存储块。

42.在一些实施例中,目标存储块的容量是根据存储器的芯片的容量所确定的。例如,对于16gb包含16个bank的芯片而言,每一bank的容量是1gb,即,目标存储块的容量也是1gb。

43.步骤s204:确定所述目标存储块的容量配置参数,所述容量配置参数用于表征所述目标存储块的待配置容量;

44.在一些可能的实施方式中,目标存储块的容量配置参数可以包括以下至少之一:目标存储块的目标容量、目标存储块中待修剪的存储区域、目标存储块中可利用的存储区域。

45.可以理解的是,存储区域可以是存储阵列的一种实现方式,当然,存储区域也可以用region表示,例如,每一bank可以被分成region《5:0》6个区域,region《5》可以是其中的

一个存储区域。

46.在一个示例中,目标存储块bank8在未损坏也未被修剪的情况下的容量可以是1gb,bank8的目标容量可以是小于等于1gb的容量,例如,目标容量可以是(1/8)gb、(1/4)gb、(1/2)gb、(2/3)gb等。如此,可以存在以下两种情况:

47.情况1:bank8包括region《5:0》6个区域,且未发生损坏,但为了满足需求需要将1gb的容量改变为目标容量(2/3)gb,可以将region《5:0》中的region《3:2》、region《1:0》和region《5:4》中的任一存储区域确定为目标存储块bank8中待修剪的存储区域,而由于bank8未发生损坏,因此可以将所有的存储区域作为目标存储块中可利用的存储区域。

48.可以看出,在目标存储块未发生损坏的情况下,仅需要确定目标存储块的目标容量,就可以存在3种实现容量配置的方法。

49.情况2:bank8包括region《5:0》6个区域,且region《1:0》发生损坏,但为了满足需求需要将1gb的容量改变为目标容量(2/3)gb,可以将region《5:0》中的region《1:0》存储区域确定为目标存储块bank8中待修剪的存储区域,将对应的剩余区域region《5:2》作为目标存储块中可利用的存储区域。当然,在需求为将1gb的容量改变为目标容量(1/3)gb时,目标存储块中可利用的存储区域对应的可以是region《3:2》,可以在将region《1:0》和region《5:4》存储区域确定为目标存储块bank8中待修剪的存储区域。

50.可以看出,在目标存储块未发生损坏的情况下,可以将对应的剩余区域作为目标存储块中可利用的存储区域,且需要同时根据确定的目标存储块的目标容量,将包含损坏区域的存储区域确定为待修剪的存储区域。

51.对于确定所述目标存储块的容量配置参数的实现方式,可以是根据目标存储块的损坏信息、目标存储块的容量配置需求确定目标存储块的容量配置参数。

52.步骤s206:基于所述目标存储块的容量配置参数,从所述目标存储块的一组编码中,确定目标编码;所述目标编码对应所述目标存储块中待修剪的存储区域;

53.可以理解的是,目标存储块的一组编码可以是表示目标存储块的存储区域中不同待修剪的存储区域的编码。例如,目标存储块的一组编码可以表示为trim_halfgoodbnk《1:0》或density《1:0》,其中,trim_halfgoodbnk《1:0》或density《1:0》可以分别为00,01,10,11,trim_halfgoodbnk《1:0》=00,可以表示目标存储块bank8的存储区域region《5:0》中不存在待修剪的存储区域的情况;trim_halfgoodbnk《1:0》=01,可以表示目标存储块bank8的存储区域region《5:0》中的待修剪的存储区域region《5:4》;trim_halfgoodbnk《1:0》=10,可以表示目标存储块bank8的存储区域region《5:0》中的待修剪的存储区域region《3:2》;trim_halfgoodbnk《1:0》=11,可以表示目标存储块bank8的存储区域region《5:0》中的待修剪的存储区域region《1:0》。

54.在一个示例中,目标编码是根据目标存储块中待修剪的存储区域所确定的,例如,在待修剪的存储区域是region《3:2》的情况下,目标编码可以是10。

55.在一种可能的实施方式中,基于所述目标存储块的容量配置参数,从所述目标存储块的一组编码中,确定目标编码,可以是在确定目标存储块未发生损坏的情况下,根据目标存储块的目标容量,从所述目标存储块的一组编码中,确定和目标容量相对应的任一待修剪的存储区域对应的目标编码。

56.例如,对于未发生损坏的目标存储块bank8,在未损坏的情况下的bank8的容量可

以是1gb,包括region《5:0》6个区域;在目标容量为(2/3)g、trim_halfgoodbnk《1:0》或density《1:0》分别为00、01、10、11,且表示不同的待修剪存储区域的情况下,可以从rim_halfgoodbnk《1:0》或density《1:0》的一组编码中挑选表示(2/3)g的任一编码作为目标编码,因此,目标编码可以是01、10或11中的任意一个。

57.在另一种可能的实施方式中,基于所述目标存储块的容量配置参数,从所述目标存储块的一组编码中,确定目标编码,可以是在确定目标存储块发生损坏的情况下,根据损坏的存储区域和目标容量,确定待修剪的存储区域和可利用的存储区域,根据待修剪的存储区域和可利用的存储区域从目标存储块的一组编码中,确定目标编码。可以理解的是,在目标容量和损坏的存储区域的容量之和等于目标存储块未损坏时的容量的情况下,所确定的目标编码是唯一的。

58.例如,对于目标存储块bank8在未损坏的情况下,目标存储块bank8的容量可以是1gb,包括region《5:0》6个区域;在region《5:4》存储区域发生损坏,且目标容量为(2/3)g、trim_halfgoodbnk《1:0》或density《1:0》分别为00、01、10、11,且表示不同的待修剪存储区域的情况下,可以将trim_halfgoodbnk《1:0》或density《1:0》的一组编码中挑选表示待修剪存储区域region《5:4》的编码作为目标编码,因此,目标编码是唯一的01。

59.步骤s208:基于所述目标编码,生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号;

60.可以理解的是,区域选择信号是对目标编码进行逻辑运算后所得到的目标输出电平。

61.步骤s210:基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置。

62.可以理解的是,修剪存储区域可以通过改变存储区域的逻辑电平来实现;例如,存储区域在未修剪前的电平可以是低电平,将存储区域的电平由低电平转换为高电平后,可以将存储区域修剪掉。

63.在一种可能的实施方式中,基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置,可以是根据区域选择信号,确定对待修剪的存储区域施加高压(高电平),对目标存储块中除待修剪的存储区域外的其它存储区域施加低压(低电平),以改变待修剪的存储区域的逻辑电平,将待修剪的存储区域修剪掉,实现对所述目标存储块的容量进行配置。

64.本技术实施例中,由于对于不同待配置的目标存储块的容量配置参数可以是不同的,基于不同的容量配置参数所确定的目标编码也可以不同,进而基于不同的目标编码所生成的区域选择信号也不同。如此,通过不同的区域选择信号,可以实现对不同待配置的目标存储块的不同待修剪的存储区域进行修剪;进而,能够灵活选取待修剪的存储区域,提升对半导体存储器上存储块的容量配置的有效利用率。

65.本技术实施例提供了还一种半导体存储器上存储块的容量配置方法,所述方法包括以下步骤:

66.步骤101:确定所述存储器上的待配置的目标存储块;

67.步骤103:确定所述目标存储块的容量配置参数,所述容量配置参数用于表征所述目标存储块的待配置容量;

68.步骤105:在所述目标存储块的容量配置参数包括所述目标存储块中待修剪的存储区域,或所述目标存储块中可利用的存储区域的情况下,基于所述待修剪的存储区域或所述可利用的存储区域,确定所述待修剪的存储区域;

69.可以理解的是,可利用的存储区域可以理解为目标存储块中除待修剪的存储区域之外的存储区域。

70.在一些可能的实施方式中,基于所述待修剪的存储区域或所述可利用的存储区域,确定所述待修剪的存储区域,可以是首先确定目标存储块中的损坏区域,根据损坏区域确定可利用的存储区域,进而确定待修剪的存储区域。

71.在一个示例中,对于目标存储块bank8的容量可以是1gb,包括region《5:0》6个区域,在目标容量为8gb,且对应region《5:4》存储区域发生损坏的情况下,可以确定待修剪的存储区域为region《5:4》;在目标容量为4gb,且对应region《5:4》存储区域发生损坏的情况下,可以确定待修剪的存储区域为region《5:2》或region《1:0》和region《5:4》。

72.步骤107:基于所述待修剪的存储区域,从所述目标存储块的一组编码中,确定目标编码;其中,所述目标存储块的一组编码中每一编码对应于所述目标存储块中的至少一个待修剪的存储区域;

73.在一种可能的实施方式中,基于所述待修剪的存储区域,从所述目标存储块的一组编码中,确定目标编码,可以是无论目标存储块是否发生损坏,均根据待修剪的存储区域,从所述目标存储块的一组编码中,确定与所述待修剪的存储区域相对应的编码。例如,在确定待修剪的存储区域为region《5:4》的情况下,将region《5:4》对应的编码01确定为目标编码。

74.步骤109:在所述目标存储块的容量配置参数包括所述目标存储块的目标容量的情况下,从所述目标存储块的一组编码中,确定与所述目标存储块的容量配置参数对应的多个编码;

75.可以理解的是,在目标存储块的存储区域未发生损坏的情况下,可直接根据目标存储块的目标容量,和目标存储块未发生损坏时的容量,从所述目标存储块的一组编码中,确定与所述目标存储块的容量配置参数对应的多个编码。例如,目标存储块bank8的容量可以是1gb,包括region《5:0》6个区域,在目标容量为(2/3)gb,bank8未发生损坏的情况下,从00、01、10和11一组编码中,将编码01、10和11,确定与目标存储块的目标容量对应的多个编码。

76.步骤111:从所述与所述目标存储块的容量配置参数对应的多个编码中,随机选择一个编码作为所述目标编码;所述目标编码对应所述目标存储块中待修剪的存储区域;

77.在一种可能的实施方式中,由于所述与所述目标存储块的容量配置参数对应的多个编码中的每一编码对应的待修剪的存储区域的容量是相同的,且目标存储块未发生损坏,因此,与所述目标存储块的容量配置参数对应的多个编码中的任意一个编码均可作为目标编码。

78.步骤113:基于所述目标编码,确定所述目标存储块中待修剪的存储区域的行地址;

79.这里,目标存储块中待修剪的存储区域的行地址可以是16位的行地址ra《15:0》,其中,ra《15》、ra《14》、ra《13》表示地址的高3位元地址。

80.可以理解的是,根据目标编码可以确定待修剪的存储区域,根据待修剪的存储区域可以确定待修剪的存储区域的行地址。

81.在一些可能的实施方式中,目标存储块中不同待修剪的存储区域对应的行地址是不同的,例如,对于容量为1gb、包括region《5:0》6个区域的目标存储块bank8,待修剪的存储区域region《4》和region《5》所对应的存储地址是不同的,其中,region《4》的行地址的高三位元地址为100,region《5》的行地址的高三位元地址为101。

82.步骤115:基于所述目标编码和所述待修剪的存储区域的行地址,生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号;

83.在一些可能的实施方式中,基于所述目标编码和所述待修剪的存储区域的行地址,生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号,可以是将目标编码和待修剪的存储区域的行地址输入与非门组成的逻辑电路,逻辑门电路输出用于选中所述目标存储块中待修剪的存储区域的区域选择信号。

84.步骤117:基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置。

85.本技术实施例中,在目标存储块的容量配置参数包括目标存储块中待修剪的存储区域,或所述目标存储块中可利用的存储区域的情况下,可以根据目标存储块中待修剪的存储区域或所述目标存储块中可利用的存储区域来确定待修剪的存储区域,并将待修剪的存储区域对应的编码确定为目标编码;在目标存储块的容量配置参数包括目标存储块的目标容量的情况下,确定目标存储块的目标容量对应的多个编码,可以将多个编码中的任一编码作为目标编码。如此,由于容量配置参数是根据目标存储块的实际情况所确定的,因此,所确定的目标编码是根据目标存储块的实际情况所确定的待修剪的存储区域,如此,所确定的目标编码更符合实际容量配置的实际需求。同时,由于同时根据目标编码和待修剪存储区域的行地址来生成区域选择信号,所确定的区域选择信号能够较为准确地实现对应目标存储块中的待修剪的存储区域的修剪。

86.本技术实施例提供了又一种半导体存储器上存储块的容量配置方法,所述方法包括以下步骤:

87.步骤201:确定所述存储器上的待配置的目标存储块;

88.步骤203:确定所述目标存储块的容量配置参数,所述容量配置参数用于表征所述目标存储块的待配置容量;

89.步骤205:基于所述目标存储块的容量配置参数,从所述目标存储块的一组编码中,确定目标编码;所述目标编码对应所述目标存储块中待修剪的存储区域;

90.步骤207:基于所述目标编码,确定所述目标存储块中待修剪的存储区域;

91.步骤209:对所述目标编码与对应所述待修剪的存储区域的行地址进行逻辑处理,得到目标电平;所述待修剪的存储区域的行地址为所述目标存储块的行地址中的高位元地址,所述高位元地址用于区别所述目标存储块中的不同存储区域;

92.可以理解的是,待修剪的存储区域的行地址中的高位元地址可以是行地址中的高三位元地址或高两位元地址。在一个示例中,对于容量为1gb、包括region《5:0》6个区域的目标存储块bank8,待修剪的存储区域region《4》的行地址的高三位元地址为100,region《5》的行地址的高三位元地址为101。

93.在一个示例中,可以将目标编码理解为一种将行地址进行映射的映射因子。

94.在一种可能的实施方式中,将所述目标编码与对应待修剪的存储区域的行地址进行逻辑处理,得到目标电平,可以是将目标编码与对应待修剪的存储区域的行地址输入与非门组成的译码器,通过译码器对目标编码与对应待修剪的存储区域的行地址进行逻辑处理,得到逻辑处理后的目标电平。

95.步骤211:将所述目标电平作为所述区域选择信号;

96.步骤213:基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置。

97.本技术实施例中,通过对所述目标编码与对应待修剪的存储区域的行地址中的高位元地址进行逻辑处理,将逻辑处理后得到目标电平作为区域选择信号,由于得到的目标电平是将待修剪的存储区域对应的编码作为映射因子,对行地址中的高位元地址进行映射所得到的,因此,获取的区域选择信号能够更准确地实现对待修剪的存储区域的修剪。

98.本技术实施例提供了再一种半导体存储器上存储块的容量配置方法,所述方法包括以下步骤:

99.步骤301:确定所述存储器上的待配置的目标存储块;

100.步骤303:确定所述目标存储块的容量配置参数,所述容量配置参数用于表征所述目标存储块的待配置容量;

101.步骤305:在所述目标存储块的容量配置参数包括所述目标存储块的目标容量的情况下,确定所述目标存储块的最大容量;

102.可以理解的是,目标存储块的最大容量可以是目标存储块未发生损坏,也未被修剪的情况下的容量。例如,目标存储块的最大容量可以是1gb。

103.步骤307:在所述目标容量小于所述最大容量的情况下,基于所述目标容量,从所述目标存储块的一组编码中,确定目标编码;所述目标编码对应所述目标存储块中待修剪的存储区域;

104.可以理解的是,在对半导体上的目标存储块进行容量配置的过程中,目标容量肯定是小于等于目标存储块的最大容量的,即,仅可能将目标存储块的容量配置的比目标存储块的最大容量小,无法将目标存储块的容量配置的比目标存储块的最大容量还要大。例如,当半导体上的目标存储块的最大容量为1gb的情况下,目标容量需要小于等于1gb,不可能大于1gb。

105.在一种可能的实施方式中,在所述目标容量小于所述最大容量的情况下,基于所述目标容量,从所述目标存储块的一组编码中,确定目标编码,可以是在目标存储块的目标容量小于目标存储块的最大容量的情况下,根据最大容量与目标容量之间的差值,确定待修剪的存储区域的容量;然后,确定目标存储块是否存在损坏区域,在确定目标存储块存在损坏区域的情况下,确定损坏区域和损坏区域的容量,根据待修剪的存储区域的容量、损坏区域和损坏区域的容量,确定待修剪的存储区域;最后,从目标存储块的一组编码中,确定待修剪的存储区域对应的编码为目标编码。

106.在另一种可能的实施方式中,在所述目标容量小于所述最大容量的情况下,基于所述目标容量,从所述目标存储块的一组编码中,确定目标编码,可以是在目标存储块的目标容量小于目标存储块的最大容量的情况下,根据最大容量与目标容量之间的差值,确定

待修剪的存储区域的容量;然后,确定目标存储块是否存在损坏区域,在确定目标存储块不存在损坏区域的情况下,将待修剪的存储区域的容量大小相同的任一存储区域确定为待修剪的存储区域;最后,从目标存储块的一组编码中,确定待修剪的存储区域对应的编码为目标编码。

107.步骤309:基于所述目标编码,生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号;

108.步骤311:基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置。

109.本技术实施例中,明确了在目标存储块目标容量小于最大容量的情况下,才基于目标容量,从目标存储块的一组编码中,确定目标编码,如此,可以实现对半导体存储器上的存储块的容量合理配置。

110.本技术实施例提供了另一种半导体存储器上存储块的容量配置方法,所述方法包括以下步骤:

111.步骤401:确定所述存储器上的待配置的目标存储块;所述目标存储块包括至少两个逻辑存储区域,每一所述逻辑存储区域包括连续的至少两个物理存储区域;所述目标存储块中待修剪的存储区域包括连续的至少两个待修剪的物理存储区域;

112.在一个可能的实施方式中,目标存储块的容量是1g,目标存储块可以包括region《5:0》6个区域,其中,region《1:0》可以是逻辑存储区域1;region《3:2》可以是逻辑存储区域2;region《1:0》可以是逻辑存储区域3,即,目标存储块包含3个逻辑存储区域。region《0》至region《5》可以分别是物理存储区域1至物理存储区域6,逻辑存储区域1可以包括连续的region《0》和region《1》;逻辑存储区域2可以包括连续的region《2》和region《3》;逻辑存储区域3可以包括连续的region《4》和region《5》。可以看出,每一逻辑存储区包括两个连续的物理存储区域。

113.步骤403:确定所述目标存储块的容量配置参数,所述容量配置参数用于表征所述目标存储块的待配置容量;

114.步骤405:在所述目标存储块的容量配置参数包括所述目标存储块中待修剪的物理存储区域的情况下,基于所述目标存储块中连续的所述至少两个待修剪的物理存储区域,在所述目标存储块所包括的至少两个逻辑存储区域中,确定待修剪的逻辑存储区域;

115.可以理解的是,本技术是以逻辑存储区域为单位进行修剪的,即,只要逻辑存储区中的任一物理存储区域发生损坏,则需要将物理存储区域所在的逻辑存储区域同时修剪掉。例如,对于逻辑存储区域region《1:0》,其中,物理存储单元region《1》发生损坏,则需要将region《1》所在的逻辑存储区域region《1:0》修剪掉。

116.在一些可能的实施方式中,在所述目标存储块的容量配置参数包括所述目标存储块中待修剪的物理存储区域的情况下,基于所述目标存储块中待修剪的物理存储区域,在所述目标存储块所包括的至少两个逻辑存储区域中,确定待修剪的逻辑存储区域,可以是在所述目标存储块的容量配置参数包括所述目标存储块中待修剪的物理存储区域的情况下,将目标存储块所包括的至少两个逻辑存储区域中,包含待修剪的物理存储区域的逻辑存储区域,确定为待修剪的逻辑存储区域。

117.步骤407:基于所述待修剪的逻辑存储区域,从所述目标存储块的一组编码中,确

定目标编码;所述目标编码对应所述目标存储块中待修剪的存储区域;

118.可以理解的是,待修剪的逻辑存储区域可以是待修剪的存储区域的一种实现方式。

119.步骤409:基于所述目标编码,生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号;

120.步骤411:基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置。

121.本技术实施例中,将目标存储块的修剪的最小单位确定为逻辑存储区域,对于逻辑存储区域下一级的物理存储区域发生损坏的情况,则需要将物理存储区域所在的逻辑存储区域进行修剪,如此,可以减小对损坏存储区域漏修剪的可能性。

122.本技术实施例提供了其它一种半导体存储器上存储块的容量配置方法,所述方法包括以下步骤:

123.步骤501:确定所述存储器上的待配置的目标存储块;所述目标存储块包括至少两个逻辑存储区域,每一所述逻辑存储区域包括连续的至少两个物理存储区域;

124.步骤503:确定所述目标存储块的容量配置参数,所述容量配置参数用于表征所述目标存储块的待配置容量;所述目标存储块的容量配置参数包括所述目标存储块的目标容量;

125.步骤505:确定所述目标存储块中单个所述物理存储区域的容量;

126.可以理解的是,单个物理存储区域的容量等于存储块的总容量与物理存储区域的个数的比值。例如,目标存储块的总容量为1gb,物理存储区域的个数为6个,则单个物理存储区域的容量为(1/6)gb。

127.步骤507:确定单个所述逻辑存储区域所包括的连续的物理存储区域的数量;

128.在一个示例中,单个逻辑存储区域所包括的连续的物理存储区域的数量可以是2,也可以是大于2的其它整数。

129.在一种可能的实施方式中,单个所述逻辑存储区域所包括的连续的物理存储区域的数量是根据目标存储块的一组编码中每一编码的位数和目标存储块中所包括的物理存储器的数量所确定的。

130.步骤509:基于单个所述逻辑存储区域所包括的连续的物理存储区域的数量和单个物理存储区域的容量,确定单个所述逻辑存储区域的容量。

131.在一些可能的实施方式中,基于单个所述逻辑存储区域所包括的连续的物理存储区域的数量和单个物理存储区域的容量,确定单个所述逻辑存储区域的容量,可以是将单个所述逻辑存储区域所包括的连续的物理存储区域的数量与单个物理存储区域的容量的乘积,确定为单个逻辑存储区域的容量。例如,在单个所述逻辑存储区域所包括的连续的物理存储区域的数量为2,单个物理存储区域的容量为(1/3)gb的情况下,单个逻辑存储区域的容量为(2/3)gb。

132.步骤511:确定所述目标存储块的最大容量;

133.可以理解的是,目标存储块的最大容量可以是目标存储块未发生损坏或未被修剪的情况下的容量。确定目标存储块的最大容量的方式可以是从半导体存储器的出厂检测数据中所获取的。

134.在一种可能的实施方式中,对于最大容量为1gb、包括region《5:0》6个物理存储区域的目标存储块bank8,其中,将每两个连续的物理存储区域确定为一个逻辑存储区域,则形成region《1:0》逻辑存储区域1、region《3:2》逻辑存储区域2和region《5:4》逻辑存储区域3,如此,可以看出,物理存储区域的容量为(1/6)gb,逻辑存储区域的容量为(1/3)gb。

135.步骤513:基于单个所述逻辑存储区域的容量和所述目标存储块的最大容量,确定在所述目标存储块上的可配置容量;所述单个所述逻辑存储区域的容量包括单个所述逻辑存储区域所包括的各物理存储区域的容量之和;

136.在一个实施例中,若逻辑存储区域包含两个物理存储区域,每一物理存储区域的容量是(1/6)gb,则逻辑存储区域的容量为(1/3)gb。

137.对于基于单个所述逻辑存储区域的容量和所述目标存储块的最大容量,确定在所述目标存储块上的可配置容量的实现方式,示例性地,可以是将目标存储块的最大容量与整数倍的逻辑存储区域的容量之差,确定为目标存储块上的可配置容量。例如,若目标存储块的最大容量为1gb,逻辑存储区域的容量为(1/3)gb,则目标存储块的可配置容量分别为(1/3)gb、(2/3)gb、1gb,均是(1/3)gb的整数倍。

138.步骤515:基于所述可配置容量和所述目标容量确定待配置的实际容量;

139.在一种可能的实施方式中,基于所述可配置容量和所述目标容量确定待配置的实际容量,可以是将可配置容量和目标容量进行比较,将与目标容量容量最接近小于目标容量的可配置容量,确定为待配置的实际容量。

140.可以理解的是,在目标存储块的最大容量为1gb,逻辑存储区域的容量为(1/3)gb、目标容量为(5/6)gb的情况下,可配置容量可以至少包括(1/3)gb、(2/3)gb;由于(2/3)gb是与(5/6)gb最接近的可配置容量((5/6)gb并不是逻辑存储区域的容量的整数倍),因此,可以确定待配置的实际容量是(2/3)gb。

141.步骤517:在所述实际容量与所述目标容量不一致的情况下,基于所述实际容量,从所述目标存储块的一组编码中,确定目标编码;所述目标编码对应所述目标存储块中待修剪的存储区域;

142.可以理解的是,由于可配置容量是实际能够实施或得到的容量,因此,在实际容量与目标容量不一致的情况下,能够根据实际容量从目标存储块的一组编码中,确定目标编码。

143.步骤519:基于所述目标编码,生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号;

144.步骤521:基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置。

145.本技术实施例中,可以根据单个物理存储区域的容量和逻辑存储区域所包括的连续的物理存储区域的数量,确定单个逻辑存储区域的容量;根据单个逻辑存储区域的容量和目标存储块的最大容量,可以确定目标存储块上的可配置容量;根据目标存储块的可配置容量和目标容量,可以确定待配置的实际容量,在实际容量与所述目标容量不一致的情况下,基于实际容量确定目标编码。

146.本技术实施例提供了另一种半导体存储器上存储块的容量配置方法,所述方法包括以下步骤:

147.步骤601:确定所述存储器上的待配置的目标存储块;所述目标存储块包括至少两个逻辑存储区域,每一所述逻辑存储区域包括连续的至少两个物理存储区域;

148.步骤603:确定所述目标存储块的容量配置参数,所述容量配置参数用于表征所述目标存储块的待配置容量;所述目标存储块的容量配置参数包括所述目标存储块的目标容量;

149.步骤605:确定所述目标存储块中单个物理存储区域的容量;

150.步骤607:确定所述目标存储块的一组编码中每一所述编码所包括的位数;

151.可以理解的是,目标存储块的一组编码中每一所述编码所包括的位数是根据目标存储块所包含的逻辑存储区域的个数所确定的。例如,若目标存储块的一组编码中每一所述编码所包括的位数为2,则逻辑存储区域的个数不能大于2的二次方。

152.步骤609:基于所述目标存储块中所包括的物理存储区域的数量和每一所述编码所包括的位数,确定单个所述逻辑存储区域所包括的所述物理存储区域的数量;

153.在一些可能的实施方式中,基于所述存储块中所包括的物理存储区域的数量和每一所述编码所包括的位数,确定单个所述逻辑存储区域所包括的物理存储区域的数量,可以是根据每一所述编码所包括的位数确定所述目标存储块的一组编码所能区分的最大逻辑存储区域的个数;根据所确定的最大逻辑存储区域的个数和物理存储区域的数量,确定单个所述逻辑存储区域所包括的连续的物理存储区域的数量。

154.在一个示例中,根据所确定的最大逻辑存储区域的个数和物理存储区域的数量,确定单个所述逻辑存储区域所包括的连续的物理存储区域的数量,可以是在最大逻辑存储区域的个数大于等于物理存储区域的数量的情况下,确定单个所述逻辑存储区域所包括的连续的物理存储区域的数量为1;在最大逻辑存储区域的个数小于物理存储区域的数量,但2倍的最大逻辑存储区域的个数大于物理存储区域的数量的情况下,确定单个所述逻辑存储区域所包括的连续的物理存储区域的数量为2。

155.以目标存储块的一组编码的每一编码的位数为2位,物理存储区域的个数为6为例进行说明,可以确定在目标存储块的一组编码的每一编码的位数为2位时所确定的最大逻辑区域的个数为4,显然,最大逻辑区域的个数4小于物理存储区域的个数6,但2倍的最大逻辑存储区域的个数为8大于物理存储区域的个数6,因此,可以确定单个所述逻辑存储区域所包括的连续的物理存储区域的数量为2。

156.以目标存储块的一组编码的每一编码的位数为3位,物理存储区域的个数为6为例进行说明,可以确定在目标存储块的一组编码的每一编码的位数为3位时所确定的最大逻辑区域的个数为8,显然,最大逻辑区域的个数8大于物理存储区域的个数6,因此,可以确定单个所述逻辑存储区域所包括的连续的物理存储区域的数量为1。

157.步骤611:基于单个所述逻辑存储区域所包括的连续的物理存储区域的数量和单个物理存储区域的容量,确定单个所述逻辑存储区域的容量。

158.在一种可能的实施方式中,基于单个所述逻辑存储区域所包括的连续的物理存储区域的数量和单个物理存储区域的容量,确定单个所述逻辑存储区域的容量,可以是将逻辑存储区域包括的连续的物理存储区域的数量与单个物理存储区域的容量的乘积,确定为单个所述逻辑存储区域的容量。例如,在逻辑存储区域包括的连续的物理存储区域的数量2、单个物理存储区域的容量为(1/6)gb的情况下,可以确定单个所述逻辑存储区域的容量

为(1/3)gb。

159.步骤613:确定所述目标存储块的最大容量;

160.步骤615:基于单个所述逻辑存储区域的容量和所述目标存储块的最大容量,确定在所述目标存储块上的可配置容量;所述单个所述逻辑存储区域的容量包括单个所述逻辑存储区域所包括的各物理存储区域的容量之和;

161.步骤617:基于所述可配置容量和所述目标容量确定待配置的实际容量;

162.步骤619:在所述实际容量与所述目标容量不一致的情况下,基于所述实际容量,从所述目标存储块的一组编码中,确定目标编码;所述目标编码对应所述目标存储块中待修剪的存储区域;

163.步骤621:基于所述目标编码,生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号;

164.步骤623:基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块的容量进行配置。

165.本技术实施例中,根据目标存储块的一组编码中每一所述编码所包括的位数和目标存储块中所包括的物理存储区域的数量,可以准确确定出单个逻辑存储区域所包括的连续的物理存储区域的数量。

166.本技术实施例提中,目标存储块的最大容量(未损坏也未被修剪时的容量)是1gb,可以通过trim实现(2/3)gb的容量;目标存储块被分成region《5:0》6个区域,在目标存储块的容量为1g时,region《5:0》这6个区域都会被用到,在目标存储块的容量为(2/3)g时,则从region《5:0》6个区域中选取其中的4个区域。对于dram的一个颗粒(die)而言,例如,一个颗粒(die)可以包括16个存储块(bank),一个存储块的容量可以为1gb(意味着至少包含2^30个存储电容,实际上dram中还含有冗余的存储电容,一个存储块的容量为1gb,其包含的存储电容会大于2^30个),那么一个完整的颗粒的容量可以达到16gb,如果一个颗粒因为制造工艺或其他原因,导致一部分存储电容无法工作,那么通过trim可以将这个颗粒的容量配置为12gb或8gb或4gb或2gb,从而在一部分存储电容无法工作的条件下,尽可能的利用这个dram颗粒。

167.表1

[0168][0169]

参见表1,可以看出:

[0170]

trim_halfgoodbnk《1:0》=01时,选取region《3:0》这4个区域,修剪region《4,5》,实现(2/3)g;

[0171]

trim_halfgoodbnk《1:0》=10时,选取region《1:0》和region《5:4》这4个区域,修剪region《3,2》,实现(2/3)g;

[0172]

trim_halfgoodbnk《1:0》=11时,选取region《5:2》4个区域,修剪region《1:0》,实

现(2/3)g。

[0173]

图3a为本技术实施例提供的一种全芯片存储区域和地址的结构示意图,如图3a所示,全芯片包括16个存储块,其中,行控制301引出的行控制线的位数为16,左侧分布着存储块4、存储块6、存储块5、存储块7、存储块0、存储块2、存储块1和存储块3;右侧分布着存储块8、存储块10、存储块9、存储块11、存储块12、存储块14、存储块13和存储块15。

[0174]

图3b为本技术实施例提供的对图3a中的存储块8进行放大后所展现的结构示意图,如图3b所示,存储块8包括region《0》至region《5》6个物理区域,其中,通过行地址ra《15:0》中的ra《15》、ra《14》和ra《13》来对region《0》至region《5》6个区域进行编码,可以看出,region《0》对应的编码为000;region《1》对应的编码为001;region《2》对应的编码为010;region《3》对应的编码为011;region《4》对应的编码为100;region《5》对应的编码为101。

[0175]

图3c为本技术实施例提供的对存储块8进行修剪后的结构示意图,如图3c所示,为了将存储块8的容量从1gb改变为(2/3)gb,其中,存储块8的连续两个物理存储区域region《4》和region《5》被修剪掉了,当然,region《4》和region《5》可以是已经损坏的物理存储区域,也可以是在region《0》至region《5》中每一物理存储区域均未损坏的情况下,随机选取的任意连续的两个物理存储区域。

[0176]

本技术实施例中,基于目标编码生成用于选中所述目标存储块中待修剪的存储区域的区域选择信号的实现过程中,需要对目标编码进行译码。其中,定义了ra1514《0》、ra1514《1》和ra1514《2》三位区域选择信号;ra1514《0》、ra1514《1》和ra1514《2》与各存储区域的关系可以参见表2。

[0177]

表2

[0178][0179]

表2中,ra1514《0》表示两个区域region《0,1》;ra1514《1》表示两个区域region《2,3》;ra1514《2》表示两个区域region《4,5》。

[0180]

为了得到区域选择信号ra1514《0》、ra1514《1》和ra1514《2》,可以通过逻辑电路对目标编码和存储块8的高两位元地址(ra《15》、ra《14》)进行处理逻辑处理得到。

[0181]

在得到区域选择信号ra1514《0》、ra1514《1》和ra1514《2》之前,可以先确定一些中间信号,例如,对目标编码进行逻辑非运算后得到的信号、以及对ra《15:14》进行逻辑非运算后得到的信号等。

[0182]

图3d为本技术实施例提供的一种对目标编码进行逻辑非运算的逻辑电路图,如图3d所示,densitytrim《1:0》表示目标编码,对densitytrim《1:0》进行逻辑非运算后,可以得到densitytrimb《1:0》。

[0183]

图3e为本技术实施例提供的一种对高两位元地址进行逻辑非运算的逻辑电路图,如图3e所示,ra《15:14》为高两位元地址,对ra《15:14》进行逻辑非运算后,可以得到rab《15:14》。

[0184]

图3f为本技术实施例提供的一种对densitytrim《0》和densitytrim《1》进行逻辑

运算的逻辑电路图,如图3f所示,对densitytrim《0》和densitytrim《1》进行逻辑与非运算后,可以得到s11n,对s11n再进行逻辑非运算后可以得到s11。

[0185]

图3g为本技术实施例提供的对densitytrimb《0》和densitytrimb《1》进行逻辑运算的逻辑电路图,如图3g所示,对densitytrimb《0》和densitytrimb《1》进行逻辑与非运算后,可以得到s00n,对s00n再进行逻辑非运算后可以得到s00。

[0186]

图3h为本技术实施例提供的通过目标编码和高两位元地址得到区域选择信号ra1514《0》的逻辑电路图,如图3h所示,对rab《15》、rab《14》和s11n进行逻辑与非运算后,再进行逻辑非运算可以得到ra1514《0》。

[0187]

图3i为本技术实施例提供的通过目标编码和高两位元地址得到区域选择信号ra1514《1》的逻辑电路图,如图3i所示,对rab《15》、rab《14》和s11进行逻辑与非运算,得到第一逻辑结果;再对rab《15》、ra《14》和densitytrimb《1》进行逻辑与非运算,得到第二逻辑结果;最后,对第一逻辑结果和第二逻辑结果进行逻辑与非运算得到ra1514《1》。

[0188]

图3j为本技术实施例提供的通过目标编码和高两位元地址得到区域选择信号ra1514《2》的逻辑电路图,如图3j所示,对ra《15》、rab《14》和s00进行逻辑与非运算,得到第三逻辑结果;再对rab《15》、ra《14》和densitytrim《1》进行逻辑与非运算,得到第四逻辑结果;最后,对第三逻辑结果和第四逻辑结果进行逻辑与非运算得到ra1514《2》。

[0189]

本技术实施例中,对目标存储块的容量配置的选择方案存在多种,可参见下表3。

[0190]

表3

[0191]

density《1:0》

ꢀꢀꢀ

00(1g)ra1514《0》ra1514《1》ra1514《2》01((2/3)g)ra1514《0》ra1514《2》ra1514《2》=010((2/3)g)ra1514《0》ra1514《1》=0ra1514《2》11((2/3)g)ra1514《0》=0ra1514《1》ra1514《2》

[0192]

表3中,对于不同的容量通过density《1:0》表示,density《1:0》为00,代表目标存储块的容量为1g,且ra1514《0》至ra1514《2》均为1代表region《0》至region《5》均为1(ra1514《0》代表region《0,1》,由于ra1514《0》代表region《0,1》,ra1514《1》代表region《2,3》,ra1514《2》代表region《4,5》,)即可用;

[0193]

density《1:0》为01,代表bank的容量为(2/3)g,且ra1514《0》和ra1514《1》为1,ra1514《2》为0,代表region《0》至region《3》均为1(可用),region《4》和region《5》为0(不可用),(ra1514《0》代表region《0,1》,由于ra1514《0》代表region《0,1》,ra1514《1》代表region《2,3》,ra1514《2》代表region《4,5》);

[0194]

density《1:0》为10,代表bank的容量为(2/3)g,且ra1514《0》和ra1514《2》为1,ra1514《1》为0,代表region《0》、region《1》、region《4》和region《5》均为1(可用),region《2》和region《3》为0(不可用),(ra1514《0》代表region《0,1》,由于ra1514《0》代表region《0,1》,ra1514《1》代表region《2,3》,ra1514《2》代表region《4,5》)。

[0195]

density《1:0》为11,代表bank的容量为(2/3)g,且ra1514《0》为0,ra1514《1》和ra1514《2》为0,代表region《0》、region《1》为0(不可用)、region《2》至region《5》均为1(可用),(ra1514《0》代表region《0,1》由于ra1514《0》代表region《0,1》,ra1514《1》代表region《2,3》,ra1514《2》代表region《4,5》)。

[0196]

图4为本技术实施例提供的一种适用于对半导体存储器上存储块的容量进行配置的系统结构图,如图4所示,所述系统结构包括读写系统401、控制单元402、译码单元403和存储块404,其中,读写系统401发出的行地址线ra《15:0》中的ra《12:0》直接与存储块404连接,ra《15:13》连接控制单元402,控制单元402将ra《15:13》与生成的densitytrim《1:0》输入给译码单元403,译码单元403与存储块404连接,译码单元403对ra《15:13》与densitytrim《1:0》进行逻辑运算得到区域选择信号,并将得到的区域选择新信号传递给存储块404,存储块404根据区域选择信号修剪对应的待修剪区域,实现对存储块容量的配置。

[0197]

可以理解的是,译码单元403可以通过图3h至图3j所组成的电路实现,可以参见上面的描述。

[0198]

本技术实施例中,ra1514《2:0》不同的编码状态对应存储块404不同的区域,例如,ra1514《2:0》=100对应的区域为region《0,1》。

[0199]

除此之外,本技术实施例还提供一种半导体存储器,所述半导体存储器支持上述实施例提供的半导体存储器上存储块的容量配置方法。图5为本技术实施例提供的一种半导体存储器的结构示意图,如图5所示,所述半导体存储器包括:

[0200]

目标存储块501,包括至少两个存储区域;

[0201]

地址处理单元502,用于输出所述目标存储块501的地址;所述地址处理单元502的输出端连接所述目标存储块501;

[0202]

编码获取单元503,用于接收目标编码,所述目标编码对应于所述目标存储块501中的至少一个待修剪的存储区域;

[0203]

区域选择信号生成单元504,用于基于所述目标编码,生成用于选中所述目标存储块501中待修剪的存储区域的区域选择信号;所述区域选择信号生成单元503的输出端连接修剪单元505的输入端;

[0204]

所述修剪单元505,用于基于所述区域选择信号,对所述待修剪的存储区域进行修剪,以实现对所述目标存储块501的容量进行配置;所述修剪单元505的输出端连接所述目标存储块501。

[0205]

在一些实施例中,所述半导体存储器还包括:控制单元,用于确定所述半导体存储器上的待配置的目标存储块501;确定所述目标存储块501的容量配置参数,所述容量配置参数用于表征所述目标存储块501的待配置容量;基于所述目标存储块501的容量配置参数,从所述目标存储块501的一组编码中,确定所述目标编码;所述目标编码对应所述目标存储块501中待修剪的存储区域;所述控制单元的输出端连接所述编码获取单元。

[0206]

在一些实施例中,所述地址处理单元502包括:行地址处理单元,用于输出所述目标存储块501的行地址;所述行地址处理单元的输出端连接所述区域选择信号生成单元的输入端和所述目标存储块501;列地址处理单元,用于输出所述目标存储块501的列地址;所述列地址处理单元的输出端连接所述目标存储块501;块地址处理单元,用于输出所述目标存储块501的块地址;所述块地址处理单元的输出端连接所述目标存储块501;所述区域选择信号生成单元503,用于将所述目标编码作与对应的待修剪的存储区域的行地址进行逻辑处理,得到目标电平;将所述目标电平作为所述区域选择信号。

[0207]

在一些实施例中,所述行地址处理单元中高位元地址的输出端连接所述区域选择信号生成单元的输入端;所述高位元地址用于区别所述目标存储块501中的不同的存储区

域。

[0208]

在一些实施例中,所述区域选择信号生成单元503包括:与非门和非门组成的逻辑门电路;所述逻辑门电路的输入端包括所述目标编码对应的信号线和所述待修剪的存储区域的行地址对应的信号线;所述逻辑门电路,用于对所述目标编码与对应的待修剪的存储区域的行地址进行逻辑处理,得到目标电平;将所述目标电平作为所述区域选择信号。

[0209]

在一些实施例中,所述区域选择信号生成单元503,包括译码器;所述译码器的输入端为所述目标编码对应的信号线;所述译码器输出的每一电平在有效的情况下为区域选择信号,所述译码器的每一输出端分别连接所述修剪单元的输入端。

[0210]

本技术实施例提供的半导体存储器与上述实施例提供的半导体存储器上存储块的容量配置方法类似,对于本技术实施例未详尽披露的技术特征,请参照上述实施例进行理解,这里,不再赘述。

[0211]

本技术实施例提供一种半导体存储器,由于所述半导体存储器对于不同待配置的目标存储块的容量配置参数可以是不同的,基于不同的容量配置参数所确定的目标编码也可以不同,进而基于不同的目标编码所生成的区域选择信号也不同。如此,通过不同的区域选择信号,可以实现对不同待配置的目标存储块的不同待修剪的存储区域进行修剪;进而,能够灵活选取待修剪的存储区域,提升对半导体存储器上存储块的容量配置的有效利用率。

[0212]

在本技术所提供的几个实施例中,应该理解到,所揭露的设备和方法,可以通过非目标的方式实现。以上所描述的设备实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,如:多个单元或组件可以结合,或可以集成到另一个系统,或一些特征可以忽略,或不执行。

[0213]

本技术所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

[0214]

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1