计算系统与计算方法与流程

本发明属于集成电路领域,更具体地,涉及集成电路计算芯片的体系架构和工作方式。

背景技术:

1、随着物联网与云计算的发展,计算任务的复杂性与日俱增,给计算芯片带来更大的压力。其中,计算芯片的主要性能指标可以分为功耗和算力指标。无论是在物联网等供能受限的场景还是云计算等消耗大量能量的场景中,功耗指标都是十分关键的。因此,如何在提供给定算力的前提下,进一步降低芯片功耗,是计算芯片的重要研究方向。

2、计算芯片的功耗主要来自两部分操作,一是数据读写,二是数据计算。对于特定计算,如深度神经网络中涉及的推理和训练计算,会出现大量的数据读写操作。数据读写的目标存储器可以分为片上存储和片外存储。由于片上存储广泛采用静态随机存储器(sram),其密度较低,因此其存储容量往往较小。当遇到大量数据读写操作时,就需要对片外存储进行访问。考察数据读写操作,对互连线周围寄生电容的充放电是其主要能耗来源。而片外存储通过较大间距的互连线和引脚进行数据访问,会产生相比片上存储大得多的能耗。针对这一现象,将数据尽可能地部署在片上存储中,并进一步降低对片上存储的数据访问是优化计算芯片能效的重要策略。

3、存算一体化架构就是其中的一个具体实现。这一架构通过构造基于忆阻器的高密度计算单元,可以将计算数据部分固化在计算单元内,从而减少了对于数据的访问操作。同时,由于采用模拟计算的方式,它对于存储数据有一定的鲁棒性,因而可以实现更大规模的片上存储。一种典型的计算方式是,在电导值为矩阵g的忆阻器阵列一侧通过数字-模拟转换器(dac)输入电压向量v,通过测量正交的另一侧的输出电流向量i,既可以实现i=gv的矩阵-向量乘法计算。其中,在神经网络推理的计算场景中,g对应网络权重,更新较少,v对应数据的特征图,更新较多。

4、在现有的存算一体化的实现中,当进行阵列规模的并行运算时,阵列的开启区域存在巨大的变化,同时内部存储节点高低阻态会存在巨大差异。因此,输入驱动级需要稳定驱动的负载阻值和电容可能存在极大的差异。这一问题对输入电路的设计和造成一定的压力。

5、此外,在同一个输入方向,对于不同的存储数据排布,像线阻之类的非理想因素也会造成不同的影响。这意味着改变某一存储器的数据可能会对相邻数据造成影响。

技术实现思路

1、本发明的目的在于解决上述问题,提出一种计算系统与计算方法。

2、本发明的目的是通过以下技术方案实现的:

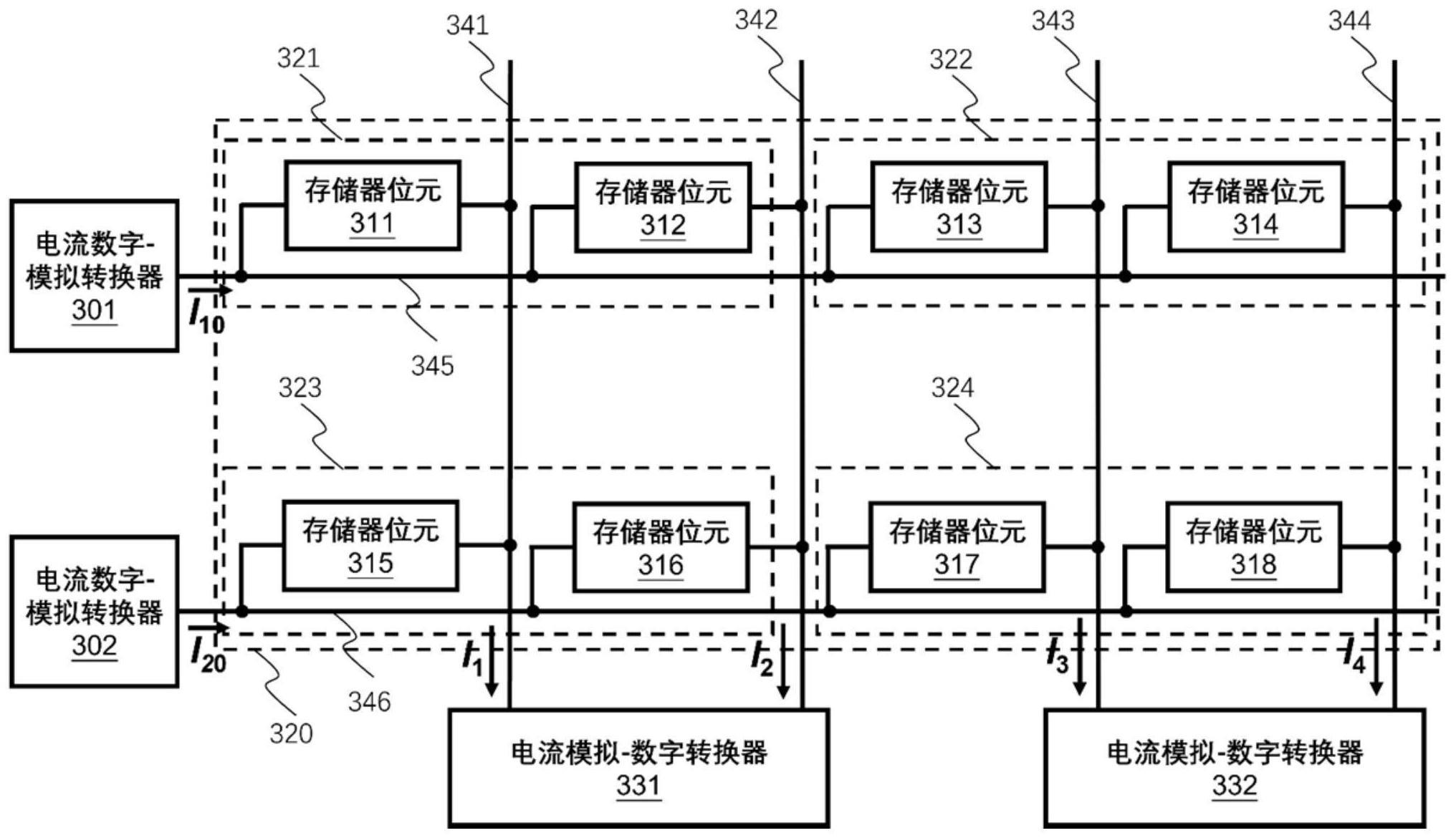

3、第一方面,提供一种计算系统,

4、所述计算系统包含存储器阵列和外围电路;

5、所述存储器阵列包含相交的字线和位线;

6、所述字线相连的存储器位元中数据加和是常数;

7、所述外围电路包含信号输入级和信号采样级;

8、所述输入级连接到所述字线;

9、所述采样级连接到所述位线。

10、进一步地,

11、所述信号输入级为电流输入;

12、所述信号采样级为电流采样。

13、进一步地,

14、对所述字线相连的存储器位元按位置相邻进行两个一组的无交集组合;

15、每个所述组合内两个位元数据加和是常数。

16、进一步地,

17、所述存储器为数字存储器,即存储数据为1或者0;

18、所述组合内位元数据有两种情况,第1个为0,第2个为1,或者第一个为1,第二个为0。

19、进一步地,

20、所述数字存储器中包含磁隧穿结,其高阻状态存储数据1,低阻状态存储数据0,或者高阻状态存储数据0,低阻状态存储数据1。

21、进一步地,

22、所述组合内的两根位线输入到一个差分的采样级中。

23、进一步地,

24、所述存储器为模拟存储器,即存储数据为0到1之间的数据值,其中数据值定义为数据读取电路测量值的某一对应关系,所述对应关系定义如下:

25、所述数据读取电路包含电压激励电路和电流测量电路;

26、对某一存储数据,所述电压激励电路施加读电压时,所述电流测量电路测量的电流值记为x;

27、对存储数据1,所述电压激励电路施加读电压时,所述电流测量电路测量的电流值记为y2;

28、对存储数据0,所述电压激励电路施加读电压时,所述电流测量电路测量的电流值记为y1;

29、则所述数据读取电路测量值对应的存储数据为(x-y1)/(y2-y1);

30、所述组合内位元数据满足,第一个位元存储数据是x时,第二个位元存储数据为1-x,其中x是0到1之间的数据值。

31、进一步地,

32、所述组合内的两根位线输入到一个差分的采样级中。

33、进一步地,所述存储器包括磁阻存储器、阻变存储器、相变存储器、铁电存储器、静态随机存储器、动态随机存储器、浮栅存储器以及电荷捕获存储器中的一种或多种。

34、第二方面,提供一种如第一方面所述的计算系统的计算方法,包括:

35、步骤一,将所述采样级输入端电位设置为与所述输入级的零电位相同;

36、步骤二,在所述输入级施加激励信号;

37、步骤三,在所述采样级进行信号采样;

38、步骤四,按计算值和信号采样值的对应关系,将所述信号采样值映射到所述计算值;

39、其中先后顺序满足,步骤二先于步骤三,步骤一先于步骤三,步骤三先于步骤四。

40、进一步地,

41、在所述输入级施加的激励信号为电流信号;

42、在所述采样级进行的信号采样为电流采样。

43、本发明的有益效果是:通过本发明可以实现计算过程中输入级和阵列的解耦合,以及阵列单元之间的解耦合。

44、本领域的技术人员在阅读以下具体实施方式并看到附图时将会认识到附加的特征和和优势。

技术特征:

1.一种计算系统,其特征在于,

2.根据权利要求1所述的计算系统,特征在于,

3.根据权利要求1或2所述的计算系统,其特征在于,

4.根据利要求3所述的计算系统,其特征在于,

5.根据权利要求4所述的计算系统,其特征在于,

6.根据权利要求5所述的计算系统,其特征在于,

7.根据权利要求3所述的计算系统,其特征在于,

8.根据权利要求3所述的计算系统,其特征在于,

9.根据权利要求1或2所述的计算系统,其特征在于,

10.一种权利要求1-9中任一项所述计算系统的计算方法,其特征在于,包括:

11.根据权利要求9所述的计算方法,其特征在于,

技术总结

本发明公开了一种计算系统以及一种使用该系统进行计算的方法。主要解决现有技术输入电路和阵列间的耦合,以及阵列存储器位元间的耦合问题。其实现方式是,构造存储器中和对应输入的字线其所相连的存储器位元中数据加和为常数,或者特殊地,构造互补的存储器位元。本发明实现了复杂模拟电路系统中的子系统解耦合,可以降低设计难度,提高系统的可靠性,易用性和效率,可应用于存算一体化的大规模模拟计算系统中。

技术研发人员:赵先成

受保护的技术使用者:浙江力德仪器有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!