一种位线泄漏电流、灵敏放大器及存储器的控制电路的制作方法

1.本发明涉及集成电路技术领域,尤其涉及一种位线泄漏电流、灵敏放大器及存储器的控制电路。

背景技术:

2.随着cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)工艺技术按比例缩小,cmos电路在减小面积的同时也提高了性能。工艺的缩小也降低了电源电压,因此需要降低晶体管的阈值电压以保持晶体管的高性能。但是阈值电压的降低会导致亚阈值泄漏电流的增大,增大的泄漏电流会对静态随机存储器(static random-access memory,sram)的操作尤其是读操作造成严重影响,位线上的泄漏电流会造成读操作时间的延长,甚至造成读数据的错误。

3.为了缓解或者是消除位线泄漏电流造成的影响,现有技术提出了以下几种方案:

4.如图1所示是现有技术中self-compared bit-line pairs的电路结构,self-compared bit-line pairs电路结构的工作原理如下:在位线bl和blb两侧分别增加一条辅助的位线,并把位线和辅助位线对应接到一个四输入灵敏放大器的四个输入上。两个pmos管分别控制位线与辅助位线的连接,当位线的电压由于存在泄漏电流而降低时,辅助位线的电压也降低而保持与位线电压相同。泄漏电流造成的一侧位线电压下降会降低灵敏放大器该侧节点的放电速度,而另一侧辅助位线的电压则对这个放电速度进行了补偿。这种电路结构很好的对泄漏电流造成的位线电压下降进行了补偿,但缺点是这种补偿不是实时的,并没有考虑到开启字线wl后位线存在的泄漏电流,因此会影响补偿的精度。

5.如图2所示是现有技术中x-calibration的电路结构,x-calibration电路结构的工作原理如下:在位线上串联电容,通过附加的pmos管改变位线连接关系,将由泄漏电流导致的位线电压的下降记录在电容上,然后用电容上记录的电压去补偿由于泄漏电流导致的位线电压的变化。但是该电路结构的缺点是,串联电容的充放电时间会降低读操作速度,位线上需要接入两个常开的pmos管来产生电流以保证电压的平稳,这会大幅增加读取时间和功耗。

技术实现要素:

6.本发明的目的是提供一种位线泄漏电流、灵敏放大器及存储器的控制电路,该电路结构在不增加更多控制信号的情况下,能够实时地检测并补偿位线泄漏电流;在位线泄漏电流很大的情况下,依然能够读出正确的数据,有很稳定的性能。

7.本发明的目的是通过以下技术方案实现的:

8.一种位线泄漏电流、灵敏放大器及存储器的控制电路,所述控制电路包括由8t sram存储单元构成的存储阵列和具有对称结构的四输入灵敏放大器,其中:

9.所述存储阵列的两对传输管分别与主位线对和副位线对连接;其中,所述主位线对包括主位线blm和blmb;所述副位线对包括副位线bln和blnb;

10.一列存储单元中连接同一侧存储节点的一根主位线blm和一根副位线blnb分别与所述四输入灵敏放大器两侧的一个输入端连接,其中:

11.所述四输入灵敏放大器中已与副位线blnb连接的一侧的输入端与另一根主位线blmb连接,已与主位线blm连接的一侧的输入端与另一根副位线bln连接;

12.当所述主位线对中的一根主位线上有泄漏电流时,所述副位线对中与这根主位线连接在同一侧存储节点的副位线也产生等量的泄漏电流;因此,在所述四输入灵敏放大器读取数据时,一侧位线的泄漏电流造成的电压降能在另一侧得到实时补偿,进而读出正确数据,实现对位线泄漏电流的控制。

13.由上述本发明提供的技术方案可以看出,上述电路结构在不增加更多控制信号的情况下,能够实时地检测并补偿位线泄漏电流;在位线泄漏电流很大的情况下,依然能够读出正确的数据,有很稳定的性能,并且在不同的位线泄漏电流下,读取数据的时间变化很小,从而提高了电路读操作的性能。

附图说明

14.为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他附图。

15.图1为现有技术中self-compared bit-line pairs的电路结构;

16.图2为现有技术中x-calibration的电路结构;

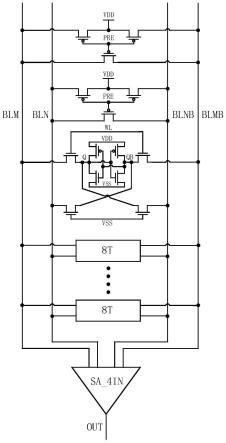

17.图3为本发明实施例所述位线泄露电流、灵敏放大器及存储器的控制电路结构示意图;

18.图4为本发明实施例所述8t sram存储单元的结构示意图;

19.图5为本发明实施例所述四输入灵敏放大器的结构示意图;

20.图6为本发明实施例所提供电路结构的时序波形图;

21.图7为55nm cmos工艺下采用传统sa的传统sram电路(以下简称为conv)和本发明实施例所提供的电路在不同位线泄漏电流情况下的读取时间图;

22.图8为55nm cmos工艺下采用传统sa的传统sram电路和本发明实施例所提供的电路在不同工艺角下所能承受的最大位线泄漏电流对比图;

23.图9为55nm cmos工艺下采用传统sa的传统sram电路和本发明实施例所提供的电路在不同工艺角下,当位线上存在最大泄漏电流时读取数据所需要的时间对比图。

具体实施方式

24.下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例,这并不构成对本发明的限制。基于本发明的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明的保护范围。

25.如图3所示为本发明实施例所述位线泄漏电流、灵敏放大器及存储器的的控制电路结构示意图,所述控制电路包括由8t sram存储单元构成的存储阵列和具有对称结构的

四输入灵敏放大器(图3中的sa_4in),其中:

26.所述存储阵列的两对传输管分别与主位线对和副位线对连接;其中,所述主位线对包括主位线blm和blmb;所述副位线对包括副位线bln和blnb;

27.一列存储单元中连接同一侧存储节点的一根主位线blm和一根副位线blnb分别与所述四输入灵敏放大器两侧的一个输入端连接,其中:

28.所述四输入灵敏放大器中已与副位线blnb连接的一侧的输入端与另一根主位线blmb连接,已与主位线blm连接的一侧的输入端与另一根副位线bln连接;

29.当所述主位线对中的一根主位线上有泄漏电流时,所述副位线对中与这根主位线连接在同一侧存储节点的副位线也产生等量的泄漏电流;因此,在所述四输入灵敏放大器读取数据时,一侧位线的泄漏电流造成的电压降能在另一侧得到实时补偿,进而读出正确数据,实现对位线泄漏电流的控制。

30.如图4所示为本发明实施例所述8t sram存储单元的结构示意图,所述存储阵列中的8t sram存储单元由2个pmos管和6个nmos管组成,2个pmos管记为p0和p1,6个nmos管记为n0~n5,其中:

31.pmos管p0的栅极与nmos管n2的栅极连接,源极与电源vdd连接;

32.pmos管p1的栅极与nmos管n3的栅极连接,源极与vdd连接;

33.nmos管n0的栅极接字线wl,漏极接主位线blm,源极分别与pmos管p0的漏极、nmos管n2的漏极、pmos管p1的栅极、nmos管n3的栅极和nmos管n5的源极连接;

34.nmos管n1的栅极接字线wl,漏极接另一主位线blmb,源极分别与pmos管p0的栅极、pmos管p1的漏极、nmos管n2的栅极、nmos管n3的漏极和nmos管n4的源极连接;

35.nmos管n2的栅极分别与pmos管p0的栅极、pmos管p1的漏极、nmos管n1的源极、nmos管n3的漏极和nmos管n4的源极连接,源极与地面vss连接;

36.nmos管n3的栅极分别与pmos管p0的漏极、pmos管p1的栅极、nmos管n0的源极、nmos管n2的漏极和nmos管n5的源极连接,源极与vss连接;

37.nmos管n4的栅极与vss连接,漏极与副位线bln连接;

38.nmos管n5的栅极与vss连接,漏极与另一副位线blnb连接。

39.如图5所示为本发明实施例所述四输入灵敏放大器的结构示意图,所述四输入灵敏放大器由4个pmos管和7个nmos管组成,4个pmos管记为p0~p3,7个nmos管记为n0~n6,其中:

40.pmos管p0的栅极与预充信号pre连接,源极与电源vdd连接;

41.pmos管p1的栅极与nmos管n0的栅极连接,源极与vdd连接;

42.pmos管p2的栅极与nmos管n1的栅极连接,源极与vdd连接;

43.pmos管p3的栅极与预充信号pre连接,源极分别与pmos管p0的源极、pmos管p1的源极、pmos管p2的源极和vdd连接;

44.nmos管n0的栅极分别与pmos管p1的栅极、pmos管p2的漏极、pmos管p3的漏极和nmos管n1的漏极连接,漏极分别与pmos管p0的漏极、pmos管p1的漏极、pmos管p2的栅极和nmos管n1的栅极连接;

45.nmos管n1的栅极分别与pmos管p0的漏极、pmos管p1的漏极、pmos管p2的栅极和nmos管n0的漏极连接,漏极分别与pmos管p1的栅极、pmos管p2的漏极、pmos管p3的漏极和

nmos管n0的栅极连接;

46.nmos管n2的栅极与主位线blm连接,漏极与nmos管n0的源极和nmos管n3的漏极连接;

47.nmos管n3的栅极与副位线bln连接,漏极与nmos管no的源极和nmos管n2的漏极连接;

48.nmos管n4的栅极与另一副位线blnb连接,漏极与nmos管n1的源极和nmos管n5的漏极连接;

49.nmos管n5的栅极与另一主位线blmb连接,漏极与nmos管n1的源极和nmos管n4的漏极连接;

50.nmos管n6的栅极与使能信号saen连接,漏极分别与nmos管n2的源极、nmos管n3的源极、nmos管n4的源极和nmos管n5的源极连接,源极与地面vss连接。

51.具体实现中,基于所述控制电路的结构:

52.在读操作开始时,先将主位线blm和blmb,以及副位线bln和blnb都预充到电源vdd,由于主位线blm上存在泄漏电流,设为i

leakage0

,主位线blm的电压v

blm

由vdd下降为vdd-δv1,δv1是泄漏电流i

leakage0

引起的主位线blm的电压v

blm

下降的幅度;同时,由于副位线blnb与主位线blm连接的是相同一侧的存储节点,副位线blnb上存在的泄漏电流与主位线blm上存在的泄漏电流大小相等,均为i

leakage0

,因此副位线blnb的电压v

blnb

也由vdd下降为vdd-δv1,即v

blm

=v

blnb

;

53.另一方面,由于主位线blmb上存在泄漏电流,设为i

leakage1

,主位线blmb的电压v

blmb

由vdd下降为vdd-δv2,δv2是泄漏电流i

leakage1

引起的主位线blmb的电压v

blmb

下降的幅度;同时,由于副位线bln与主位线blmb连接的是相同一侧的存储节点,副位线bln上存在的泄漏电流与主位线blmb上存在的泄漏电流大小相等,均为i

leakage1

,因此,副位线bln的电压v

bln

也由vdd下降为vdd-δv2,即v

blmb

=v

bln

;

54.如图6所示为本发明实施例所提供电路结构的时序波形图,其中pre为预充信号,wl为字线信号,saen为四输入灵敏放大器(sa_4in)的使能信号,在开启字线wl后,如果存储节点q存储的数据为”0”,则主位线blm上存在位线放电电流i

cell0

,导致主位线blm的电压v

blm

降低,而副位线blnb的电压v

blnb

不变,因此有v

blm

<v

blnb

,v

blmb

=v

bln

;由于主位线blm和副位线bln接在所述四输入灵敏放大器左侧的两个输入端口,而主位线blnb和副位线blmb接在所述四输入灵敏放大器右侧的两个输入端口,且因为所述四输入灵敏放大器两侧的输入端口对称,所以在开启使能信号saen时,所述四输入灵敏放大器的输出节点out的放电速度将大于输出节点outb的放电速度,其中,在预充阶段输出节点out和输出节点outb均预充到vdd;输出节点out的电压快速下降到0,而输出节点outb的电压将保持为vdd,从而产生输出信号,完成数据读取;

55.如果存储节点q存储的数据为”1”,则主位线blmb上存在位线放电电流i

cell1

,导致主位线blmb的电压v

blmb

降低,而副位线bln的电压v

bln

不变,因此有v

blmb

<v

bln

,v

blm

=v

blnb

;所以在开启使能信号saen时,所述四输入灵敏放大器的输出节点out的放电速度将小于输出节点outb的放电速度,输出节点outb的电压快速下降到0,而输出节点out的电压将保持为vdd,从而产生输出信号,完成数据读取。

56.值得注意的是,本发明实施例中未作详细描述的内容属于本领域专业技术人员公

知的现有技术。

57.为了更加清晰地展现出本发明所提供的技术方案以及所产生的技术效果,下面将结合附图将本发明实施例所提供的电路结构的性能与传统sram和sa电路进行对比,其具体内容如下:

58.(1)如图7所示为55nm cmos工艺下采用传统sa的传统sram电路(以下简称为conv)和本发明实施例所提供的电路在不同位线泄漏电流情况下的读取时间图,由图7可以看出:在1.2v电源电压、tt工艺角、25℃的仿真条件下,结果显示,当泄漏电流比较小时,采用传统sa的传统sram电路的读取时间要比本发明实施例所提供的电路结构略小一点。但是当泄漏电流增大到10ua左右时,采用传统sa的传统sram电路的读取时间要大于本发明实施例所提供的电路结构,并且当泄漏电流进一步增大时,采用传统sram结构的读取时间将快速增大,而采用本发明实施例所提供的电路结构的读取时间基本不变,甚至呈减小的趋势,并且在相同泄漏电流的情况下,采用传统sram结构的读取时间远大于采用本发明实施例所提供的电路结构的读取时间。

59.(2)如图8所示为55nm cmos工艺下采用传统sa的传统sram电路和本发明实施例所提供的电路在不同工艺角下所能承受的最大位线泄漏电流对比图,由于本发明实施例所提供的电路结构在主位线存在任意大小的泄漏电流时,都能读出正确的数据,但实际电路中,过大的泄漏电流还会引起对存储节点数据的读破坏。因此在测试电路结构在不同工艺角下所能承受的最大主位线泄漏电流时,取的是在不发生读破坏的情况下电路结构可承受的最大主位线泄漏电流。由图8可以看出:在1.2v电源电压、25℃的仿真条件下,在不同工艺角下本发明实施例所提供的电路结构相比于传统sram电路,在承受位线泄漏电流的能力上皆有所提高,提高最大的是在ss工艺角下,电路结构承受泄漏电流的能力增加了156.6%。

60.(3)如图9所示为55nm cmos工艺下采用传统sa的传统sram电路和本发明实施例所提供的电路在不同工艺角下,当位线上存在最大泄漏电流时读取数据所需要的时间对比图。其中,ss工艺角下,conv和该结构的位线泄漏电流分别是是22.4ua和57.49ua;tt工艺角下,conv和该结构的位线泄漏电流分别是是34.71ua和56.68ua;ff工艺角下,conv和该结构的位线泄漏电流分别是是50.42ua和63.15ua。由图9可以看出:在1.2v电源电压、25℃的仿真条件下,在不同工艺角下,当位线上存在最大泄漏电流时,本发明实施例所提供的电路结构读取数据的时间比传统sram电路大幅减少,读取时间最大减少了81.2%。

61.(4)如下表1所示,为在1.2v电源电压、tt工艺角、25℃的仿真条件下,本发明实施例所提供的电路在不同主位线泄漏,不同存储数据的情况下,读取q节点数据时sa_4in的数据输出情况:

62.表1

63.主位线泄漏对比q、qb节点存储数据sa_4in输出out输出数据blm泄漏较大(0,1)00blm泄漏较大(1,0)11blmb泄漏较大(0,1)00blmb泄漏较大(1,0)11

64.由表1可以看出:在1.2v电源电压、tt工艺角、25℃的仿真条件下,结果显示,当主位线blm上存在的泄漏电流比主位线blmb大时,如果存储节点q为”0”,sa_4in的输出out=

0,电路输出数据为”0”;如果存储节点q为”1”,sa_4in的输出out=1,电路输出数据为”1”。当主位线blmb上存在的泄漏电流比主位线blm大时,如果存储节点q为”0”,sa_4in的输出out=0,电路输出数据为”0”;如果存储节点q为”1”,sa_4in的输出out=1,电路输出数据为”1”。

65.综上所述,本发明实施例所提供的控制电路能够有效的抵抗位线泄漏电流造成的影响,相比于传统sram电路结构,可以显著减少读取数据的时间,提高了sram读操作的速度;并且提高了sram抵抗位线泄漏电流的能力,避免了传统sram在读操作时由于泄漏电流导致的读出错误数据的问题,提高了sram读取数据的稳定性。

66.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明披露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求书的保护范围为准。本文背景技术部分公开的信息仅仅旨在加深对本发明的总体背景技术的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域技术人员所公知的现有技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1