存储设备、存储设备的操作方法以及控制器的操作方法与流程

本公开涉及存储设备、存储设备的操作方法以及控制器的操作方法。

背景技术:

1、包括非易失性存储器件的存储设备可以用在通用串行总线(usb)驱动器、数码相机、移动电话、智能手机、平板个人计算机(pc)、pc、内存卡、固态硬盘(ssd)等中。存储设备可以被用来存储或移动大量数据。近来,存储设备已经被小型化并且以嵌入的形式实现于电子设备中。

技术实现思路

1、本公开的各方面提供了在读取操作中具有减少的读取延迟的控制器、包括该控制器的存储设备及其操作方法。

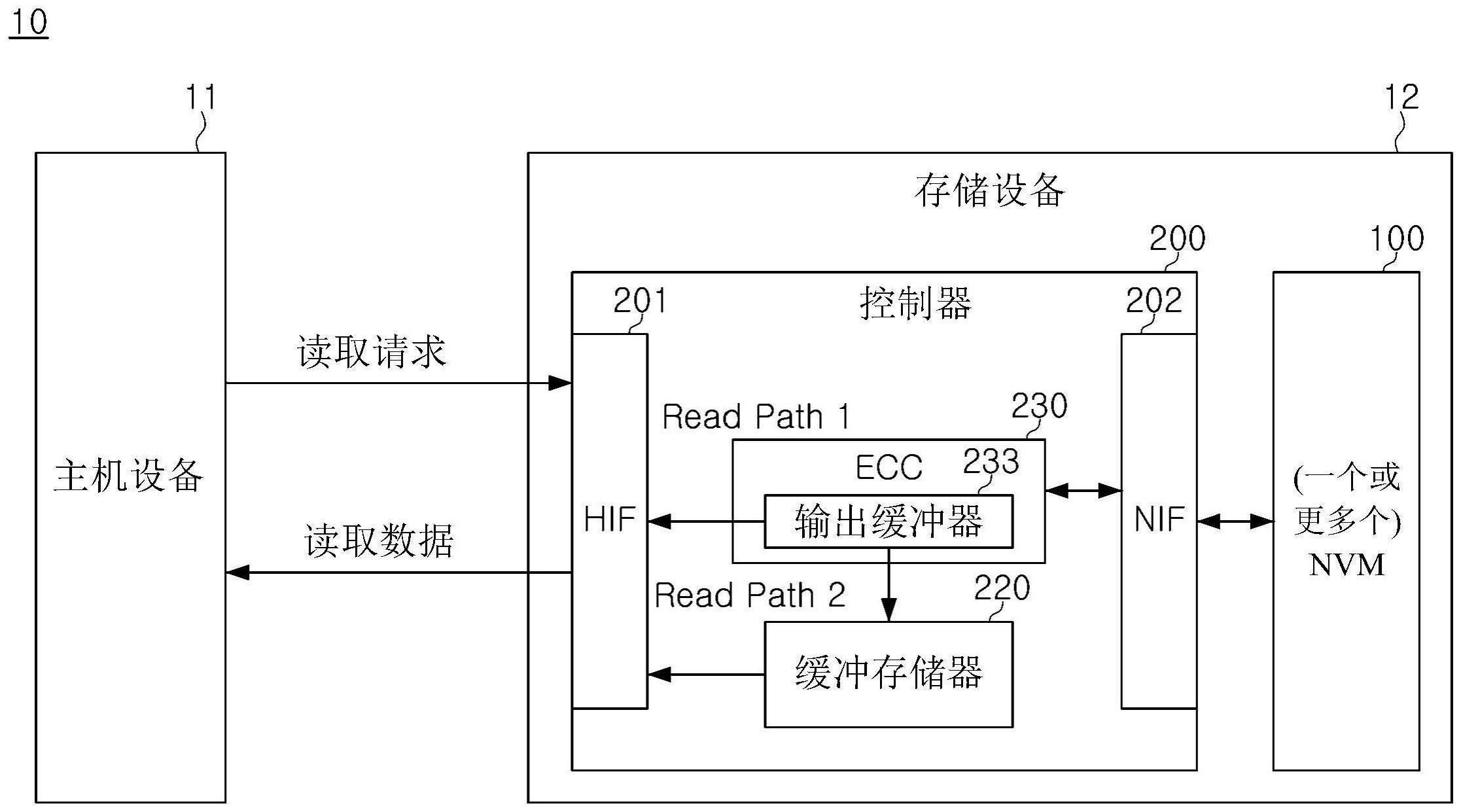

2、根据示例实施例的一方面,一种存储设备的操作方法包括:从主机设备接收主机读取命令;识别与所述主机读取命令对应的读取路径是否对应于第一直接存储器访问(dma)读取路径;以及基于所述读取路径对应于所述第一dma读取路径,通过主机dma管理器,将存储在纠错电路的输出缓冲器中的读取数据直接输出到所述主机设备。

3、根据示例实施例的一方面,一种控制器的操作方法,所述控制器被配置为控制非易失性存储器件,所述操作方法包括:从主机设备接收读取请求;根据所述读取请求的属性来识别读取路径;将与所述读取请求对应的读取命令发送到所述非易失性存储器件;从所述非易失性存储器件接收与所述读取命令对应的读取数据;对所述读取数据执行纠错操作,以获得纠错后的读取数据;以及根据所述读取路径来执行1级直接存储器访问(dma)操作和2级dma操作当中的一者,以将所述纠错后的读取数据提供给所述主机设备。

4、根据示例实施例的一方面,一种存储设备包括:至少一个非易失性存储器件;以及控制器,所述控制器被配置为控制所述至少一个非易失性存储器件。所述控制器包括:主机接口电路,所述主机接口电路被配置为与主机设备接口连接;非易失性存储器接口电路,所述非易失性存储器接口电路被配置为与所述至少一个非易失性存储器件接口连接;纠错电路,所述纠错电路被配置为纠正从所述至少一个非易失性存储器件读取的读取数据的错误并将所述读取数据存储在输出缓冲器中,并且基于读取路径是第一读取路径,在主机直接存储器访问(dma)管理器的控制下,将存储在所述输出缓冲器中的第一读取数据输出到所述主机接口电路;以及缓冲存储器,所述缓冲存储器被配置为从所述纠错电路的所述输出缓冲器接收所述第一读取数据,并且基于所述读取路径是第二读取路径,在所述主机dma管理器的控制下,将第二读取数据输出到所述主机接口电路。

5、根据示例实施例的一方面,一种控制器,其中,所述控制器被配置为控制至少一个非易失性存储器件,所述控制器包括:至少一个处理器;主机接口电路,所述主机接口电路被配置为与主机设备接口连接;非易失性存储器接口电路,所述非易失性存储器接口电路被配置为与所述至少一个非易失性存储器件接口连接;缓冲存储器;纠错电路,所述纠错电路包括输出缓冲器,其中,所述纠错电路被配置为纠正从所述至少一个非易失性存储器件读取的数据中的错误;主机直接存储器访问(dma)电路,所述主机dma电路被配置为通过所述主机接口电路直接访问所述纠错电路的所述输出缓冲器和所述缓冲存储器;以及,非易失性存储器(nvm)dma电路,所述nvm dma电路被配置为通过所述非易失性存储器接口电路直接访问所述至少一个非易失性存储器件。所述主机dma电路还被配置为基于读取路径对应于1级dma操作,直接获得存储在所述纠错电路的所述输出缓冲器中的读取数据,并将所述读取数据提供给所述主机接口电路。所述主机dma电路还被配置为基于所述读取路径对应于2级dma操作,控制将存储在所述纠错电路的所述输出缓冲器中的读取数据存储到所述缓冲存储器中,从所述缓冲存储器获得所述读取数据并将所述缓冲存储器的数据输出到所述主机接口电路。

技术特征:

1.一种存储设备的操作方法,所述操作方法包括:

2.根据权利要求1所述的操作方法,所述操作方法还包括:

3.根据权利要求1所述的操作方法,其中,所述的识别包括:根据所述主机读取命令的属性来选择所述读取路径。

4.根据权利要求1所述的操作方法,其中,所述的识别包括:识别所述主机读取命令是否是随机读取命令。

5.根据权利要求1所述的操作方法,其中,所述的识别包括:读取指示所述第一dma读取路径的sfr,所述sfr即特殊特征寄存器。

6.根据权利要求5所述的操作方法,所述操作方法还包括:设置所述sfr。

7.根据权利要求5所述的操作方法,所述操作方法还包括:根据来自所述主机设备的请求来设置所述sfr。

8.根据权利要求5所述的操作方法,所述操作方法还包括:根据所述存储设备的内部策略来设置所述sfr。

9.根据权利要求1所述的操作方法,所述操作方法还包括:在非易失性dma管理器的控制下,将所述读取数据从非易失性存储器件直接发送到所述纠错电路。

10.根据权利要求1所述的操作方法,其中,所述输出缓冲器包括低密度奇偶校验电路的静态随机存取存储器。

11.一种控制器的操作方法,所述控制器被配置为控制非易失性存储器件,所述操作方法包括:

12.根据权利要求11所述的操作方法,其中,所述读取请求的属性是基于接收到的地址被确定的,并且指示所述读取请求是否是随机读取请求。

13.根据权利要求11所述的操作方法,其中,用于所述1级dma操作的第一读取路径或用于所述2级dma操作的第二读取路径被设置在sfr中,所述sfr即特殊特征寄存器,并且识别所述读取路径包括读取所述sfr。

14.根据权利要求13所述的操作方法,所述操作方法还包括:根据来自所述主机设备的请求或根据内部策略来设置所述sfr。

15.根据权利要求11所述的操作方法,其中,所述的执行所述1级dma操作包括:将所述纠错后的读取数据从纠错电路的输出缓冲器直接发送到所述主机设备,并且

16.一种存储设备,包括:

17.根据权利要求16所述的存储设备,其中,所述控制器还被配置为从所述第一读取路径和所述第二读取路径当中选择一个读取路径作为所述读取路径。

18.根据权利要求16所述的存储设备,其中,所述控制器进一步被配置为:基于从所述主机设备接收到的地址来识别读取请求是否是随机读取请求,并且基于所述读取请求是所述随机读取请求,选择所述第一读取路径作为所述读取路径。

19.根据权利要求16所述的存储设备,其中,所述控制器还包括:特殊特征寄存器,所述特殊特征寄存器被配置为存储指示所述读取路径是所述第一读取路径还是所述第二读取路径的值。

20.根据权利要求16所述的存储设备,其中,所述缓冲存储器是静态随机存取存储器。

技术总结

提供存储设备、存储设备的操作方法以及控制器的操作方法。所述存储设备的操作方法包括:从主机设备接收主机读取命令;识别与所述主机读取命令对应的读取路径是否对应于第一直接存储器访问(DMA)读取路径;以及基于所述读取路径对应于所述第一DMA读取路径,通过主机DMA管理器,将存储在纠错电路的输出缓冲器中的读取数据直接输出到所述主机设备。

技术研发人员:崔镜隐,郑宇圣

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!