运用于非易失性存储器的感测元件的制作方法

本发明是有关于一种感测元件(sensing device),且特别是有关于一种运用于非易失性存储器(non-volatile memory)的感测元件。

背景技术:

1、众所周知,非易失性存储器(non-volatile memory)已经非常广泛的应用于各种电子产品。例如sd卡、固态硬碟(solid state drive,简称ssd)等等。基本上,在非易失性存储器内的存储器阵列(memory array)中包括多个存储单元(memory cell)。而每个存储单元中皆会有一个浮动栅极晶体管(floating gate transistor)。其中,浮动栅极晶体管中的浮动栅极(floating gate)可以储存热载子(hot carrier),而根据热载子储存量的多寡即可决定该浮动栅极晶体管的储存状态。再者,浮动栅极晶体管也可称为储存晶体管(storage transistor)。

2、一般来说,当热载子注入浮动栅极晶体管后,浮动栅极晶体管的阈值电压(threshold voltage,简称vt)会根据热载子注入的数量而改变。因此,具有较高的阈值电压的浮动栅极晶体管需要较高的栅极电压(gate voltage)来开启(turn on)浮动栅极晶体管;反之,具有较低的阈值电压的浮动栅极晶体管则可以用较低的栅极电压来开启浮动栅极晶体管。

3、于非易失性存储器的编程周期(program cycle)时,可控制注入浮动栅极的热载子量,进而改变浮动栅极晶体管的阈值电压。而在感测周期(sense cycle)时,提供一读取电压(read voltage)至浮动栅极晶体管,便可以产生存储单元电流(cell current),或称为读取电流(read current)。而根据存储单元电流的大小,即可得知该浮动栅极晶体管(亦即存储单元)的储存状态为开启状态(on state)或者关闭状态(off state)。

4、举例来说,当读取电压提供至具备低阈值电压的浮动栅极晶体管,则此浮动栅极晶体管会成为开启状态,进而产生较高的存储单元电流(cell current)。反之,当读取电压提供至具备高阈值电压的浮动栅极晶体管,则此浮动栅极晶体管会无法开启而成为关闭状态,进而产生近于零的存储单元电流。也就是说,在感测周期时,开启状态的存储单元产生较高的存储单元电流;而关闭状态的存储单元产生较低的存储单元电流。

5、当然,非易失性存储器中更需要提供一感测元件(sensing device),用以接收存储单元产生的存储单元电流,并判断存储单元中的储存状态。

6、请参照第1图,其所绘示为已知感测元件示意图。感测元件100包括晶体管m1、晶体管m2、电流源(current source)110、运算放大器120与判断元件(judging element)130。

7、晶体管m1与运算放大器120连接形成一电压箝位电路(voltage clampingcicuit),其中晶体管m1的漏极连接至数据线(data line,dl)以接收存储单元输出的存储单元电流icell,晶体管m1的栅极连接至运算放大器120输出端,晶体管m1的源极接收接地电压gnd。再者,运算放大器120的第一输入端接收一箝位电压(clamping voltage)vclp,运算放大器120的第二输入端连接至晶体管m1的漏极。因此,当电压箝位电路正常运作状态时,晶体管m1漏极上的数据线电压(data line voltage)vdl等于箝位电压vclp。

8、电流源110连接于供应电压vdd与判断节点(judging node)s之间,电流源110可产生一参考电流iref。晶体管m2的漏极连接至判断节点s,晶体管m2的漏极接收参考电流iref,晶体管m2的栅极连接至晶体管m1的栅极,晶体管m2的源极接收接地电压gnd。其中,供应电压vdd大于箝位电压vclp,箝位电压vclp大于接地电压gnd。例如,供应电压vdd为3.3v~5v,箝位电压vclp为0.2v~0.4v。

9、再者,判断元件130的输入端连接至判断节点s用以接收判断节点上的判断电压(judging voltage)vjudge,判断元件130的输出端产生输出数据dout。举例来说,判断元件130包括逻辑缓冲器(logic buffer)132、134,串接于判断元件130的输入端与输出端之间。因此,在感测周期时,可根据判断元件130的输出数据dout来判断存储单元为开启状态或者关闭状态。其中,每一个逻辑缓冲器132、134可利用二个非门(not gate)串接而成。

10、在感测周期时,数据线dl会连接至存储单元并且接收存储单元电流icell。当数据线dl上的存储单元电流icell大于参考电流iref时,判断电压vjudge会被下拉(pull down)至接地电压gnd,因此判断元件130输出第一逻辑电平(例如逻辑低电平)的输出数据dout,代表存储单元为开启状态(on state)。反之,当数据线dl上的存储单元电流icell小于参考电流iref时,判断电压vjudge会被上拉(pull up)至供应电压vdd,因此判断元件130输出第二逻辑电平(例如逻辑高电平)的输出数据dout,代表存储单元为关闭状态(off state)。

11、由以上的说明可知,感测元件100可根据存储单元产生的存储单元电流icell来判断该存储单元的储存状态。

12、然而,已知感测元件100有其缺陷。如上所述,感测元件100的运算放大器120连接至数据线dl。由于运算放大器120连接成一负反馈放大器(negative feedbackamplifier),放大器的高增益(high gain)也会将噪声放大,并影响判断节点s的判断电压vjudge。举例来说,放大器将接地端噪声(ground noise)放大,造成判断节点s的判断电压vjudge不稳定,使得判断元件130误判。

技术实现思路

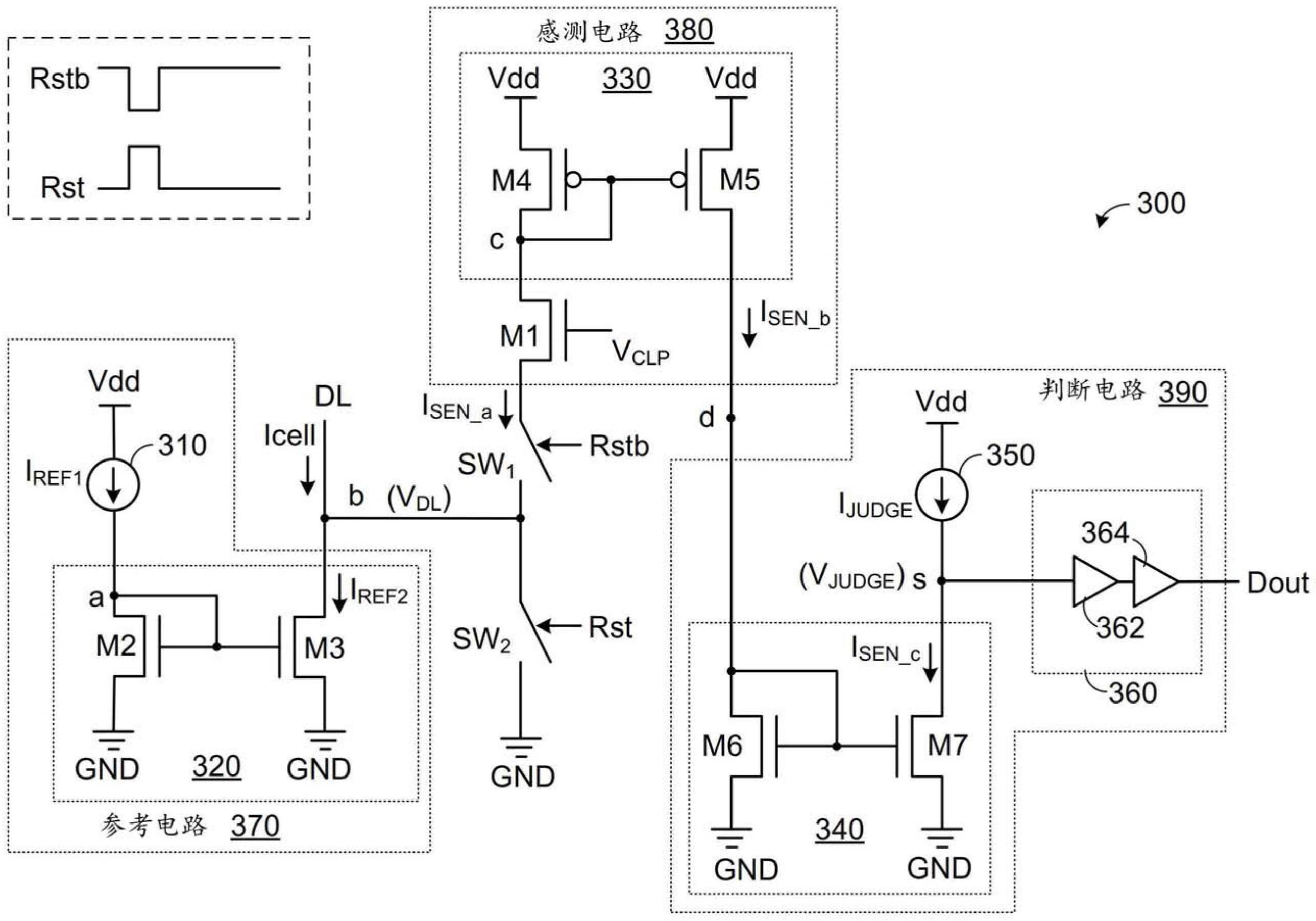

1、本发明是有关于一种运用于非易失性存储器的一感测元件,该非易失性存储器包括一存储单元,于一感测周期时,该存储单元连接至一数据线,该感测元件包括:一第一电流源,该第一电流源连接于一供应电压与一第一节点之间,该第一电流源产生一参考电流;一第一电流镜,该第一电流镜的一输入端连接至该第一节点,该电流镜的一镜射端连接至一第二节点,且该第二节点连接至该数据线;一第一开关,该第一开关的一第一端连接至该第二节点,该第一开关的一控制端接收一反相重置脉冲;一第二开关,该第二开关的一第一端连接至该第二节点,该第二开关的一第二端接收一接地电压,该第二开关的一控制端接收一重置脉冲;一第一晶体管,该第一晶体管的一漏极连接至一第三节点,该第一晶体管的一源极连接至该第一开关的一第二端,该第一晶体管的一栅极接收一箝位电压;一第二电流镜,该第二电流镜的一输入端连接至该第三节点,该第二电流镜的一镜射端连接至一第四节点;一第三电流镜,该第三电流镜的一输入端连接至该第四节点,该第三电流镜的一镜射端连接至一判断节点;一第二电流源,该第二电流源连接于该供应电压与该判断节点之间,该第二电流源产生一判断电流;以及,一判断元件,该判断元件的一输入端连接至判断节点,该判断元件的一输出端产生一输出数据。

2、本发明是有关于一种运用于非易失性存储器的一感测元件,该非易失性存储器包括一存储单元,于一感测周期时,该存储单元连接至一数据线并产生一存储单元电流至一第一节点,该感测元件包括:一参考电路,连接至该第一节点,且该参考电路提供一参考电流;一第一开关,该第一开关的一第一端连接至该第一节点,该第一开关的一控制端接收一反相重置脉冲;一第二开关,该第二开关的一第一端连接至该第一节点,该第二开关的一第二端接收一接地电压,该第二开关的一控制端接收一重置脉冲,其中该重置脉冲与该反相重置脉冲为互补的关系;一感测电路,连接于该第一开关的一第二端与一第二节点之间,该感测电路根据该存储单元电流与该参考电流的差异来产生一第一感测电流;一判断电路,连接至该第二节点,该判断电路接收该第一感测电流,并根据该第一感测电流来产生一输出数据;其中,当该存储单元的一存储单元电流大于该参考电流时,该第一感测电流实质上等于零,且该输出数据为一第一逻辑电平;其中,当该存储单元的一存储单元电流小于该参考电流时,该第一感测电流大于零,且该输出数据为一第二逻辑电平。

- 还没有人留言评论。精彩留言会获得点赞!