负电压控制电路、方法、存储器及电子设备与流程

本技术属于电子电路领域,具体涉及一种负电压控制电路、方法、存储器及电子设备。

背景技术:

1、近年来,随着手持设备的普及,对低功耗的要求越来越高,因此芯片的电压随之降低。低电压下,静态随机存取存储器(static random access memory,sram)的写操作失效率有所提升,存储单元不能存储正确的数据,导致芯片功能失效。因此,需要采用负电压数据线写辅助电路对sram存储器进行写操作,以此来提高写操作良率。

2、负电压数据线写辅助电路包括两个部分,负电压产生电路和负电压控制电路。负电压控制电路提供一根控制线来开启和关闭负电压产生电路。写操作时,控制线开启负电压产生电路,将数据线下拉到负电压以下,以此来提高写操作良率。

3、但是,现有的负电压控制电路对于存储器的写操作能力的提升不太理想。此外现有的负电压控制电路普遍结构复杂,面积较大,导致成本上升。

技术实现思路

1、鉴于此,本技术的目的在于提供一种负电压控制电路、方法存储器及电子设备,以改善现有负电压控制电路对于存储器的写操作能力提升不太理想,以及结构复杂的问题。

2、本技术的实施例是这样实现的:

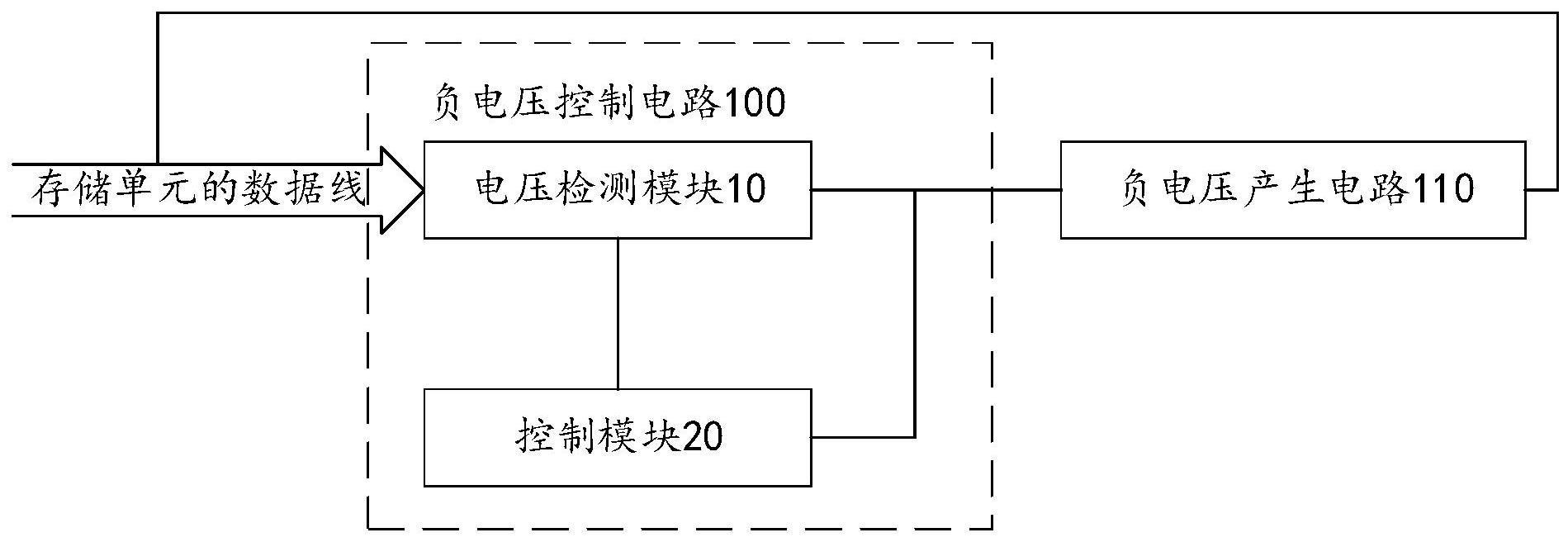

3、第一方面,本技术实施例提供了一种负电压控制电路,包括:电压检测模块和控制模块;电压检测模块,用于与存储单元的数据线连接,所述电压检测模块用于检测所述数据线的电压;控制模块,与所述电压检测模块以及负电压产生电路连接,所述控制模块用于当所述数据线的电压低于预设电压时,控制所述负电压产生电路的开启,以使所述负电压产生电路将所述数据线的电压下拉到负电压,其中,所述预设电压为所述存储单元能够写入数据0时的电压。

4、本技术实施例中,该负电压控制电路能够自动拟合存储单元的写电压,能有效的检测负电压产生电路的最佳开启时间,即当检测到数据线的电压下降到存储单元能够写入数据0的电压以下时,才控制负电压产生电路的开启,由于本技术实施例中数据线的电压需要下降到更低电压才开启负电压产生电路,使得数据线的下拉幅度更大(即下拉能力更强),进而有效的提升了存储单元的写操作良率。且电路结构简单,面积小,有效的节省了成本。

5、结合第一方面实施例的一种可能的实施方式,所述电压检测模块包括:反相器;所述反相器的输入端与所述存储单元的数据线连接,所述反相器的输出端及内部节点与所述控制模块连接;所述反相器用于检测所述数据线的电压,当所述数据线的电压低于所述反相器的翻转电压时,所述反相器输出高电平;所述控制模块,还用于调节所述反相器的翻转电压,使其小于所述预设电压,其中,所述控制模块用于检测到所述反相器的电压由低电平翻转为高电平时,控制所述负电压产生电路的开启。

6、本技术实施例中,利用反相器来检测数据线的电压,当反相器输入端的电压(即数据线的电压)为高电平时,反相器输出低电压,当反相器输入端的电压低于反相器的翻转电压时,反相器输出高电平,同时,通过控制模块来调节反相器的翻转电压,使翻转电压降低该预设电压,使得数据线的电压需要下降到更低电压,反相器才能翻转,以实现当数据线的电压低于预设电压时,控制负电压产生电路的开启的功能。由于反相器的结构简单,在使其在发明目的的同时,可以有效降低电路面积及实现成本。

7、结合第一方面实施例的一种可能的实施方式,所述反相器包括:第一pmos(positive channel metal oxide semiconductor,p沟道金属氧化物半导体)管、第二pmos管及第一nmos(negative channel metal oxide semiconductor,n沟道金属氧化物半导体)管;所述第一pmos管的源极与电源连接,所述第一pmos管的漏极与所述第二pmos管的源极连接,所述第二pmos管的漏极与所述第一nmos管的漏极连接,所述第一nmos管的源极接地;所述第一pmos管的栅极、所述第二pmos管的栅极、所述第一nmos管的栅极均与所述存储单元的数据线连接,所述第二pmos管的漏极及源极还与所述控制模块连接;其中,通过所述控制模块将所述第二pmos管源极的电压拉低,以降低所述第二pmos的阈值电压,使得所述第二pmos管导通时的数据线电压小于所述第一pmos管导通时的数据线电压。

8、本技术实施例中,采用上述三个晶体管来构成反相器,当第一pmos管导通时,通过控制模块来下拉第二pmos管的阈值电压,使得第二pmos管导通时的数据线电压小于第一pmos管导通时的数据线电压,也即数据线电压需要下降到更低电压(低于存储单元能够写入数据0的电压以下),第二pmos管才能导通,从而才能使第二pmos管的漏极翻转为高电压,以实现在最佳时间开启负电压产生电路,将存储单元的数据线下拉到负电压。由于晶体管具有体积小、成本低等优点,从而使得该负电压控制电路的面积及成本进一步减少。

9、结合第一方面实施例的一种可能的实施方式,所述控制模块包括用于调节所述第二pmos的阈值电压的调节开关;所述调节开关的第一端与所述电压检测模块的内部节点连接,所述调节开关的控制端与所述电压检测模块的输出端,以及所述负电压产生电路连接,所述调节开关的第二端接地。

10、本技术实施例中,采用调节开关来调节电压检测模块的内部节点的电压,从而实现当数据线的电压低于预设电压(存储单元能够写入数据0时的电压),这一最佳时间开启负电压产生电路,能加强存储器的写操作能力。在实现其发明目的的同时,可以使电路结构更简单、成本更低廉,从而增加了实用性。

11、结合第一方面实施例的一种可能的实施方式,所述负电压控制电路包括:第一pmos管、第二pmos管、第一nmos管、第三pmos管;所述第一pmos管的源极与电源连接,所述第一pmos管的漏极与所述第二pmos管的源极连接,所述第二pmos管的漏极与所述第一nmos管的漏极连接,所述第一nmos管的源极接地;所述第一pmos管的栅极、所述第二pmos管的栅极、所述第一nmos管的栅极均与所述存储单元的数据线连接,所述第二pmos管的漏极还与所述第三pmos管的栅极连接,所述第三pmos管的源极与所述第二pmos管的源极连接,所述第三pmos管的源极接地,所述第三pmos管的栅极还与所述负电压产生电路连接。

12、本技术实施例中,采用上述结构的负电压控制电路,可以在增强存储单元的写操作良率的同时,能最大程度的电路面积及设计成本。

13、结合第一方面实施例的一种可能的实施方式,所述第一pmos管的尺寸、所述第二pmos管的尺寸与所述存储单元的上拉晶体管的尺寸一致;和/或所述第一nmos管的尺寸与所述存储单元的下拉晶体管的尺寸一致。

14、本技术实施例中,因第一pmos管、第二pmos管和/或第一nmos管和存储单元的器件类型和尺寸一致,因此其电器特性和存储单元的电路特性一致或接近,使得电压检测更准确。

15、第二方面,本技术实施例还提供了一种存储器,包括:存储器电路和写辅助电路,所述写辅助电路包括负电压产生电路和如上述第一方面实施例和/或结合第一方面实施例的任一种可能的实施方式提供的负电压控制电路,所述负电压控制电路与所述负电压产生电路连接。

16、第三方面,本技术实施例还提供了一种电子设备,包括处理器及如上述的存储器。

17、第四方面,本技术实施例还提供了一种负电压控制方法,包括:检测存储单元的数据线的电压;当所述数据线的电压低于预设电压时,控制所述负电压产生电路的开启,以使所述负电压产生电路将所述数据线的电压下拉到负电压;其中,所述预设电压为所述存储单元能够写入数据0的电压。

18、本技术的其他特征和优点将在随后的说明书阐述。本技术的目的和其他优点可通过在所写的说明书以及附图中所特别指出的结构来实现和获得。

- 还没有人留言评论。精彩留言会获得点赞!