晶片外驱动器结构的制作方法

1.本发明是有关于一种晶片外驱动器(off chip driver,ocd)结构,且特别是具有静电保护电路的晶片外驱动器结构。

背景技术:

2.一般在输入输出垫片(input/output pad)的设计中,静电放电(electrostatic discharge,esd)保护电路和晶片外驱动器(off chip driver,ocd)电路通常以围绕垫片的方式设置,且为了充足的静电放电保护表现及驱动讯号的能力而具有较大布局面积。

3.随着先进技术中晶片尺寸的缩小,由于布局面积的限制,静电放电保护电路和晶片外驱动器的布局设计更加困难。因此,如何在有效保护内部电路的同时减小布局面积是本领域的重要课题。

技术实现要素:

4.本发明的目的在于提供一种晶片外驱动器结构,其可减少晶片外驱动器电路的整体布局面积。

5.本发明的一实施例是关于一种晶片外驱动器结构。晶片外驱动器结构包含多个上拉晶体管、多个下拉晶体管、多个第一类型的第一区域、多个第二类型的第二区域,以及多个电阻元件。第一区域和第二区域交错形成静电保护电路。多个电阻元件中的一个耦接上拉晶体管中的一个或下拉晶体管中的一个。电阻元件配置在第一区域和第二区域之间。

6.在部分实施例中,电阻元件由多晶硅或金属构成。

7.在部分实施例中,电阻元件由多晶硅或金属构成,电阻中每一个的电阻值是能根据多晶硅和金属的长度比例而调整的。

8.在部分实施例中,晶片外驱动器结构还包含多个浅沟槽隔离结构,配置在第一区域和第二区域之间,其中电阻元件设置在浅沟槽隔离结构之上。

9.在部分实施例中,第一区域、第二区域和浅沟槽隔离结构设置在第一层,电阻元件设置在不同于第一层的第二层。

10.在部分实施例中,第一区域、第二区域、浅沟槽隔离结构和电阻元件为在第一方向上延伸而互相平行的条状区域。

11.在部分实施例中,在垂直于第一方向的第二方向上,第一区域和第二区域以交错方式设置。

12.在部分实施例中,在垂直于第一方向的第二方向上,第一区域和第二区域中每一个被浅沟槽隔离结构夹在中间。

13.在部分实施例中,在垂直于第一方向的第二方向上,浅沟槽隔离结构中每一个被第一区域中的一个和第二区域中的一个夹在中间。

14.在部分实施例中,耦接至上拉晶体管的电阻元件设置在用以接收第一电压的第二区域与耦接至垫片的第一区域之间,耦接至下拉晶体管的电阻元件设置在用以接收第二电

压的第一区域与耦接至垫片的第二区域之间。

15.综上所述,本发明的晶片外驱动器结构通过应用于上述各个实施例中,通过设置电阻元件在静电保护二极管的p型掺杂区和n型掺杂区之间,可减少晶片外驱动器电路的整体布局面积。

附图说明

16.图1是根据本发明的部分实施例所绘示的一种晶片外驱动器的电路示意图。

17.图2是根据本发明的部分实施例所绘示的一种具有静电保护二极管的上拉电路的示意图。

18.图3是根据本发明的图2实施例所绘示的一种静电保护二极管的剖面图。

19.图4是根据本发明的部分实施例所绘示的一种具有静电保护二极管的下拉电路的示意图。

20.图5是根据本发明的图4实施例所绘示的一种静电保护二极管的剖面图。

21.图6a~图6d是根据本发明的部分实施例所绘示的一种电阻元件的示意图。

22.主要附图标记说明:

23.100-晶片外驱动器电路,120-上拉电路,140-下拉电路,esd-静电保护电路,pn、np-静电保护二极管,pmos、nmos-晶体管,ru1~ru7、rn1~rn7-电阻,i/o-输入输出垫片,800-电源,900-接地,power-第一电压,gnd-第二电压,102、103、105、106-主动区,104、107-栅极,109-连接线,122、144-p型掺杂区,124、142-n型掺杂区,122a、142a-侧边区域,122b、124b、142b、144b-条状区域,126、146-浅沟槽隔离结构,128、148-电阻元件,n1、n2、n3、n4、n5、n6、n7、n8-金属接点,x、y、z-方向,a-a’、b-b

’-

切线,p_sub-p型基板,n_well-n型井,r1、r2、r3、r4-电阻元件,u1、u2、u3、u4-部件。

具体实施方式

24.具体实施方式现在将在下文中参考附图更全面地描述本发明,附图中示出了本发明的示例性实施例。然而,本发明可以以许多不同的形式实施,不应该被解释为限于此处阐述的实施例。提供这些实施例是为了使本发明彻底和完整,并且向本领域技术人员充分传达本发明的范围。相同的附图标记表示相同的元件。

25.本文所使用的所有词汇具有其通常的意涵。上述的词汇在普遍常用的字典中的定义,在本说明书的内容中包含任一在此讨论的词汇的使用例子仅为示例,不应限制到本发明的范围与意涵。同样地,本发明亦不仅以于此说明书所示出的各种实施例为限。

26.在本文中,使用第一、第二等等的词汇,是用于描述各种元件、组件、区域、层与/或区块是可以被理解的。但是这些元件、组件、区域、层与/或区块不应该被这些术语所限制。这些词汇只限于用来辨别单一元件、组件、区域、层与/或区块。因此,在下文中的第一元件、组件、区域、层与/或区块也可被称为第二元件、组件、区域、层与/或区块,而不脱离本发明的本意。

27.关于本文中所使用的“耦接”或“连接”,均可指二或多个元件相互直接作实体或电性接触,或是相互间接作实体或电性接触,亦可指二或多个元件相互操作或动作。

28.应当理解,当一个元件被称为在另一个元件“上”时,它可以直接在另一个元件上,

或者可以在它们之间存在中间元件。当一个元素被称为“直接在”另一个元素上时,不存在中间元素。如这里所使用的,术语“及/或”包括一个或多个相关所列项目的任何和所有组合。

29.请参考图1。图1是根据本发明的部分实施例所绘示的一种晶片外驱动器电路100的示意图。如图1所示,晶片外驱动器(off chip driver,ocd)电路100包含上拉电路120、下拉电路140和静电保护(electrostatic discharge,esd)电路esd。静电保护电路esd包含静电保护二极管pn和静电保护二极管np。上拉电路120包含多个第一晶体管(例如,图1中所示的第一晶体管pmos)和多个电阻(例如,电阻ru1~ru7)。下拉电路140包含多个第二晶体管(例如,图1中所示的第二晶体管nmos)和多个电阻(例如,电阻rn1~rn7)。

30.多个第一晶体管的第一端耦接至电源800并用以接收第一电压power。多个第一晶体管的第二端分别耦接至电阻ru1~ru7的一端。而电阻ru1~ru7的另一端耦接至输入输出垫片i/o。

31.相似地,多个第二晶体管的第一端耦接至接地900并用以接收第二电压gnd。多个第二晶体管的第二端分别耦接至电阻rn1~rn7的一端。电阻rn1~rn7的另一端耦接至输入输出垫片i/o。

32.静电保护二极管pn和上拉电路120以并联方式连接。静电保护二极管np和下拉电路140以并联方式连接。具体而言,静电保护二极管pn的n接面耦接至电源800并用以接收第一电压power。静电保护二极管pn的p接面和静电保护二极管np的n接面耦接至输入输出垫片i/o。静电保护二极管np的p接面耦接至接地900并用以接收第二电压gnd。

33.值得注意的是,绘示于图1中的七个第一晶体管、七个第二晶体管和十四个电阻仅为例子,并非用以限制本发明。本领域的技术人员可依实际需求调整晶体管和电阻的数量。

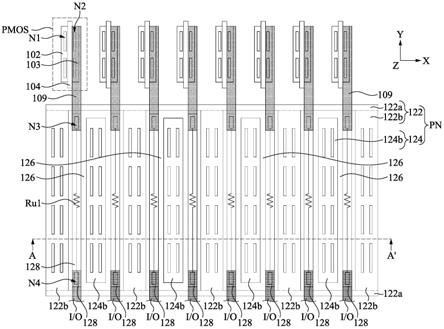

34.请一并参考图2和图3。图2是根据本发明的部分实施例所绘示的一种具有静电保护二极管pn的上拉电路120的示意图。图3是根据本发明的图2实施例所绘示的一种静电保护二极管pn的剖面图。为了方便且清楚说明,在多个第一晶体管中以标示第一晶体管pmos作为代表。相似地,在电阻ru1~ru7中以标示电阻ru1作为代表。

35.如图2所示,第一晶体管pmos由主动区102、103和栅极104所构成。电阻ru1由电阻元件128所构成。静电保护二极管pn由多个第一类型的第一区域(即,p型掺杂区122)和多个第二类型的第二区域(即,n型掺杂区124)所构成。换言之,在部分实施例中,第一类型是p型而第二类型是n型。然而,本发明不受到上述类型所限制,其他第一类型和第二类型的适当配置亦在本发明所涵盖的范围之内。

36.值得注意的是,在本发明说明书中p型或p型掺杂区是掺杂有三价杂质的区域,举例但不限于如半导体制造领域中已知的硼(b)、铝(al)和镓(ga)。此外,n型或n型掺杂区是掺杂有五价杂质的区域,举例但不限于如半导体制造领域已知的磷(p)、砷(as)和锑(sb)。

37.在部分实施例中,栅极104设置并横跨在主动区102和主动区103上方。主动区102配置在栅极104的第一侧,而主动区103设置在栅极104的第二侧。主动区102用以接收第一电压power。主动区103耦接至电阻元件128,而电阻元件128耦接至输入输出垫片i/o。

38.具体而言,主动区102经由金属接点n1耦接至电源800(未示于图2中)。主动区103经由金属接点n2耦接至连接线109。电阻元件128经由金属接点n3耦接至连接线109。电阻元件128经由金属接点n4耦接至输入输出垫片i/o。

39.如此一来,通过连接电阻元件128至主动区103和输入输出垫片i/o,电阻元件128能够实现连接至第一晶体管pmos和输入输出垫片i/o的电阻ru1。

40.如图2所示,静电保护二极管pn由p型掺杂区122和n型掺杂区124所构成。在部分实施例中,p型掺杂区122由一对侧边区域122a和多个条状区域122b所构成。n型掺杂区124由多个条状区域124b所构成。

41.结构上,如图2所示,一对侧边区域122a是一对细长并在x方向上延伸的条状区域。条状区域122b和条状区域124b在y方向上延伸并夹在一对侧边区域122a之间。此外,在x方向上,条状区域122b和条状区域124b以交错方式配置。

42.在部分实施例中,多个浅沟槽隔离结构(shallow trench isolations,sti)126连接在条状区域122b和条状区域124b之间。换言之,条状区域124b由浅沟槽隔离结构126所围绕,且浅沟槽隔离结构126被条状区域122b和侧边区域122a(即,p型掺杂区122)所围绕。

43.以不同角度说明,如图3所示,条状区域122b、条状区域124b和浅沟槽隔离结构126设置在p型基板p_sub上,而电阻元件128设置在浅沟槽隔离结构126之上。换言之,条状区域122b、条状区域124b和浅沟槽隔离结构126设置在第一层,而电阻元件128设置在不同于第一层的第二层。举例来说,电阻元件128可设置在第一金属层、第二金属层及/或第三金属层。

44.此外,如图3所示,条状区域122b和条状区域124b在x方向上以交错方式设置。换言之,每个条状区域122b和每个条状区域124b在x方向上被浅沟槽隔离结构126夹在中间,而每个浅沟槽隔离结构126在x方向上被夹在条状区域122b中的一个和条状区域124b中的一个之间。

45.如此一来,电阻元件128可设置在静电保护二极管pn的布局区域内。因此如图1所示的电阻ru1~ru7不需要占用额外的布局区域。也就是说,在相同尺寸的静电保护二极管pn的布局区域中,能设置静电保护二极管pn和电阻元件128。

46.请一并参考图4和图5。图4是根据本发明的部分实施例所绘示的一种具有静电保护二极管np的下拉电路140的示意图。图5是根据本发明的图4实施例所绘示的一种静电保护二极管np的剖面图。为了方便清楚说明,在多个第二晶体管中以标示第二晶体管nmos作为代表。相似地,在电阻rn1~rn7中以标示电阻rn1作为代表。

47.如图4所示,第二晶体管nmos由主动区105、106和栅极107所构成。电阻rn1由电阻元件148所构成。静电保护二极管np由多个第一类型的第一区域(即,p型掺杂区144)和多个第二类型的第二区域(即,n型掺杂区142)所构成。

48.在部分实施例中,栅极107设置并横跨在主动区105和主动区106上方。主动区105设置在栅极107的第一侧,而主动区106设置在栅极107的第二侧。主动区105用以接收第二电压gnd。主动区106耦接至电阻元件148,而电阻元件148耦接至输入输出垫片i/o。

49.具体而言,主动区105经由金属接点n5耦接至接地900(未绘示于图4)。主动区106经由金属接点n6耦接至连接线109。电阻元件148经由金属接点n7耦接至连接线109。电阻元件148经由金属接点n8耦接至输入输出垫片i/o。

50.如此一来,通过连接电阻元件148至主动区106和输入输出垫片i/o,电阻元件148能够实现连接至第二晶体管nmos和输入输出垫片i/o的电阻rn1。

51.如图4所示,静电保护二极管np由n型掺杂区142和p型掺杂区144所构成。在部分实

施例中,n型掺杂区142由一对侧边区域142a和多个条状区域142b所构成。p型掺杂区144由多个条状区域144b所构成。如图4所示,一对侧边区域142a是一对在x方向上延伸的条状区域。条状区域142b和条状区域144b在y方向上延伸并夹在一对侧边区域142a之间。此外,在x方向上,条状区域142b和条状区域144b以交错方式配置。

52.在部分实施例中,多个浅沟槽隔离结构146连接在条状区域142b和条状区域144b之间。换言之,条状区域144b由浅沟槽隔离结构146所围绕,且浅沟槽隔离结构146被条状区域142b和侧边区域142a(即,n型掺杂区142)所围绕。

53.以不同角度说明,如图5所示,条状区域142b、条状区域144b和浅沟槽隔离结构146设置在n型井n_well之上,n型井n_well设置在p型基板p_sub上,而电阻元件148设置在浅沟槽隔离结构146之上。换言之,条状区域142b、条状区域144b和浅沟槽隔离结构146设置在第一层,而电阻元件128设置在不同于第一层的第二层。举例来说,电阻元件148可设置在第一金属层、第二金属层及/或第三金属层。

54.此外,如图5所示,条状区域142b和条状区域144b在x方向上以交错方式设置。换言之,每个条状区域142b和每个条状区域144b在x方向上被浅沟槽隔离结构146夹在中间,而每个浅沟槽隔离结构146在x方向上被夹在条状区域142b中的一个和条状区域144b中的一个之间。

55.如此一来,电阻元件148可设置在静电保护二极管np的布局区域内。因此,如图1所示的电阻rn1~rn7不需要占用额外的布局区域。也就是说,在相同尺寸的静电保护二极管np的布局区域中,能设置静电保护二极管np和电阻元件148。

56.关于电阻元件128和148的详细说明,请参考图6a~图6d。图6a~图6d是根据本发明的部分实施例所绘示的一种电阻元件r1~r4的示意图。在部分实施例中,如图1所示的电阻ru1~ru7和rn1~rn7可由图6a~图6d中所示的电阻元件r1~r4所实现。如图6a所示,电阻元件r1由四个部件u1~u4所构成。相似地,如图6b~图6d所示,电阻元件r2、r3和r4分别由三个部件u1~u3、两个部件u1~u2和一个部件u1所构成。在部分实施例中,每个部件u1~u4可为多晶硅(polysilicon)。在其他部分实施例中,每个部件u1~u4可为金属。由于不同材质的不同导电性,因此每个电阻的阻值是能根据电阻元件的多晶硅和金属的长度比例而调整的。例如,当部件u1~u4是由导电体所连接的多晶硅结构,且电阻元件r1的阻值为4/4r时,电阻元件r2、r3和r4的阻值分别为3/4r、2/4r和1/4r。换言之,当电阻元件的多晶硅的长度越长时,电阻元件的阻值就越大。

57.值得注意的是,绘示于图中的四个部件及其长度仅为例子,并非用以限制本发明。本领域的技术人员可根据实际需求调整部件的数量、长度及其不同材料的比例。

58.需要说明的是,在不冲突的情况下,在本发明各个附图、实施例及实施例中的特征与电路可以相互组合。附图中所绘示的电路仅为示例之用,是简化以使说明简洁并便于理解,并非用以限制本发明。此外,上述各实施例中的各个装置、单元及元件可以由各种类型的数字或类比电路实现,亦可分别由不同的积体电路晶片实现,或整合至单一晶片。上述仅为例示,本发明并不以此为限。

59.综上所述,本发明通过应用上述各个实施例中,通过设置电阻元件在静电保护二极管的p型掺杂区和n型掺杂区之间,可减少晶片外驱动器电路的整体布局面积。

60.虽然本发明已以实施方式公开如上,然其并非限定本发明,任何本领域的技术人

员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰,因此本发明的保护范围当视权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1