半导体器件及制造方法与流程

1.本发明涉及半导体技术领域,尤其涉及一种半导体器件及制造方法。

背景技术:

2.目前人工智能、物联网等领域芯片依赖大数据存算,迫切需要运算更快,功耗更低,成本更低的芯片。因此,科学界提出了在存储和逻辑器件技术上的一个全新的计算框架模式,即将存储和逻辑运算集于一体的电路架构,存算一体(logic in memory or lim)。铁电场效应晶体管是最有可能实现在同一个晶体管中实现逻辑运算或存储的场效应晶体管器件。其原理在于栅极中使用铁电材料,利用极化方向调节沟道电势,根据写入时极化方向不同,将在读出时得到不同vt的两组id-vg曲线,实现0或1的状态。然而,在读出时,栅极的铁电层再次受到电压刺激,容易造成铁电极化失效、退化甚至翻转,使得存储特性逐步失效。

3.因此,有必要提供一种新型的半导体器件及制造方法以解决现有技术中存在的上述问题。

技术实现要素:

4.本发明的目的在于提供一种半导体器件及制造方法,实现半导体用作存储器件时的写入与读出分离,提高器件可靠性。

5.为实现上述目的,本发明的所述半导体器件,包括铁电层衬底、栅极、源极、漏极、浅沟槽隔离结构和侧墙,所述铁电层衬底自下而上包括第一硅层、第一氧化层、铁电层、第二氧化层和第二硅层,所述栅极、所述源极、所述漏极和所述浅沟槽隔离结构设置于所述衬底上,所述侧墙环绕所述栅极设置,且所述栅极自下而上包括层间介质层、介电层、保护层和多晶硅层,其中,所述铁电层的材料为铁电性材料,所述介电层的材料包括二氧化铪基高介电常数材料或二氧化铪基材料中的一种。

6.本发明的有益效果在于:所述介电层的材料包括铁电性材料、二氧化铪基高介电常数材料或二氧化铪基材料中的一种,可降低亚阈值摆幅,所述铁电层的材料为铁电性材料,能够利用底电极写入不同极化方向对沟道开启进行控制,读出时采用表面栅,降低对所述铁电层的影响,写入时采用底部栅,用作存储器件时的写入与读出分离,提高了器件的可靠性。

7.优选地,所述源极嵌于所述衬底内,且与所述铁电层相接触。

8.优选地,所述漏极嵌于所述衬底内,且与所述铁电层相接触。

9.优选地,所述铁电性材料为二氧化铪。

10.优选地,所述铁电性材料为钙钛矿结构材料。

11.优选地,所述浅沟槽隔离结构嵌于所述衬底内,且贯穿所述第二硅层、所述第二氧化层、所述铁电层和所述第一氧化层。

12.优选地,所述保护层的材料为氮化钛。

13.优选地,所述层间介质层的厚度为0~1nm,所述介电层的厚度为0~10nm,所述保护层的厚度为1~3nm,所述多晶硅层的厚度为10~30nm。

14.本发明还提供了一种半导体器件制造方法,包括以下步骤:

15.s1:获取铁电层衬底,然后在所述铁电层衬底上依次形成浅沟槽隔离结构以及阱区,其中,所述铁电层衬底自下而上包括第一硅层、第一氧化层、铁电层、第二氧化层和第二硅层,所述铁电层的材料为铁电性材料;

16.s2:在所述阱区上生长栅氧化层,然后在所述栅氧化层上依次沉积层间介质层、介电层、保护层、多晶硅层以及硬掩膜层,以形成栅极刻蚀结构,其中,所述介电层的材料包括二氧化铪基高介电常数材料或二氧化铪基材料中的一种;

17.s3:对所述栅极刻蚀结构进行刻蚀以及去除所述硬掩膜层,以形成栅极;

18.s4:环绕所述栅极形成侧墙,然后在所述阱区上生成源极和漏极。

19.所述半导体器件制造方法的有益效果在于:所述介电层的材料包括二氧化铪基高介电常数材料或二氧化铪基材料中的一种,可有效降低了亚阈值摆幅,所述铁电层的材料为铁电性材料,使得制造出来的半导体器件,能够利用底电极写入不同极化方向对沟道开启进行控制,读出时采用表面栅,降低对所述铁电层的影响,写入时采用底部栅,用作存储器件时的写入与读出分离,提高了器件的可靠性。

20.优选地,所述步骤s1包括以下步骤:

21.s1a:对所述第一硅层的表面进行氧化,以使所述第一硅层的表面形成所述第一氧化层,以及对所述第二硅层的表面进行氧化,以使所述第二硅层的表面形成所述第二氧化层;

22.s2a:在所述第一氧化层上沉积所述铁电层;

23.s3a:将所述铁电层和所述第二氧化层键合,然后剥离部分所述第一硅层或所述第二硅层,以得到所述铁电层衬底。

24.进一步优选地,所述步骤s1a中,还包括向所述第一硅层或所述第二硅层注入离子,以便于剥离部分所述第一硅层或所述第二硅层。

附图说明

25.图1为本发明半导体器件制造方法的流程图;

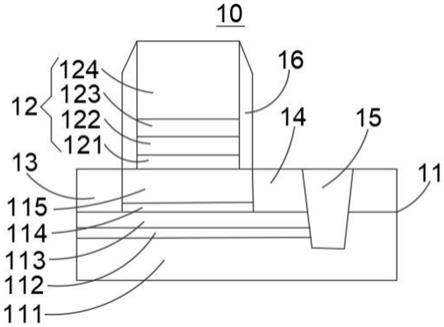

26.图2为本发明半导体器件的结构示意图。

具体实施方式

27.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。除非另外定义,此处使用的技术术语或者科学术语应当为本发明所属领域内具有一般技能的人士所理解的通常意义。本文中使用的“包括”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。

28.针对现有技术存在的问题,本发明的实施例提供了一种半导体器件制造方法,参

照图1,所述半导体器件制造方法包括以下步骤:

29.s1:获取铁电层衬底,然后在所述铁电层衬底上依次形成浅沟槽隔离结构以及阱区,其中,所述铁电层衬底自下而上包括第一硅层、第一氧化层、铁电层、第二氧化层和第二硅层,所述铁电层的材料为铁电性材料;

30.s2:在所述阱区上生长栅氧化层,然后在所述栅氧化层上依次沉积层间介质层、介电层、保护层、多晶硅层以及硬掩膜层,以形成栅极刻蚀结构,其中,所述介电层的材料包括二氧化铪基高介电常数材料或二氧化铪基材料中的一种;

31.s3:对所述栅极刻蚀结构进行刻蚀以及去除所述硬掩膜层,以形成栅极;

32.s4:环绕所述栅极形成侧墙,然后在所述阱区上生成源极和漏极。

33.一些实施例中,所述步骤s1包括以下步骤:

34.s1a:对所述第一硅层的表面进行氧化,以使所述第一硅层的表面形成所述第一氧化层,以及对所述第二硅层的表面进行氧化,以使所述第二硅层的表面形成所述第二氧化层;

35.s2a:在所述第一氧化层上沉积所述铁电层;

36.s3a:将所述铁电层和所述第二氧化层键合,然后剥离部分所述第一硅层或所述第二硅层,以得到所述铁电层衬底。

37.一些实施例中,所述步骤s1a中,还包括向所述第一硅层或所述第二硅层注入离子,以便于剥离部分所述第一硅层或所述第二硅层。具体地,所述离子为氢离子。

38.一些实施例中,所述步骤s1中,对所述第二硅层背向所述铁电层的一面进行热氧化,形成一层厚度为20nm的二氧化硅;采用化学气相沉积的方式在所述二氧化硅上形成一层厚度为250nm的氮化硅;在所述氮化硅上形一层厚度为0.5~1μm的光刻胶;对所述氮化硅、二氧化硅和第二硅层进行刻蚀,以形成浅沟槽;去除光刻胶,然后通过化学气相沉积的方式沉积0.5~1μm的二氧化硅,并通过化学机械研磨的方式去除多余的二氧化硅,直至到达氮化硅;在180℃的温度下通过热磷酸湿法刻蚀去除氮化硅,以形成所述浅沟槽隔离结构。

39.一些实施例中,所述步骤s1中,采用光刻胶交替隔离的方法,向部分所述第二硅层内注入高能磷离子,以形成n型区域,向部分所述第二硅层内注入高能硼离子,以形成p型区域,然后进行退火,以使所述n型区域形成n阱区,所述p型区域形成p阱区。

40.一些实施例中,所述步骤s2中,还包括在所述n阱区和所述p阱区上生长厚度为25nm的牺牲氧化层,用于捕获所述n阱区和所述p阱区表面硅的缺陷;通过氢氟酸溶液湿法刻蚀去除所述牺牲氧化层,以剩余洁净的硅表面。

41.一些实施例中,所述步骤s2中,所述栅氧化层的厚度为2~10nm,用作半导体的栅绝缘层。

42.一些实施例中,所述步骤s2和s3中,通过化学气相沉积的方式在所述栅氧化层上依次沉积层间介质层、介电层、多晶硅层以及硬掩膜层,然后对层间介质层、介电层和多晶硅层进行刻蚀,去除所述硬掩膜层后形成栅极。

43.一些实施例中,所述步骤s4中,采用光刻胶交替隔离的方式,向所述p阱区注入低能量、浅深度和低掺杂的砷离子,向所述n阱区注入低能量、浅深度和低掺杂的bf2+离子;然后通过化学气相沉积的方式沉积一层厚度为120~180nm的氮化硅;在180℃的温度下通过

热磷酸湿法刻蚀去多余的氮化硅,留下环绕所述栅极的氮化硅作为侧墙;采用光刻胶交替隔离的方式,向所述p阱区注入浅深度和重掺杂的砷离子,以形成重掺杂的源区和漏区,即源极和漏极,向所述n阱区注入浅深度和重掺杂的bf2+离子,以形成重掺杂的源区和漏区,即源极和漏极。

44.一些实施例中,所述步骤s4中,还包括在所述多晶硅层生长氧化层,用于缓冲隔离多晶硅和后续工艺中的氮化硅。

45.一些实施例中,所述步骤s1中,还包括刻蚀所述浅沟槽隔离结构背向所述栅极一侧的所述第二硅层、所述第二氧化层、所述铁电层以及所述第一氧化层,然后在所述第一硅层的上侧沉积硅,注入离子以形成连接所述第一硅层的电极。

46.一些实施例中,所述半导体器件制造方法还包括在氢氟酸内浸泡,以去除栅极、源极和漏极表面的氧化物,以暴露出源极、源极和漏极表面的硅;通过化学气相沉积的方式沉积一层厚度为20~40nm的钛,采用快速加热工艺,在800℃和氮气气氛的条件下,使得钛与硅接触的区域形成钛化硅,而其他区域的钛无变化;通过湿法刻蚀,采用氢氧化铵和过氧化氢刻蚀去掉剩余的钛,而保留钛化硅,以形成硅与金属之间的欧姆接触;通过化学气相沉积一层厚度为1μm的硼磷硅玻璃,并通过化学机械研磨在硼磷硅玻璃上形成一个光滑的表面;采用光刻胶定义接触孔,对硼磷硅玻璃进行刻蚀,以获得孔状结构;通过溅射工艺在硼磷硅玻璃的外漏面上沉积一层厚度为20nm的氮化钛;通过化学气相沉积的方式沉积钨,以填充满所述孔状结构和硼磷硅玻璃的表面,其中,所述孔状结构内钨的厚度大于或等于所述孔状结构的半径;通过化学机械研磨去除表面的钨和氮化钛,其中,钨填充满所述孔状结构;通过溅射工艺,沉积第一层金属,并采用光刻胶遮挡的方式对所述第一层金属进行刻蚀,以形成多个第一层金属;采用与所述第一层金属相同的工艺生成第二层金属、第三层金属直至第n层金属,n为大于1的自然数。

47.图2为本发明一些实施例中半导体器件的结构示意图。所述半导体器件10包括铁电层衬底11、栅极12、源极13、漏极14、浅沟槽隔离结构15和侧墙16,所述铁电层衬底11自下而上包括第一硅层111、第一氧化层112、铁电层113、第二氧化层114和第二硅层115,所述栅极12、所述源极13、所述漏极14和所述浅沟槽隔离结构15设置于所述衬底11上,所述侧墙16环绕所述栅极12设置,且所述栅极12自下而上包括层间介质层121、介电层122、保护层123和多晶硅层124,其中,所述铁电层113的材料为铁电性材料,所述介电层122的材料包括二氧化铪基高介电常数材料或二氧化铪基材料中的一种。

48.一些实施例中,参照图2,所述源极13嵌于所述衬底11内,且与所述铁电层113相接触;所述漏极14嵌于所述衬底11内,且与所述铁电层113相接触;所述浅沟槽隔离结构15嵌于所述衬底11内,且贯穿所述第二硅层115、所述第二氧化层114、所述铁电层113和所述第一氧化层112。

49.一些实施例中,参照图2,所述浅沟槽隔离结构15的右侧去除所述第二硅层115、所述第二氧化层114、所述铁电层113和第一氧化层112,并在所述第一硅层111的上侧形成连接所述第一硅层111的电极。

50.一些实施例中,所述铁电性材料为二氧化铪。又一些实施例中,所述铁电性材料为钙钛矿结构材料。

51.一些实施例中,所述保护层的材料为氮化钛,所述层间介质层的厚度为0~1nm,所

述介电层的厚度为0~10nm,所述保护层的厚度为1~3nm,所述多晶硅层的厚度为10~30nm。具体地,所述层间介质层的厚度为1nm,所述介电层的厚度为10nm,所述保护层的厚度为3nm,所述多晶硅层的厚度为30nm。

52.一些实施例中,所述半导体器件中,所述源端和所述漏端接正偏压,所述铁电层衬底接地,则所述铁电层写入向下的极化,以写入1;基于所述铁电层为写入向下的极化状态,读出时,沟道的空穴被吸引到下表面,电子更容易聚集在栅极下侧,因此id-vg曲线的阈值电压vt较小,出现低vt,以读出1;所述源端和所述漏端接负偏压,所述铁电层衬底接地,则所述铁电层写入向上的极化,以写入0;基于所述铁电层为写入向上的极化状态,读出时,沟道里的电子被吸引到下表面,电子不容易聚集在栅极下侧,因此id-vg出现高vt,以读出0。

53.又一些实施例中,所述半导体器件中,所述源端和所述漏端接地,所述铁电层或所述栅极接负偏压,则所述铁电层写入向下的极化,以写入1;基于所述铁电层为写入向下的极化状态,读出时,沟道的空穴被吸引到下表面,电子更容易聚集在栅极下侧,因此id-vg曲线的阈值电压vt较小,出现低vt,以读出1;所述源端和所述漏端接地,所述铁电层或所述栅极接正偏压,则所述铁电层写入向上的极化,以写入0;基于所述铁电层为写入向上的极化状态,读出时,沟道里的电子被吸引到下表面,电子不容易聚集在栅极下侧,因此id-vg出现高vt,以读出0。

54.虽然在上文中详细说明了本发明的实施方式,但是对于本领域的技术人员来说显而易见的是,能够对这些实施方式进行各种修改和变化。但是,应理解,这种修改和变化都属于权利要求书中所述的本发明的范围和精神之内。而且,在此说明的本发明可有其它的实施方式,并且可通过多种方式实施或实现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1