静电保护电路及半导体装置的制作方法

1.本发明涉及半导体装置的静电保护电路。

背景技术:

2.现有的半导体装置的静电保护电路,由发射极端子与信号端子连接且集电极端子与gnd端子连接的pnp晶体管构成。在具备这样构成的静电保护电路的半导体装置中,即便信号端子下降到gnd端子的电位以下,也不会引起动作上的问题(例如,参照专利文献1)。

3.【现有技术文献】【专利文献】【专利文献1】日本特开2000-223499号公报。

技术实现要素:

4.【发明要解决的课题】如图6所示,静电保护电路60的静电保护用的pnp晶体管(以实线示出),在用cmos工艺制造的情况下,一般由n阱(nwell)构成基极。这样构成的pnp晶体管可以视为:p型区域61为正极且nwell为负极的二极管d1和p型区域62为正极且nwell为负极的二极管d2的串联连接。另外,二极管d1的正极、nwell、p衬底(psub)可以视为寄生pnp晶体管(以虚线示出)的发射极、基极、集电极。

5.然而,当成为高温时二极管d2的泄漏电流会经由二极管d1而流过。寄生pnp晶体管使得按其电流放大率对泄漏电流放大后的集电极电流流动。因而,现有的静电保护电路中,在成为高温时寄生pnp晶体管的集电极电流从信号端子流入gnd端子,所以会增大信号端子的输入电流。

6.本发明的目的在于提供在高温下信号端子的输入电流的增加量较少的静电保护电路及半导体装置。

7.【用于解决课题的方案】本发明的实施方式所涉及的静电保护电路,其特征在于具备:第1二极管,其正极与信号端子连接;第2二极管,其负极与第1二极管的负极连接且正极与gnd端子连接;以及耗尽型的mos晶体管,其与第1二极管并联连接。

8.另外,本发明的实施方式所涉及的半导体装置,其特征在于:在信号端子与内部电路之间具备上述静电保护电路。

9.【发明效果】依据本发明的静电保护电路,与第1二极管并联地设置了耗尽型的mos晶体管,所以能够提供在高温下信号端子的输入电流的增加量较少的静电保护电路及半导体装置。

附图说明

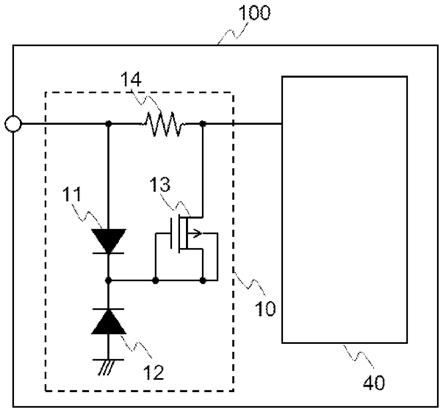

10.图1是示出具备第1实施方式所涉及的静电保护电路的半导体装置的电路图。

11.图2是示出第1实施方式所涉及的静电保护电路的其他例子的电路图。

12.图3是示出具备第2实施方式所涉及的静电保护电路的半导体装置的电路图。

13.图4是示出第2实施方式所涉及的静电保护电路的其他例子的电路图。

14.图5是示出第1实施方式所涉及的静电保护电路的其他例子的电路图。

15.图6是现有的具备静电保护电路的半导体装置的截面图。

具体实施方式

16.以下,参照附图,对本发明的实施方式进行说明。本发明的实施方式所涉及的半导体装置具有:对信号进行输入输出的信号端子;与信号端子连接的内部电路;以及设置在信号端子与内部电路之间的静电保护电路。关于半导体装置的内部电路,将省略其详细的说明。

17.<第1实施方式>图1是示出具备第1实施方式所涉及的静电保护电路的半导体装置的电路图。

18.半导体装置100具备静电保护电路10和内部电路40。静电保护电路10具备二极管11、12、耗尽型的p沟道型mos晶体管(以下pmos晶体管)13和电阻14。电阻14是内部电路40的晶体管的栅极保护电阻。

19.二极管11中,正极与信号端子连接,负极与二极管12的负极连接。二极管12的正极与gnd端子连接。pmos晶体管13中,漏极与内部电路40连接,栅极、源极和本体(bulk)连接到二极管11的负极。电阻14连接在二极管11的正极与pmos晶体管13的漏极之间。

20.接着,对第1实施方式的静电保护电路10的动作进行说明。此外,在静电保护电路10中,由二极管11的正极和负极及psub构成寄生pnp晶体管这一点与现有技术是同样的。

21.<信号端子的电压高于gnd端子的电压的稳定状态>pmos晶体管13中,栅极与源极连接,但因为是耗尽型,所以在漏极-源极间存在沟道。由于pmos晶体管13的电流供给能力充分大于流过二极管12的泄漏电流,所以pmos晶体管13的导通电阻导致的电压降会接近于0v。因此,二极管12的大部分泄漏电流流过pmos晶体管13,而在二极管11中没有电流流过。因而,在寄生pnp晶体管中不会有电流流过,所以能够将流过信号端子的电流抑制得较小。

22.<信号端子的电压低于gnd端子的电压的反向连接状态>pmos晶体管13作为过驱动电压为|vtpd|(阈值电压)的恒流源进行动作。反向电流从gnd端子经由二极管12和pmos晶体管13流入信号端子,但可以通过pmos晶体管13抑制为能够允许的电流。因而,即便与二极管11并联地连接有pmos晶体管13,反向连接状态下半导体装置的动作上也不会产生问题。

23.如以上说明的那样,本实施方式所涉及的静电保护电路10与二极管11并联地具备pmos晶体管13,从而在高温下不会有电流流过寄生晶体管,因此能够减少信号端子的输入电流的增加量。

24.此外,即便将pmos晶体管13置换成图2所示那样连接的耗尽型的n沟道型mos晶体管23,也能获得同样的效果。

25.<第2实施方式>图3是示出具备第2实施方式所涉及的静电保护电路的半导体装置的电路图。

26.相对于图1的静电保护电路10,图3的静电保护电路20还具备电阻15。此外,对于与图1所示的静电保护电路10相同的结构要素标注相同的标号,并适当省略重复的说明。

27.<信号端子的电压高于gnd端子的电压的稳定状态>在pmos晶体管13的源极与二极管12的负极之间连接有电阻15。电阻15的电阻值充分小,因此可以进行与图1的静电保护电路10同样的动作。

28.<信号端子的电压低于gnd端子的电压的反向连接状态>在反向连接状态下,流过pmos晶体管13的电流大体由|vtpd|/r决定。在此,r为电阻15的电阻值。即,将该电流设定为作为反向电流能够允许的电流值即可。因而,与第1实施方式的静电保护电路10相比,能够减小pmos晶体管13的尺寸。

29.如以上说明的那样,本实施方式的静电保护电路20通过与二极管11并联地具备pmos晶体管13和电阻15,在高温下不会有电流流过寄生晶体管,因此能够减少信号端子的输入电流的增加量。

30.此外,即便将pmos晶体管13和电阻15置换成图4所示那样连接的耗尽型的n沟道型mos晶体管23和电阻25,也能获得同样的效果。

31.以上,对本发明的实施方式进行了说明,但是本发明并不局限于上述实施方式,在不脱离本发明的宗旨的范围内可进行各种变更。

32.例如,二极管11和二极管12也可以置换成mos晶体管的静电保护元件。作为一个例子,在图5中示出将图1的静电保护电路10的二极管置换成增强型的n沟道mos晶体管31、32的静电保护电路30。

33.另外,例如电阻14也可以在pmos晶体管13的漏极(nmos晶体管23的源极)与内部电路40之间连接。在此情况下,为了进行保护,也可以与pmos晶体管13的漏极(nmos晶体管23的源极)和本体的路径串联地设置电阻,例如在pmos晶体管13的栅极和源极和本体的连接点与二极管11的负极之间设置电阻。

34.标号说明10、20、30 静电保护电路;11、12 二极管;13 耗尽型的p沟道型mos晶体管;23 耗尽型的n沟道型mos晶体管;31、32 增强型的n沟道型mos晶体管;40 内部电路;100 半导体装置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1