一种二极管封装框架的制作方法

[0001]

本实用新型涉及一种二极管封装框架,属于电子元件封装技术领域。

背景技术:

[0002]

随着科学技术的发展和电子线路的设计需求,在各种设备、仪器的电子线路中都要使用esd来进行保护,避免设备、仪器受到静电损伤;

[0003]

以往的硅esd保护二极管为单通道设计,不能满足电路小型化、集成化的发展方向,需要开发多通道的硅esd保护二极管,多通道的硅esd保护二极管如图2所示,如果采用以往的单通道硅esd保护二极管封装框架对现有的多通道的硅esd保护二极管进行封装,存在的问题为:以前的封装框架只有一个放置芯片的搭载段,当将所有芯片放置在一个搭载段上,由于放置芯片的搭载段是一个金属导电整体,放置芯片完成后芯片背部全部导通,每个芯片之间都会相互影响,不能达到产品设计时的功能要求。

技术实现要素:

[0004]

为解决上述技术问题,本实用新型提供了一种二极管封装框架。

[0005]

本实用新型通过以下技术方案得以实现。

[0006]

本实用新型提供的一种二极管封装框架,包括:底板,底板上设有多个封装单元,封装单元包括芯片搭载段、引脚段,八个芯片搭载段以均匀间隔的四个为一组,两组对向设置;引脚段两端分别与芯片搭载段和底板凹槽内侧面固定连接。

[0007]

所述芯片搭载段侧面与底板凹槽内侧面有间距。

[0008]

所述芯片搭载段与引脚段为一体,提高导电性能。

[0009]

所述引脚段连接芯片搭载段的中部。

[0010]

所述引脚段宽度小于芯片搭载段的宽度。

[0011]

所述两引脚段之间经连接段固定连接,提高引脚段的强度。

[0012]

所述两引脚段与连接段固定为一体。

[0013]

所述封装单元与底板纵向之间设有通槽a。

[0014]

所述封装单元彼此纵向之间设有通槽b。

[0015]

所述封装单元彼此横向之间设有通槽c。

[0016]

本实用新型的有益效果在于:对八个引脚段与连接段连接处将一个封装单元精剪下,由于八个芯片搭载段不是一个整体而是彼此间隔的,形成四条独立的线路,保护四条独立线路不受静电破坏的危险,解决了金属导电整体会将八个芯片的背部全部导通,导致在封装后的产品性能不能达到产品设计时的功能要求的问题,使得生产的产品能满足合格要求。

附图说明

[0017]

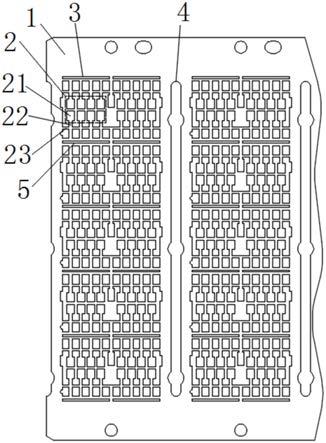

图1是本实用新型的结构示意图;

[0018]

图2是硅esd保护二极管封装图;

[0019]

图中:1-底板;2-封装单元;21-芯片搭载段;22-引脚段;23-连接段;3-通槽a;4-通槽b;5-通槽c。

具体实施方式

[0020]

下面进一步描述本实用新型的技术方案,但要求保护的范围并不局限于所述。

[0021]

参见图1至图2所示。

[0022]

本实用新型的一种二极管封装框架,包括:底板1,底板1上设有多个封装单元2,封装单元2包括芯片搭载段21、引脚段22,八个芯片搭载段21以均匀间隔的四个为一组,两组对向设置;引脚段22两端分别与芯片搭载段21和底板1凹槽内侧面固定连接。

[0023]

所述芯片搭载段21侧面与底板1凹槽内侧面有间距。

[0024]

所述芯片搭载段21与引脚段22为一体,提高导电性能。

[0025]

所述引脚段22连接芯片搭载段21的中部。

[0026]

所述引脚段22宽度小于芯片搭载段21的宽度。

[0027]

所述两引脚段22之间经连接段23固定连接,提高引脚段22的强度。

[0028]

所述两引脚段22与连接段23固定为一体。

[0029]

所述封装单元2与底板1纵向之间设有通槽a3。

[0030]

所述封装单元2彼此纵向之间设有通槽b4。

[0031]

所述封装单元2彼此横向之间设有通槽c5。

[0032]

工作原理:以八个p、n结芯片为一单元,八个p、n结芯片分别放置在一个封装单元2的八个芯片搭载段21上,使用引线对p、n结进行导电焊接,而后进行塑装,塑装后以通槽a3、通槽b4、通槽c5以及芯片搭载段21侧面与底板1凹槽内侧面有间距将一个封装单元2初剪下,再从八个引脚段22与连接段23连接处将一个封装单元2精剪下,由于八个芯片搭载段21不是一个整体而是彼此间隔的,形成四条独立的线路,保护四条独立线路不受静电破坏的危险,解决了金属导电整体会将八个芯片的背部全部导通,导致在封装后的产品性能不能达到产品设计时的功能要求的问题,使得生产的产品能满足合格要求。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1