一种多芯片堆叠的三维扇出型封装结构的制作方法

[0001]

本实用新型涉及一种多芯片堆叠的三维扇出型封装结构,属于芯片封装技术领域。

背景技术:

[0002]

扇出型的英文全称为(fan-out packaging;fop),中文全称为(扇出型封装),其采取将芯片内引脚拉线出来的方式,让多种不同裸晶埋进去,通过高密度再布线相连,提高互联密度,并缩短了芯片之间距离,降低了封装厚度并节省空间,提高了互联性能。然而对于多颗芯片密集封装,扇出后的面积过大,封装密度不足,无法应用于超高密度多芯片模组。

技术实现要素:

[0003]

承上所述,本实用新型的目的在于克服现有芯片封装结构的不足,提供一种多芯片堆叠的三维扇出型封装结构,以解决现有的三维扇出型封装结构无法应用于超高密度多芯片模组的问题。

[0004]

本实用新型的目的是这样实现的:

[0005]

本实用新型提供了一种多芯片堆叠的三维扇出型封装结构,其由下而上依次包括第一封装体、再布线金属层ⅱ和第二封装体,所述第二封装体堆叠设置在第一封装体的上方,并通过再布线金属层ⅱ实现电信连接,

[0006]

所述第一封装体包括再布线金属层ⅰ、芯片ⅰ封装体、若干个金属互联柱、塑封料ⅰ,所述再布线金属层ⅰ的上表面设置上层焊盘ⅰ和上层焊盘ⅱ、其下表面设置底层焊盘;

[0007]

所述芯片ⅰ封装体包括芯片ⅰ、金属引脚、芯片绝缘层和芯片塑封料,所述芯片绝缘层覆盖芯片ⅰ的正面,并设有芯片绝缘层开口露出芯片ⅰ的芯片电极,所述金属引脚通过芯片绝缘层开口与芯片电极连接,所述芯片塑封料塑封金属引脚,所述芯片ⅰ通过金属引脚倒装在再布线金属层ⅰ的上表面并与再布线金属层ⅰ的上层焊盘ⅱ连接,

[0008]

所述金属互联柱设置在芯片ⅰ封装体的周围并与再布线金属层ⅰ的上层焊盘ⅰ连接,所述塑封料ⅰ于再布线金属层ⅰ上方包封芯片ⅰ封装体和金属互联柱,其上表面与金属互联柱的顶端、芯片ⅰ封装体的顶端齐平;

[0009]

所述再布线金属层ⅱ的上表面设置上层复合金属焊盘,所述上层复合金属焊盘上设置金属合金层;

[0010]

所述第二封装体包括若干个芯片ⅱ、芯片下凸块金属、焊球、底填胶和塑封料ⅱ,所述芯片下凸块金属设置于芯片ⅱ的正面,所述芯片ⅱ依次通过芯片下凸块金属、焊球、金属合金层与再布线金属层ⅱ的上层复合金属焊盘倒装连接;

[0011]

所述底填胶填充芯片ⅱ底部及其芯片间隙,所述塑封料ⅱ于再布线金属层ⅱ上方塑封芯片ⅱ,并露出芯片ⅱ的背面;

[0012]

所述芯片ⅰ依次通过金属引脚、再布线金属层ⅰ、金属互联柱、再布线金属层ⅱ与芯片ⅱ连接,和/或所述芯片ⅰ依次通过金属引脚、再布线金属层ⅰ将电信号向下传导。

[0013]

进一步地,所述塑封料ⅰ于再布线金属层ⅰ上方留出再布线金属层ⅰ的上方边缘不包封,所述第二封装体的塑封料ⅱ向下塑封再布线金属层ⅱ至第一封装体的再布线金属层ⅰ的上方边缘。

[0014]

进一步地,所述第一封装体的塑封料ⅰ还塑封被动元件ⅰ,所述被动元件ⅰ设置于再布线金属层ⅰ的上表面。

[0015]

进一步地,所述第二封装体的塑封料ⅱ还塑封被动元件ⅱ,所述被动元件ⅱ设置于再布线金属层ⅱ的上表面。

[0016]

进一步地,所述上层复合金属焊盘包括铜层和镍层,所述镍层覆盖铜层之上。

[0017]

进一步地,所述金属合金层包括金层和焊锡层,所述焊锡层覆盖金层。

[0018]

进一步地,还包括金属微凸块和球栅阵列焊球,所述金属微凸块设置于再布线金属层ⅰ的下方与其底层焊盘连接,所述球栅阵列焊球通过金属微凸块与再布线金属层ⅰ连接。

[0019]

有益效果

[0020]

1、本实用新型多芯片堆叠的扇出型封装结构,兼顾扇出型封装布线密度大,互联间距小的优点,并通过三维堆叠的方式有效利用了垂直方向的空间;

[0021]

2、基于本实用新型提供的该种封装结构获得的最终单颗产品,除了露出的金属锡球凸点外及功能芯片背面硅外,将全部由塑封胶包裹,形成良好的机械强度;使用再布线作为同层芯片之间互联电路,形成平面方向的扇出型结构;利用垂直方向的互联金属柱ⅱ将上层的第一封装体的再布线金属层ⅰ与下层第二封装体内的再布线金属层ⅱ互联,进而形成下层芯片ⅰ与上层芯片ⅱ之间的三维互联;最终实现功能芯片间的三维扇出型互联,用更小尺寸形成高密度互联,相比传统的扇出型封装结构或三维堆叠工艺,该方案集成度更高且更有利于实现。

附图说明

[0022]

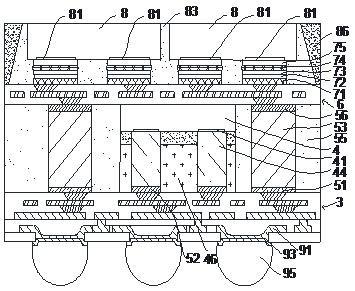

图1为本实用新型一种多芯片堆叠的三维扇出型封装结构的实施例一的剖面示意图;

[0023]

图2至图4为图1中第一封装体内的芯片ⅰ与被动元件ⅰ的分布示意图;

[0024]

图5为本实用新型一种多芯片堆叠的三维扇出型封装结构的实施例二的剖面示意图;

[0025]

主要元件符号说明

[0026]

再布线金属层ⅰ3

[0027]

芯片ⅰ4

[0028]

金属引脚44

[0029]

芯片绝缘层46

[0030]

芯片塑封料48

[0031]

上层焊盘ⅰ51

[0032]

上层焊盘ⅱ52

[0033]

金属互联柱53

[0034]

塑封料ⅰ55

[0035]

再布线金属层ⅱ6

[0036]

铜层71

[0037]

镍层72

[0038]

金属合金层73

[0039]

焊球74

[0040]

芯片下凸块金属75

[0041]

芯片ⅱ8

[0042]

底填胶83

[0043]

塑封料ⅱ86

[0044]

底层焊盘91

[0045]

金属微凸块93

[0046]

球栅阵列焊球95。

具体实施方式

[0047]

现在将在下文中参照附图更加充分地描述本实用新型,在附图中示出了本实用新型的示例性实施例,从而本公开将本实用新型的范围充分地传达给本领域的技术人员。然而,本实用新型可以以许多不同的形式实现,并且不应被解释为限制于这里阐述的实施例。

[0048]

下面结合附图和实施例对本实用新型进行进一步地说明。

[0049]

实施例一

[0050]

本实用新型一种多芯片堆叠的三维扇出型封装结构,其由下而上依次包括第一封装体、再布线金属层ⅱ6和第二封装体,所述第二封装体堆叠设置在第一封装体的上方,并通过再布线金属层ⅱ6连接电信连接,如图1至4所示。

[0051]

所述第一封装体包括再布线金属层ⅰ3、芯片ⅰ封装体、若干个金属互联柱53、塑封料ⅰ55,再布线金属层ⅰ3的上表面设有金属互联柱53的上层焊盘ⅰ51和芯片ⅰ封装体的上层焊盘ⅱ52,其下表面设有底层焊盘91。

[0052]

所述芯片ⅰ封装体包括芯片ⅰ4、金属引脚44、芯片绝缘层46和芯片塑封料48,所述芯片ⅰ4倒装在再布线金属层ⅰ3的上表面,具体地,所述芯片绝缘层46覆盖芯片ⅰ4的正面,并设有芯片绝缘层开口露出芯片ⅰ4的芯片电极41,所述金属引脚44通过芯片绝缘层开口与芯片ⅰ4的芯片电极41连接,所述芯片塑封料48塑封金属引脚44。芯片ⅰ4的金属引脚44外露出第一封装体。芯片ⅰ4通过金属引脚44倒装在再布线金属层ⅰ3的上表面并与再布线金属层ⅰ3的上层焊盘ⅱ52连接。

[0053]

所述金属互联柱53设置在芯片ⅰ封装体的周围并与再布线金属层ⅰ3的上层焊盘ⅰ51连接,所述塑封料ⅰ55于再布线金属层ⅰ3上方包封芯片ⅰ封装体和金属互联柱53,其上表面与金属互联柱53的顶端、芯片ⅰ封装体的顶端齐平;

[0054]

所述再布线金属层ⅱ6的上表面设置上层复合金属焊盘,所述上层复合金属焊盘包括铜层71和镍层72,所述镍层72覆盖铜层71之上。所述再布线金属层ⅱ6的下表面设置连接金属互联柱53的下层焊盘 56。所述再布线金属层ⅱ6包括多层金属层以及绝缘层。

[0055]

所述上层复合金属焊盘上设置金属合金层73,金属合金层73包括金层72和焊锡层73,所述焊锡层73覆盖金层72;

[0056]

所述第二封装体包括若干个芯片ⅱ8、芯片下凸块金属75、焊球74、底填胶83和塑封料ⅱ86,芯片ⅱ8为功能芯片。所述芯片下凸块金属75设置于芯片ⅱ8的正面与芯片ⅱ电极81连接,所述芯片ⅱ8依次通过芯片下凸块金属75、焊球74、金属合金层与再布线金属层ⅱ6的上层复合金属焊盘70倒装连接;

[0057]

所述底填胶83填充芯片ⅱ8底部及其芯片间隙,所述塑封料ⅱ86于再布线金属层ⅱ6上方塑封芯片ⅱ8,并露出芯片ⅱ8的背面;

[0058]

所述芯片ⅰ4依次通过金属引脚44、再布线金属层ⅰ3、金属互联柱53、再布线金属层ⅱ6与芯片ⅱ8连接,和/或所述芯片ⅰ4依次通过金属引脚44、再布线金属层ⅰ3将电信号向下传导,使得芯片ⅰ4的每一个金属引脚44通过再布线金属层ⅰ3跟至少一个金属互联柱53相连接或与至少一个芯片ⅱ8相连接。再布线金属层ⅰ3的下方还可以设置金属微凸块93和球栅阵列焊球95,所述金属微凸块93设置于再布线金属层ⅰ3的下方与其底层焊盘91连接,所述球栅阵列焊球95通过金属微凸块93与再布线金属层ⅰ3连接。

[0059]

本实用新型一种多芯片堆叠的三维扇出型封装结构的上述实施例,通过堆叠在第一封装体上方的第二封装体的再布线金属层ⅱ6,第二封装体内包裹的芯片ⅱ8与位于第二封装体内的再布线路的焊盘互联,进而与第一封装体内芯片ⅰ4以及再布线金属层ⅰ3形成三维互联。

[0060]

本实用新型一种多芯片堆叠的三维扇出型封装结构,其第一封装体的塑封料ⅰ55还塑封电阻、电感等被动元件ⅰ41,所述被动元件ⅰ41设置于再布线金属层ⅰ3的上表面。如图2至4所示。可选地,其第二封装体的塑封料ⅱ86还塑封电阻、电感等被动元件ⅱ,所述被动元件ⅱ设置于再布线金属层ⅱ6的上表面。

[0061]

实施例二

[0062]

本实用新型一种多芯片堆叠的三维扇出型封装结构,其由下而上依次包括第一封装体、再布线金属层ⅱ6和第二封装体,所述第二封装体堆叠设置在第一封装体的上方,并通过再布线金属层ⅱ6连接电信连接,如图5所示。

[0063]

所述第一封装体包括再布线金属层ⅰ3、芯片ⅰ封装体、若干个金属互联柱53、塑封料ⅰ55,再布线金属层ⅰ3的上表面设有金属互联柱53的上层焊盘51和芯片ⅰ封装体的上层焊盘ⅱ52,其下表面设有底层焊盘91。

[0064]

所述芯片ⅰ封装体包括芯片ⅰ4、金属引脚44、芯片绝缘层46和芯片塑封料48,所述芯片ⅰ4倒装在再布线金属层ⅰ3的上表面,具体地,所述芯片绝缘层46覆盖芯片ⅰ4的正面,并设有芯片绝缘层开口露出芯片ⅰ4的芯片电极41,所述金属引脚44通过芯片绝缘层开口与芯片ⅰ4的芯片电极41连接,所述芯片塑封料48塑封金属引脚44。芯片ⅰ4的金属引脚44外露出第一封装体。芯片ⅰ4通过金属引脚44倒装在再布线金属层ⅰ3的上表面并与再布线金属层ⅰ3的上层焊盘ⅱ52连接。

[0065]

所述金属互联柱53设置在芯片ⅰ封装体的周围并与再布线金属层ⅰ3的上层焊盘ⅰ51连接,所述塑封料ⅰ55于再布线金属层ⅰ3上方包封芯片ⅰ封装体和金属互联柱53,并留出再布线金属层ⅰ3的上方边缘不包封,其上表面与金属互联柱53的顶端、芯片ⅰ封装体的顶端齐平;

[0066]

所述再布线金属层ⅱ6的上表面设置上层复合金属焊盘,所述上层复合金属焊盘包括铜层71和镍层72,所述镍层72覆盖铜层71之上。所述再布线金属层ⅱ6的下表面设置连

接金属互联柱53的下层焊盘 56。所述再布线金属层ⅱ6包括多层金属层以及绝缘层。

[0067]

所述上层复合金属焊盘上设置金属合金层73,金属合金层73包括金层和焊锡层,所述焊锡层覆盖金层;

[0068]

所述第二封装体包括若干个芯片ⅱ8、芯片下凸块金属75、焊球74、底填胶83和塑封料ⅱ86,芯片ⅱ8为功能芯片。所述芯片下凸块金属75设置于芯片ⅱ8的正面,所述芯片ⅱ8依次通过芯片下凸块金属75、焊球74、金属合金层与再布线金属层ⅱ6的上层复合金属焊盘倒装连接;

[0069]

所述底填胶83填充芯片ⅱ8底部及其芯片间隙,所述塑封料ⅱ86于再布线金属层ⅱ6上方塑封芯片ⅱ8,并露出芯片ⅱ8的背面;且塑封料ⅱ86向下塑封再布线金属层ⅱ6至第一封装体的再布线金属层ⅰ3的上方边缘,通过塑封料ⅱ86的包裹,形成了良好的机械强度。

[0070]

所述芯片ⅰ4依次通过金属引脚44、再布线金属层ⅰ3、金属互联柱53、再布线金属层ⅱ6与芯片ⅱ8连接,和/或所述芯片ⅰ4依次通过金属引脚44、再布线金属层ⅰ3将电信号向下传导,使得芯片ⅰ4的每一个金属引脚44通过再布线金属层ⅰ3跟至少一个金属互联柱53相连接或与至少一个芯片ⅱ8相连接。再布线金属层ⅰ3的下方还可以设置金属微凸块93和球栅阵列焊球95,所述金属微凸块93设置于再布线金属层ⅰ3的下方与其底层焊盘91连接,所述球栅阵列焊球95通过金属微凸块93与再布线金属层ⅰ3连接。

[0071]

本实用新型一种多芯片堆叠的三维扇出型封装结构的上述实施例,通过堆叠在第一封装体上方的第二封装体的再布线金属层ⅱ6,第二封装体内包裹的芯片ⅱ8与位于第二封装体内的再布线路的焊盘互联,进而与第一封装体内芯片ⅰ4以及再布线金属层ⅰ3形成三维互联。

[0072]

本实用新型一种多芯片堆叠的三维扇出型封装结构,其第一封装体的塑封料ⅰ55还塑封电阻、电感等被动元件ⅰ47,所述被动元件ⅰ47设置于再布线金属层ⅰ3的上表面。如图2至4所示。可选地,其第二封装体的塑封料ⅱ86还塑封电阻、电感等被动元件ⅱ,所述被动元件ⅱ设置于再布线金属层ⅱ6的上表面。

[0073]

以上所述的具体实施方式,对本实用新型的目的、技术方案和有益效果进行了进一步地详细说明,所应理解的是,以上所述仅为本实用新型的具体实施方式而已,并不用于限定本实用新型的保护范围,在本实用新型的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1