碳化硅单晶,半导体元件的制作方法

1.该公开涉及碳化硅单晶及使用该碳化硅单晶的半导体元件。

背景技术:

2.属于氮化物半导体的gan、aln、inn等或者作为它们的混晶的材料具有宽带隙,被用作大功率电子器件或者短波发光器件等。其中,作为大功率电子器件,开发了关于场效应型晶体管(fet:field-effect transistor),特别是关于高电子迁移率晶体管(hemt:high electron mobility transistor)的技术。使用氮化物半导体的hemt能够用于高输出

·

高效率放大器,大功率开关器件等,其工作频率可覆盖微波和毫米波区域。专利文献1中公开了用于移动电话的基站放大器的大功率电子器件的一个例子。

3.利用大多数的技术进行生长的碳化硅单晶通常导电性过高而不能用作氮化物半导体hemt的基板。特别是,这样的碳化硅单晶的高导电性有时妨碍晶体管的高速工作,因此要求电阻率高的碳化硅单晶。

4.为了实现在碳化硅单晶的基板上制成的器件中稳定的高速工作和高频工作,作为寄生电容的对策,需要具有至少1

×

105ω

·

cm的电阻率的碳化硅单晶。另外,为了使器件的传送线损耗为最小限而达到0.1分贝/cm以下的允许等级,需要1

×

107ω

·

cm或者其以上的电阻率,进一步优选碳化硅单晶的电阻率必须接近1

×

108ω

·

cm以上的范围。

5.作为电阻率高的碳化硅单晶的实现方法,考虑碳化硅单晶具有的宽带隙而仅降低杂质的浓度的方法。例如,300k的4h碳化硅单晶具有3.2ev的宽带隙,因此电阻率随着高纯度化而升高。作为其他实现方法,提出了使用v(钒)的掺杂的方法。此外,作为其他实现方法,也有使用晶体缺陷的例子。

6.现有技术文献

7.专利文献

8.专利文献1:日本特开2002-359256号公报

技术实现要素:

9.如前所述,通过提高碳化硅单晶的纯度,能够提高碳化硅单晶的电阻率。但是,碳化硅单晶在其生长时经常会非意图地混入微量的氮,其氮浓度有时达到5

×

10

16

/cm3。通过将材料高纯度化,或者时常对装置实施高度的调整,从而可以控制在1

×

10

16

/cm3以下,但是导致碳化硅单晶的价格上涨。并且,即便是这样高纯度化的碳化硅单晶,碳化硅单晶中残留的微量的氮作为施主起作用,其活化率随着温度上升而增加。因此,碳化硅单晶的电阻率随温度上升而降低,导致在碳化硅单晶的基板上制成的器件特性例如高速、高频工作特性的降低这些不利的变化。另外,成为施主的氮除了温度的上升以外还引起例如由辐射或者光引起的载流子的激发,成为碳化硅单晶的电阻率降低的原因。

10.作为提高碳化硅单晶的电阻率的其他方法,如上所述,通过掺杂过渡元素来捕获有助于导电的电子的方法。例如通过v捕获电子来实现高的电气特性的方法,即便在前述的

氮和作为施主作用的其他的杂质的浓度高的情况下,也能够实现非常高的电阻率。然而,该方法是通过室温或者温度上升利用v暂时捕获由杂质或者晶体缺陷激活的载流子,妨碍载流子的移动而实现高的电阻率,因此存在后述的缺点。

11.作为第1个缺点,被v捕获的载流子的放出时间,随着温度上升指数级缩短,因此高温下的电子捕获实际上并不是有效的。因此,高温下的电阻率与常温相比急剧降低。因此,常温下电阻率足够高,足够高到几乎视为半绝缘性的程度的碳化硅单晶的电阻率在高温下降低。这样,在碳化硅单晶的基板上制成晶体管时,晶体管与基板之间的寄生电容增加。作为结果,晶体管的栅极与漏极

·

源极间的容量增加,所以有在碳化硅单晶的基板上制成的晶体管的输出功率在高温下降低这样的重大问题。此外,认为即便在因由晶体缺陷引起的载流子的捕获而提高电阻率时,基于相同的原理也产生该问题。

12.作为第2个缺点,基于v的电子捕获是暂时的,因此存在从捕获经过一定时间后基板的电位变化,晶体管的特性变化的问题。

13.使在碳化硅单晶的基板上制成的晶体管进行on/off工作时,off时向栅极施加负电位,因此,自由载流子被由v生成的捕获能级所捕获。由于该现象,基板带负电(charge up),因此基板的相对的电位发生波动,向扩大栅极的耗尽层的方向工作,减少流过晶体管的电流。

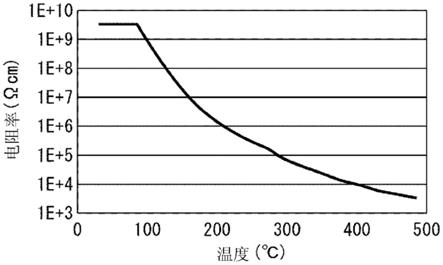

14.接着,结束on/off工作时,off时向栅极施加的负电位消失。但是,如上说,由v捕获自由载流子是暂时的,因此从on/off工作的结束随着时间经过自由载流子缓缓地放出,基板电位也变化。因此,重新开始on/off工作时,与on/off工作刚结束的情况相比,栅极的耗尽层的状态不同,流过晶体管的电流变化,晶体管的特性变化。

15.本公开是为了解决上述的问题而进行的,其目的是提供室温下的电阻率高,抑制伴随温度上升的电阻率的降低,能够抑制基板的电势的经时变化的碳化硅单晶。

16.本技术的公开所述的碳化硅单晶的特征在于,在从室温到400℃的范围,温度与电阻率呈正相关,在从室温到400℃的范围,具有至少1

×

107ω

·

cm的电阻率,室温下显示基于空穴的导电,过渡元素的浓度为1

×

10

17

/cm3以下。

17.在下面说明本公开的其他特征。

18.根据该公开,能够提供在抑制过渡元素的浓度的同时室温下显示基于空穴的导电的方式导入掺杂剂,因此电阻率高,能够抑制由温度上升所致的电阻率的降低,能够抑制基板的电势的经时变化的碳化硅单晶。

附图说明

19.图1是表示掺杂v的碳化硅单晶的电阻率的温度依赖性的图。

20.图2是表示实施方式的碳化硅单晶的电阻率的温度依赖性的图。

21.图3是半导体元件的剖视图。

22.图4是表示环境温度为常温的gan-hemt的电流/电压特性的图。

23.图5是表示环境温度为250度的gan-hemt的电压-电流特性的图。

24.图6是表示晶体管的恢复特性的说明图。

25.图7是表示gan-hemt的恢复特性的电流-时间特性的图。

具体实施方式

26.参照附图对实施方式的碳化硅单晶和半导体元件进行说明。相同的或者对应的构成要素附以相同的符号,有时省略重复的说明。

27.实施方式

28.实施方式的碳化硅单晶的多型例如为4h。实施方式的碳化硅单晶例如含有氮作为施主掺杂剂。氮的浓度可以为1

×

10

15

/cm3~5

×

10

16

/cm3的范围。根据其它例子,氮的浓度可以为1

×

10

15

/cm3~3

×

10

16

/cm3的范围。进而根据其它例子,氮的浓度可以为1

×

10

15

/cm3~1

×

10

16

/cm3的范围。另外,施主掺杂剂可以为5

×

10

16

/cm3以下的浓度的氮或者硅,或者低于1

×

10

17

/cm3的浓度的氮或者硅。

29.该实施方式的碳化硅单晶是掺杂受主的p型,室温下具有至少1

×

107ω

·

cm的固有电阻的范围的电阻率。假定硼的受主掺杂剂的浓度例如为2

×

10

15

/cm3~1

×

10

17

/cm3的范围。其掺杂剂浓度超过1

×

10

17

/cm3时,空穴的传导机制变得显著,电阻率过度降低而影响室温下的晶体的电特性,因此掺杂剂浓度必须为1

×

10

17

/cm3以下。根据其它例子,受主掺杂剂的浓度可以为2

×

10

15

/cm3~5

×

10

16

/cm3的范围。进而在其它例子中,受主掺杂剂的浓度为2

×

10

15

/cm3~3

×

10

16

/cm3的范围。作为受主掺杂剂,除硼外,也可以使用铝、锌、镁或者其他受主型掺杂剂。当然前述的受主掺杂剂的浓度随着掺杂剂的活化率而增减,例如铝的情况下与硼相比,需要几倍的大量的掺杂。换句话说,受主掺杂剂可以为1

×

10

17

/cm3以下的浓度的硼或者铝等。

30.这样,实施方式的碳化硅单晶具备至少1种的施主掺杂剂和至少1种的受主掺杂剂。而且,施主与受主的平衡使电子的传导特性被调整到室温下看不到的范围。换句话说,实施方式的碳化硅单晶室温下补偿施主,显示基于空穴的导电。

31.进一步优选使受主掺杂剂的浓度的上限为3

×

10

16

/cm3以下,添加能够维持p型的施主掺杂剂。

32.这是因为以下的理由。作为使sic基板为p型且为高电阻的方法,有仅由低浓度的施主掺杂剂进行导电控制的方法和利用施主补偿受主的载流子的方法。

33.前者,即使施主、受主两方的浓度非常低的方法能够容易地得到高电阻sic。然而,导电类型(p/n)的控制变得困难。而且即便能够控制为p型,为了使sic的电阻率与温度呈正相关,还需要存在适量的施主掺杂剂,施主掺杂剂的浓度的控制变得更困难。

34.后者,即利用施主掺杂剂补偿受主载流子的方法,首先为了维持p型,进而为了实现高电阻化,需要正确进行施主掺杂剂和受主掺杂剂的添加量控制,并且需要使有效的受主载流子为极低浓度。以施主、受主的浓度高的状态满足这些条件在实际的制作上是很困难的。

35.这些问题的解决方法是使受主掺杂剂的浓度尽可能低且为可控制的掺杂量。具体而言,非常优选使受主掺杂剂的浓度为5

×

10

15

/cm3以上3

×

10

16

/cm3以下的范围,是降低制作上的困难度的现实的解决方法。同时,如果考虑受主掺杂剂与施主掺杂剂的活化率之差,则非常优选施主掺杂剂的浓度为受主掺杂剂的浓度的10分之1~10分之4的范围。

36.实施方式的碳化硅单晶中,电阻率的控制不是基于深能级,因此从该观点考虑,钒等过渡元素的浓度不必特别限定。然而,为了避免深的能级对延迟特性的负面影响,应限制过渡元素的浓度的上限。例如如果过渡元素为v,优选使v的浓度小于1

×

10

17

/cm3。另外,v以

外的例如ni、ti之类的过渡元素的情况下,优选使过渡元素的浓度为1

×

10

16

/cm3以下或者为1

×

10

17

/cm3以下。

37.实施方式的碳化硅单晶在从室温到400℃的范围具有至少1

×

107ω

·

cm的电阻率。根据其它例子,在从室温到400℃的范围具有至少10000ω

·

cm的电阻率。此外,根据其它例子,在从室温到400℃的范围具有至少1

×

108ω

·

cm的电阻率。任一例子中,实施方式的碳化硅单晶在从室温到400℃的范围电阻率随着温度上升而提高。这是因为在该温度范围,随着温度上升有助于导电的载流子的数量减少,从而电阻率提高。

38.碳化硅单晶的电阻值的测定如下实施。首先实施传导特性的p/n判定。在判定为p型的碳化硅单晶上在表面和背面或者以恒定间隔蒸镀2点直径2厘米的tial电极而制成试样。在判定为n型的碳化硅单晶上蒸镀直径2厘米的ni电极而制成试样。两者电极的面积都大,因此不论整流性如何,由直接通电进行测定的电流电压特性、电极面积以及电极间距离计算电阻值。由此,进行电阻值与电阻值的温度依赖性测定。

39.首先,研究了高纯度化的碳化硅单晶。高纯度化的碳化硅单晶在室温下判定为n型,由sims测定的氮的浓度为1

×

10

16

/cm3。电阻值室温下为5000~10000ω

·

cm,电阻值随着温度上升而降低。

40.如上所述,碳化硅单晶因其制法而很难防止氮的混入,即便高纯度化的基板,微量的氮也作为施主发挥功能。认为作为这样的氮为主的杂质半导体的碳化硅单晶,施主的活化率随温度上升而提高,载流子指数级增加直到饱和区域,结果观察到电阻率降低的现象。

41.接下来,进行掺杂了v的碳化硅单晶研究。图1是表示掺杂了v(钒)的碳化硅单晶的电阻率的温度依赖性特性的图。常温下电阻率非常高而超过测定极限,因此未实施p/n判定。由sims测定的氮的浓度为3

×

10

16

/cm3。

42.图1中,80℃以下的电阻率为恒定值(2

×

109ω

·

cm),但这是因为根据这次的测定中使用的计测器和制成试样的限制,2

×

109ω

·

cm是能够算出的电阻率的上限。由在超过80℃的温度范围得到的测定值的arrhenius曲线的外推值推断为常温下的电阻率为1

×

10

12

ω

·

cm以上,因此认为实际的室温下的电阻率为至少2

×

109ω

·

cm以上。

43.但是,出现掺杂v的碳化硅单晶的电阻率随着温度上升在130℃的1

×

108ω

·

cm到400℃的1

×

104ω

·

cm急剧降低5个数量级以上的现象。

44.这样,电阻率随着掺杂了v的碳化硅单晶的温度上升而降低是因为室温下被v捕获的电子随着温度上升从v的放出时间变得极短,变化为表观上捕获功能不起作用的状态,成为载流子的电子增大。

45.接着,进行实施方式的碳化硅单晶研究。图2是表示实施方式的碳化硅单晶的电阻率的温度依赖性特性的图。通过sims分析得到的氮的浓度为7

×

10

15

/cm3,硼的浓度为2

×

10

16

/cm3。本测定中确认碳化硅单晶的空穴传导后,使用蒸镀p型的欧姆的直径2厘米的tial电极而制成的试样。碳化硅单晶室温下显示1

×

108ω

·

cm左右的电阻率。该值与先前所示的添加v的碳化硅单晶的室温下的电阻率(至少2

×

109ω

·

cm以上)相比,为较低的值。然而,如图2所示,实施方式的碳化硅单晶中,在从室温到400℃的范围呈现出固有电阻随着温度上升而提高的趋势。换句话说,在从室温到400℃的范围温度与电阻率呈正相关。其结果,在110℃以上的温度,实施方式的碳化硅单晶具有超过掺杂了v的碳化硅单晶的电阻率。

46.认为该现象是因为伴随温度上升,施主的活化率的增加与受主的活化率的增加相

比更大,受主补偿在此之前作为支配导电的载流子的空穴,实效上对导电有效的载流子减少。

47.即,如果基于空穴的导电占主导,则仅仅是p-型基板,但本实施方式中,通过低浓度的施主掺杂剂补偿空穴到常温下看不到由电子引起的导电特性的程度。作为施主掺杂剂的氮的浓度的一个例子如上所述为1

×

10

15

/cm3~5

×

10

16

/cm3。由此在从室温到400℃的范围温度上升的情况下,活化的施主被受主补偿,因此能够提供保持1

×

107ω

·

cm以上的电阻率的碳化硅单晶。

48.此时,碳化硅单晶中含有的过渡元素的浓度在该过渡元素在从室温到400℃的范围不自行释放有助于导电的载流子的范围内可以为任意的浓度。然而,例如碳化硅单晶显示空穴传导特性的情况下,如果过渡元素补偿高浓度的电子,则电阻率随着温度上升而急剧降低。因此,如上所述通过使过渡元素的浓度为1

×

10

17

/cm3以下,或者进一步优选为1

×

10

16

/cm3以下,则能够抑制过渡元素形成深的陷阱而捕获随着温度上升的活化率的上升下而增加的电子和空穴以促进任一方的载流子的增加。

49.碳化硅晶体的多型可以为3c、4h、6h或者15r多型。实施方式的碳化硅单晶积极地允许室温下的空穴传导,因此可以采用例如空穴迁移率小于多型4h的6h。另外,应用于器件而需要宽带隙的情况下采用4h、6h而不是采用3c。

50.通过准备包含上述的实施方式的碳化硅单晶的基板,在该基板上形成器件,能够提供半导体元件。作为基板上形成的器件,例如,可以采用金属-半导体场效应晶体管(mesfet),金属-绝缘体场效应晶体管(mosfet),高电子迁移率晶体管(hemt)等。可以假定这样的半导体元件例如为200℃以上进行工作。

51.图3是半导体元件的剖视图。该半导体元件具备以实施方式的碳化硅单晶为材料的基板1。在基板1上层叠有多个化合物半导体层。具体而言,具有形成于基板1上的下部缓冲层2、形成于下部缓冲层2上的缓冲层3和形成于缓冲层3上的肖特基层5。

52.下部缓冲层2因为具备低温形成的aln或者gan,所以也有时称为低温缓冲层。缓冲层3例如由掺杂碳的gan形成。肖特基层5例如由algan形成。在基板1上依次层叠下部缓冲层2、缓冲层3、肖特基层5而形成异质结结构。在肖特基层5上形成有栅电极7、源极电极6以及漏极电极8。作为欧姆电极的源极电极6和漏极电极8通过在肖特基层5上依次层叠alti、au而形成。作为肖特基电极的栅电极7在肖特基层5上肖特基电极pt、au而形成。图3中还示出了在肖特基层5和缓冲层3的异质结界面正下方形成二维电子气4。

53.图4和图5是表示在实施方式的碳化硅单晶上制成的gan-hemt与以浓度8

×

10

16

/cm3添加了v的碳化硅单晶的基板上制成的gan-hemt的电压-电流特性的图。图4和图5中,实线表示在实施方式的碳化硅单晶上制成的gan-hemt的电压-电流特性,虚线表示添加了在v的碳化硅单晶的基板上制成的gan-hemt的电压-电流特性。两种gan-hemt都为相同的晶体管结构。

54.图4表示环境温度为常温的gan-hemt的电流/电压特性,图5表示环境温度为250度的gan-hemt的电压-电流特性。测定中,栅极电压为4v,工作频率为1mhz。图4所示的是在实施方式的碳化硅单晶的上制成的gan-hemt和在添加了v的碳化硅单晶的基板上制成的gan-hemt的环境温度为常温的情况下的电压-电流特性。两者几乎没有差别。如上所述,在110度以下的温度下,实施方式的碳化硅单晶的电阻率低于添加了v的碳化硅单晶的电阻率,但由

图4确认不影响常温的gan-hemt的特性。

55.图5是在实施方式的碳化硅单晶上制成的gan-hemt与在添加了v的碳化硅单晶的基板上制成的gan-hemt的环境温度为250度时的电压-电流特性。

56.由图4和图5的比较可知,在添加了v的碳化硅单晶的基板上制成的gan-hemt随环境温度的上升电流显著降低。另一方面,在实施方式的碳化硅单晶上制成的gan-hemt中随着环境温度的上升的电流的降低是轻微的。换句话说能够抑制高温下的晶体管的输出功率的降低。认为该现象是因为在实施方式的碳化硅单晶上制成的gan-hemt中,高温下也维持碳化硅单晶基板的电阻率,另一方面,使用添加了v的碳化硅单晶基板的gan-hemt的情况下,被v捕获的电子的释放时间在高温下变短,因此,基板的电阻率变低,高频特性降低。

57.图6是表示晶体管的恢复特性的说明图。图6的上段示出了向晶体管输入的输入功率pin,下段示意地示出了晶体管的漏极电流id。图6的横轴为上段和下段的时间t。如图6的上段所示,向晶体管输入的信号的大小直到时间t=t0为止为小信号的电平,从时间t0到t1上升到大信号的电平,t1以后再次降低到小信号的电平。大信号的电平对晶体管过输入的电平。如图6的下段所示,晶体管的漏极电流根据输入功率在t0以前为id1,从时间t0到t1为id2。然而,将输入电力从大信号降低到小信号的t1之后的漏极电流在氮化镓(gan)的陷阱(半导体的格子缺损)的影响下漏极电流减少而一度成为id1以下,以一定的时间常数瞬时逐渐恢复到id1。一般,该现象称为恢复特性。

58.图7是表示在实施方式的碳化硅单晶的基板上制成的gan-hemt与添加了v的碳化硅单晶的基板上制成的gan-hemt的恢复特性的图,是比较图6的t=t1以后的漏极电流的行为的图。以实线表示在实施方式的碳化硅单晶的基板上制成的gan-hemt的电流-时间特性,以虚线表示在添加了v的碳化硅单晶的基板上制成的gan-hemt的电流-时间特性。

59.如图7所示,在实施方式的碳化硅单晶的基板上制成的gan-hemt的电流与在添加了v的碳化硅单晶的基板上制成的gan-hemt的电流比较,电流的降低更小。换句话说,抑制了晶体管的特性的变化。认为这是因为实施方式的碳化硅单晶中不存在有效的量的钒,即没有发生因钒引起的电子的捕获

·

释放,因此漏极电流id的降低变小,改善了恢复特性。

60.本实施方式的碳化硅单晶基板能够适用于包含微波和毫米波的高频下工作的场效应型晶体管、特别是高电子迁移率晶体管。

61.符号说明

62.1基板,2下部缓冲层,3缓冲层,4二维电子气,5肖特基层,6源极电极,7栅电极,8漏极电极。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1