包括具有六边形轮廓的晶胞的横向半导体器件的制作方法

本公开涉及半导体器件,特别是六边形横向半导体器件。本公开尤其涉及具有全顶面电流提取的六边形横向氮化镓增强模式高电子迁移率晶体管(gallium-nitrideenhancement mode high electron mobility transistor,gan-ehemt)。该半导体器件可用作电源、汽车、lidar、服务器、适配器等中的功率半导体器件(power semiconductordevice)。

背景技术:

1、如图1所示的“条带(stripe)”配置是功率半导体器件最简单、应用最广泛的布局;这要求进行仔细的终端设计。在基于pgan的ehemt中,这意味着:

2、1)pgan条带12(形成栅极端子)需要封装源极接触头(source contact)11,以避免在条带端形成二维电子气(two-dimensional electron gas,2deg)(否则漏极13-源极11短)。如图1的b所示,这引起pgan条带12的强弯曲(strong bending)14从而导致电场扰动(强对称性破裂(strong symmetry rupture))。这引致泄漏增加。

3、2)如图1的c所示,电气地去激活(隔离)16条带端15:广泛采用的解决方案是对在终端区的algan/gan进行n2注入(永久的材料破坏以划定有源区(active region))。这种注入通过pgan层进行,这破坏了pgan原子结构并潜在地造成泄漏。

4、以上两种解决方案都表现出电气缺点:on和off两种状态下的潜在泄漏增加导致电路消耗随时间增加以及栅极随时间劣化(高温反向偏置(high temperature reversebias,htrb)、高温栅极偏置(high temperature gate bias,htgb)htgb、vth偏移等)。在on状态下报告这样的设计/布局的具体问题(即vth偏移和htgb缺点)。图2示出了与由栅极端设计引起的夹断(pinch-off)属性劣化有关的这样的漏极泄漏增加的示例,其中,曲线21示出了一般晶体管的预期泄漏,而曲线22示出了在亚阈值区域中(甚至在低vds下)的高漏源泄漏(drain to source leakage)。

技术实现思路

1、本公开的目的是提供上述问题的解决方案。因此,本公开的目的是提供减少漏极泄漏的半导体器件。

2、该目的通过独立权利要求的特征来实现。其他实施方式在从属权利要求、说明书、以及附图中显而易见。

3、本公开的基本思想是消除上述功率半导体器件的“条带”结构,并使用封闭的几何形状,即封闭的晶胞。这种颠覆性的解决方案改善了对称性,并提供了最大的能力来填充“管芯(die)”区域(通常,管芯为矩形)。从被分析的三种不同形状(见图3)可见,六边形是最优的封闭形状。为了克服栅极端的缺点,根据本公开的解决方案将条带布局改变为具有全顶面电流提取的六边形布局。下文给出了更多的细节。

4、根据本公开的解决方案解决了与pgan栅极概念和标准的条带配置的组合有关的横向pgan hemt结构的特定缺点。六边形晶胞概念消除了“pgan”端区(end region)并恢复了对称性。主要增益在于消除寄生泄漏(parasitic leakage)。全顶面电流提取允许克服横向器件的背面接触(沟槽蚀刻、背面光刻、双面晶圆(wafer)处理等)的技术复杂性和相关成本。

5、上述结构为gan hemt,即横向功率半导体器件(lateral power semiconductordevice)。该结构可以实现为pgan栅极hemt(pgan-gate hemt)。pgan栅极hemt是具有p型gan半导体中的栅极的gan hemt,以获得e模式功能(提供常关(normally off)器件的增强模式)。可以通过mg掺杂(mg-doped)gan材料的外延生长来获得p型层,但其他技术也是可行的。虽然我们在下文所示的示例中称该栅极为“pgan栅极”(因为该栅极包含p型掺杂),但本公开还涵盖该栅极的其他工程实例,例如交替的若干层p型gan层、n型gan层、或未掺杂gan层(undoped-gan layer)。该结构是六边形的封闭晶胞布局。该布局取代了标准的条带布局,在标准的条带布局中,栅极、漏极、以及源极是平行的条带,其结束于有源区域的界限附近或延伸超过有源区的界限。六边形可以在六边形的中心具有源极(或漏极)。六边形(源极、漏极、栅极)的拐角可以倒圆以减小局部电场。该结构可以构建在异质外延体(绝缘体上硅基氮化镓(gan-on-soi,soi基gan)、蓝宝石基氮化镓(ganonsaphire,蓝宝石基gan)、碳化硅基氮化镓(gan-onsic,sic基gan)等)上或构建在氮化镓基氮化镓(gan-on-gan,gan基gan)材料上。pgan栅极可以是平面层或填充层(例如,在pgan在沟槽栅极中再生长(regrowth)的情况下)。漏极电流、源极电流、以及栅极电流的提取在晶圆的顶面完成。

6、根据第一示例(如下图4和图5所示),可以通过使用一个金属层级提取每个端子(源极、漏极、以及栅极)的电流来实现电流提取。可以使用另一金属层级将电流路由到接合焊盘(bond pad)(或器件外)。

7、根据第二示例(如下图6和图7所示),可以通过在金属平面(层级)之间将路由(routing)共享到外部来完成电流提取。例如,源极通过金属1路由,漏极和栅极通过金属2路由。

8、根据第三示例(如下图8和图9所示),可以使用用于每个端子的专用金属层级来提取电流。例如,栅极通过金属1路由,源极通过金属2路由,漏极通过金属3路由。

9、这样的设计可以实现以下益处:减少off状态下的器件泄漏(电路消耗);提高htrb和htgb下的器件寿命;消除与泄漏有关的vth偏移;解决(与条带耦合的)横向结构典型的电迁移约束;减小管芯尺寸,降低成本;提高功率密度;减少管芯上的热不均匀性和电不均匀性;解决栅极端处的电场峰值的问题;设计紧凑(即减小成本);克服对背面晶圆处理和蚀刻技术的需要;减小技术复杂度和成本。

10、为了详细描述本发明,将使用以下术语、缩写、以及符号:

11、高电子迁移率晶体管high electron mobility transistor,hemt

12、氮化镓gallium-nitride,gan

13、增强模式高电子迁移率晶体管enhancement mode high electron mobilitytransistor,ehemt

14、高温反向偏置high temperature reverse bias,htrb

15、高温栅极偏置high temperature gate bias,htgb

16、hemt是一种高电子迁移率晶体管(hemt),也称为异质结构场效应晶体管(heterostructure field-effect transistor,hfet)或调制掺杂场效应晶体管(modulation-doped field-effect transistor,modfet),hemt是一种场效应晶体管,在两种具有不同带隙的材料之间引入一个结(junction)(即异质结)作为沟道(channel),而不是mosfet通常采用的掺杂区。虽然取决于器件的应用存在很大的差异,但是一种常用的材料组合是gaas和algaas。

17、根据第一方面,本公开涉及一种半导体器件,包括:管芯层,包括主表面;多个第一端子,安装在管芯层的主表面上,其中,第一端子形成具有六边形轮廓的晶胞的栅格,该晶胞跨管芯层的主表面并排布置;多个第二端子,安装在管芯层的主表面上,其中,每个第二端子形成布置在相应第一端子的晶胞内的六边形轮廓,其中,在第二端子与第一端子之间存在间隙;多个第三端子,安装在管芯层的主表面上,其中,每个第三端子形成为六边形并布置在相应的第二端子的六边形轮廓内,其中,在第三端子与第二端子之间存在第二间隙;以及至少两个金属化层,布置在多个第一端子、多个第二端子、以及多个第三端子上,用于接收来自多个第一端子、多个第二端子、以及多个第三端子的电流。

18、间隙(gap)是指各种开口(opening)、空位(vacant space)、缺失(lack)、或停顿(pause)。间隙表示两个对象(如上述端子)之间的缺口或孔。两个端子之间的间隙意味着两个端子不互相接触。

19、可以用隔离材料来填充两个端子之间的间隙,以避免两个端子之间的电气连接。

20、在一个示例中,第一端子可以是源极端子,第二端子可以是栅极端子,第三端子可以是漏极端子。在另一示例中,第一端子可以是栅极端子,第二端子可以是漏极端子,第三端子可以是源极端子。也可以使用端子之间的任何其他分配。

21、第一端子和第三端子不是强制性的物理实体,而只是称为源极和漏极的区域。

22、这些端子可能表示algan层中的空腔(cavity),而不一定表示algan层顶部的实体。这意味着,如图10所示,第一端子和第三端子可以放置在主表面111的顶部上,或者稍微低于主表面111。

23、第一端子和第三端子是可以位于主表面的顶部或低于主平面的接触头(在低于主平面的情况下,通过移除管芯或蚀刻穿过管芯直至厚度tcontact来获得端子。tcontact可以位于距主表面0nm与大于algan厚度的深度之间)。

24、根据第一方面的这种半导体器件提供了一种针对与pgan栅极概念和标准的条带配置的组合有关的横向pgan hemt结构的特定缺点的解决方案。该半导体器件的六边形晶胞结构消除了“pgan”端区,恢复了对称性。因此,可以消除寄生泄漏。该半导体器件的全顶面电流提取允许(例如,通过使用沟槽蚀刻、背面光刻、双面晶圆处理等)克服横向器件的背面接触的技术复杂性和相关成本。

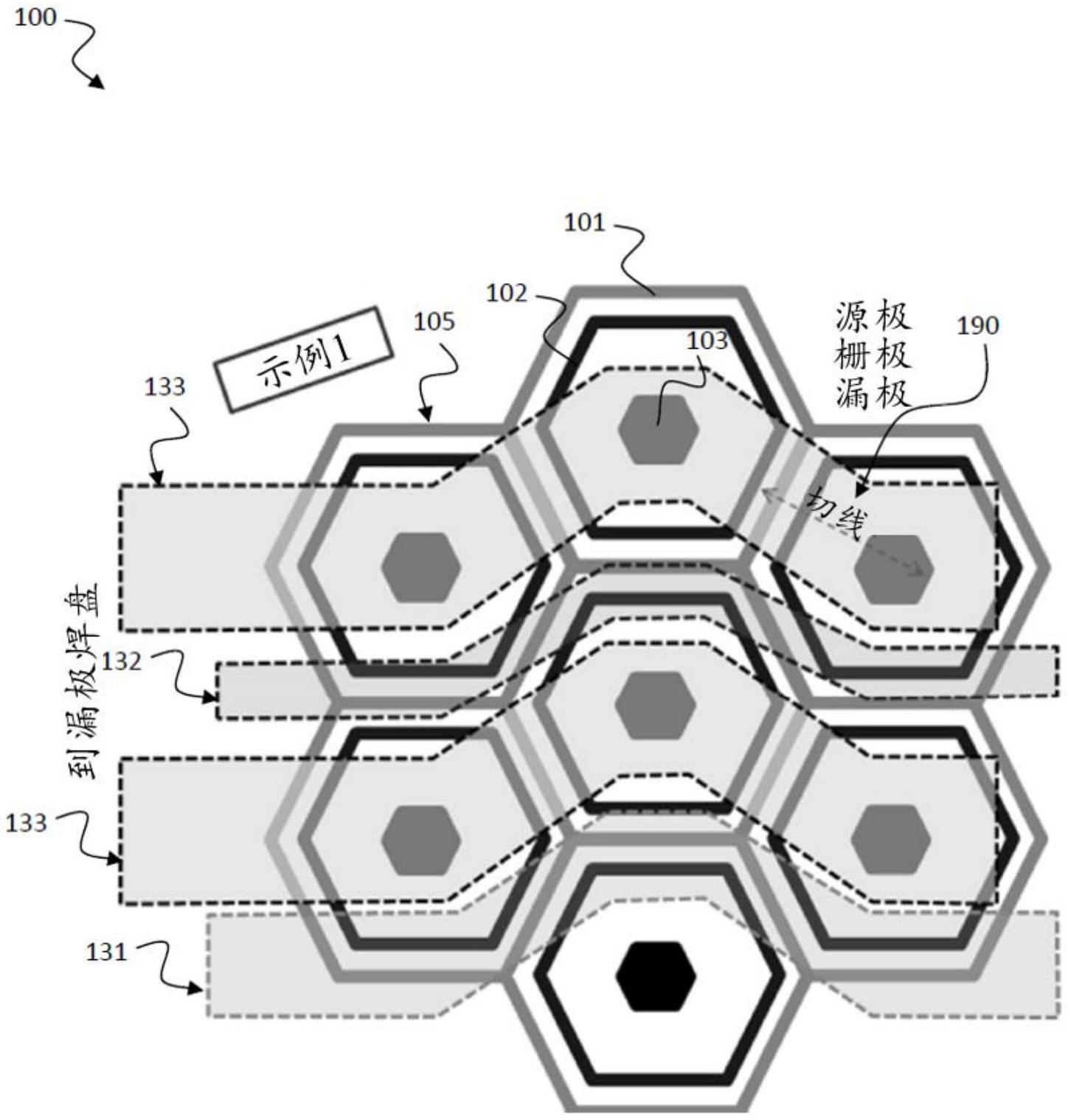

25、在半导体器件的示例性实施方式(以下称为示例1)中,第一金属化层m1包括彼此分隔开的第一部分、第二部分、以及第三部分,其中,第一金属化层m1的第一部分覆盖每个第一端子的至少部分以接收来自多个第一端子的电流,其中,第一金属化层m1的第二部分覆盖每个第二端子的至少部分以接收来自多个第二端子的电流,其中,第一金属化层m1的第三部分覆盖每个第三端子的至少部分以接收来自多个第三端子的电流。

26、根据示例1的这种半导体器件提供了以下优点:减少off状态下的器件泄漏,提高htrb和htgb下的器件寿命,消除与泄漏有关的vth偏移,减小管芯尺寸和降低成本。其他优点是提高功率密度,减少管芯上的热不均匀性和电不均匀性,减小栅极端处的电场峰值。无需背面晶圆处理和蚀刻技术。

27、在该半导体器件的示例性实施方式(也可以属于示例1)中,在第一金属化层m1上布置第二金属化层m2,第二金属化层m2包括彼此分隔开的第一部分、第二部分、以及第三部分,其中,第一金属化层m1的第一部分连接到第二金属化层m2的第一部分,以将从多个第一端子提取的电流路由到另一实体,其中,第一金属化层的第二部分连接到第二金属化层m2的第二部分,以将从多个第二端子提取的电流路由到另一实体,其中,第一金属化层m1的第三部分连接到第二金属化层m2的第三部分,以将从多个第三端子提取的电流路由到另一实体。

28、在该半导体器件的示例性实施方式(也可以属于示例1)中,第二金属化层m2的第一部分形成为覆盖多个第一端子的六边形轮廓的部分的波浪形,其中,第二金属化层m2的第二部分形成为覆盖多个第二端子的六边形轮廓的部分的波浪形,其中,第二金属化层m2的第三部分形成为覆盖多个第三端子的六边形的波浪形。

29、在该半导体器件的示例性实施方式(也可以属于示例1)中,在第一金属化层m1与第二金属化层m2之间布置隔离层,其中,第一金属化层m1的第一部分与第二金属化层m2的第一部分之间的连接、第一金属化层m1的第二部分与第二金属化层m2的第二部分之间的连接、以及第一金属化层m1的第三部分与第二金属化层m2的第三部分之间的连接由穿过隔离层的通孔形成。

30、在该半导体器件的示例性实施方式(以下称为示例2)中,第一金属化层m1包括彼此分开的第一部分和第二部分,其中,第一金属化层m1的第一部分覆盖多个第一端子的至少部分以接收来自第一端子的电流,其中,第一金属化层m1的第二部分覆盖多个第二端子的至少部分以接收来自第二端子的电流。

31、根据示例2的这种半导体器件提供了与针对示例1的半导体器件所描述的相同的优点,即减少off状态下的器件泄漏,提高htrb和htgb下的器件寿命,消除与泄漏有关的vth偏移,减小管芯尺寸和降低成本。其他优点是提高功率密度,减少管芯上的热不均匀性和电不均匀性,减小栅极端处的电场峰值。无需背面晶圆处理和蚀刻技术。

32、在该半导体器件的示例性实施方式(也可以属于示例2)中,在第一金属化层m1上布置第二金属化层m2,第二金属化层m2包括彼此分隔开的第一部分和第二部分,其中,第二金属化层m2的第一部分覆盖多个第三端子的至少部分以接收来自第三端子的电流。

33、在该半导体器件的示例性实施方式(也可以属于示例2)中,第二金属化层m2的第一部分用于将来自第三端子的电流路由到另一实体,其中,第一金属化层(m1)的第一部分用于将来自第一端子的电流路由到另一实体,并且其中,第二金属化层m2的第二部分连接到第一金属化层m1的第二部分,以将来自第二端子的电流路由到另一实体。

34、在该半导体器件的示例性实施方式(也可以属于示例2)中,在第一金属化层(m1)与第二金属化层m2之间布置隔离层,其中,第二金属化层m2的第二部分与第一金属化层m1的第二部分之间的连接由穿过隔离层的通孔形成。

35、在该半导体器件的示例性实施方式(以下称为示例3)中,第一金属化层m1覆盖第一端子的至少部分,以接收来自第一端子的电流,并将来自第一端子的电流路由到另一实体,其中,第二金属化层m2覆盖第二端子的至少部分,以接收来自第二端子的电流,并将来自第二端子的电流路由到另一实体,其中,第三金属化层m3覆盖第三端子的至少部分,以接收来自第三端子的电流,并将来自第三端子的电流路由到另一实体。

36、根据示例3的这种半导体器件提供了与针对示例1的半导体器件所描述的相同的优点,即减少off状态下的器件泄漏,提高htrb和htgb下的器件寿命,消除与泄漏有关的vth偏移,减小管芯尺寸和降低成本。其他优点是提高功率密度,减少管芯上的热不均匀性和电不均匀性,减小栅极端处的电场峰值。无需背面晶圆处理和蚀刻技术。

37、在该半导体器件的示例性实施方式(也可以属于示例3)中,在第一金属化层m1上布置第二金属化层m2,并且其中,在第二金属化层m2上布置第三金属化层m3。

38、在该半导体器件的示例性实施方式(也可以属于示例3)中,第三金属化层m3完全覆盖管芯层的主表面。

39、在该半导体器件的示例性实施方式(也可以属于示例3)中,至少部分地被第三金属化层m3覆盖的第三端子是漏极端子,并且其中,第一端子和第二端子分别是源极端子或栅极端子。

40、当从m2或m3直接到第一端子、第二端子、或第三端子时,这可以直接完成(例如如图9所示)或通过穿过隔离层的通孔或插头来完成(例如如图11所示)。

41、在该半导体器件的示例性实施方式中,多个第一端子的六边形轮廓、多个第二端子的六边形轮廓、或多个第三端子的六边形中的至少一个具有圆角(rounded corner)或切角(cut corner)。

42、图12示出了具有标准角601的六边形、具有切角602的六边形、以及具有圆角603的六边形的示例。

43、在该半导体器件的示例性实施方式中,该半导体器件包括横向功率半导体器件,该横向功率半导体器件包括gan高电子迁移率晶体管(hemt)器件。

44、hemt是一种高电子迁移率晶体管(hemt),也称为异质结构场效应晶体管(hfet)或调制掺杂场效应晶体管(modfet),hemt是一种场效应晶体管,在两种具有不同带隙的材料之间引入一个结(即异质结)作为沟道,而不是mosfet通常采用的掺杂区。虽然取决于器件的应用存在很大的差异,但是一种常用的材料组合是gaas和algaas。

45、在该半导体器件的示例性实施方式中,管芯层包括gan层和在该gan层上方的algan层,其中,主表面形成在algan层的顶部。

46、在该半导体器件的示例性实施方式中,多个第一端子、多个第二端子、以及多个第三端子形成在algan层顶部的一个层级上;或者多个第一端子、多个第二端子、以及多个第三端子中的至少一个延伸到algan层中;或者多个第一端子、多个第二端子、以及多个第三端子中的至少一个延伸到gan层中。

47、在该半导体器件的示例性实施方式中,该半导体器件包括gan hemt,该gan hemt包括至少部分p型gan半导体中的栅极,以获得提供常关器件的增强模式。

48、栅极可以是完全p型或部分p型的。这意味着,栅极可以设计成包括多个p型、n型、或未掺杂型的gan。例如,栅极可以包括p型、n型、或未掺杂的gan层的混合。

49、通过mg掺杂gan材料的外延生长,可以获得p型层和n型层。其他技术也是可行的。

50、在该半导体器件的示例性实施方式中,gan层构建在异质外延体上(特别是soi基gan、蓝宝石基gan、或sic基gan),或者构建在gan基gan材料上。

51、在该半导体器件的示例性实施方式中,特别是在pgan在沟槽栅极中再生长的情况下,多个第二端子包括形成为平面层或填充层的pgan栅极。

52、在该半导体器件的示例性实施方式中,至少两个金属化层m1、m2用于将电流路由到另一实体。

- 还没有人留言评论。精彩留言会获得点赞!