在半导体衬底上的三维结构中填充间隙的方法与流程

在半导体衬底上的三维结构中填充间隙的方法

1.相关申请的引用

2.本技术要求于2020年4月24日提交的美国临时申请号63/014,916的优先权,其全部内容通过引用并入本文。

技术领域

3.本公开总体上涉及半导体器件制造领域,并且更具体地,涉及用于填充半导体衬底上的诸如沟槽或孔的三维结构中的间隙的方法。

背景技术:

4.在高长宽比的沟槽或孔内沉积薄膜对于半导体制造领域(例如在间隙填充工艺中)很有用。利用诸如原子层沉积(ald)、等离子体增强原子层沉积(peald)、化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)等方法,可以将薄膜直接沉积在三维(3d)结构中,例如高长宽比孔内。已经注意到,在高长宽比结构中沉积薄膜时,会至少在沟槽或孔的上部上形成悬垂或凸出部分。因此,沟槽或孔的上部可能首先被薄膜填充,并且沟槽的间隙从顶部闭合,使得在沟槽的中部中产生一些空隙和/或接缝。类似地,在沟槽具有负斜率的情况下,其中沟槽的上部的宽度较小,而沟槽的下部的宽度较大,沟槽的上部可能也首先填充薄膜,且沟槽的间隙从顶部闭合,使得在沟槽的中部中产生一些空隙和/或接缝。

技术实现要素:

5.为了总结所描述的技术和相对于现有技术所获得的优点,在此描述所描述的技术的某些目的和优点。在所描述的技术的任何特定实施例中,并非所有这些目的或优点都可以实现。因此,例如,本领域技术人员将认识到,可以以实现或优化本文所教导的一个优点或一组优点的方式实施或执行所描述的技术,而不必实现本文所教导或建议的其他目的或优点。

6.一个方面是一种在半导体衬底的三维结构中填充间隙的方法,该方法包括:使用利用具有第一频率的第一射频(rf)功率激活的至少一种反应气体将薄膜沉积在三维结构上,三维结构包括沟槽和/或孔;以及使用利用具有小于第一频率的第二频率的第二rf功率激活的至少一种蚀刻剂蚀刻沉积的薄膜。

7.上述方法还包括重复至少一次沉积和蚀刻的循环,直到沟槽和/或孔被薄膜填充。在上述方法中,反应气体包括氧气。在上述方法中,反应气体包括o2、o3、h2o、no2、n2o中的至少一个,或其组合。在上述方法中,第一频率在约100khz至约3,000mhz的范围内。在上述方法中,第一频率在约27.12mhz至约100mhz的范围内。在上述方法中,第一rf功率在约100瓦至约20,000瓦的范围内。在上述方法中,第一rf功率在约500瓦至约3,000瓦的范围内。

8.在上述方法中,第二频率在约3khz至约13,560khz的范围内。在上述方法中,第二频率在约100khz至约5,000khz的范围内。在上述方法中,第二rf功率在约100瓦至约500瓦的范围内。在上述方法中,第一频率在约27.12mhz至约100mhz的范围内,且其中第二频率在

约100khz至约5,000khz的范围内。在上述方法中,蚀刻剂包括氟。在上述方法中,蚀刻剂包括nf3、clf3、f2、sf6、cf4中的至少一个,或其组合。在上述方法中,沟槽和/或孔的长宽比至少约为20:1。

9.在上述方法中,长宽比在约30:1至约80:1的范围内。在上述方法中,沟槽和/或孔的宽度至少为约200nm,且其中蚀刻剂气体包括sf6、cf4中的至少一个,或其组合。在上述方法中,当沟槽和/或孔的宽度至少约为200nm时,重复执行约1

‑

10次。在上述方法中,当沟槽和/或孔的宽度在约150nm至约200nm的范围内时,重复执行约1

‑

20次。在上述方法中,当沟槽和/或孔的宽度在约100nm至约150nm的范围内时,重复执行约1

‑

30次。

10.在上述方法中,当沟槽和/或孔的宽度为约100nm或更小时,重复执行约1

‑

40次。在上述方法中,沉积或蚀刻中的至少一个在约50℃到约600℃的范围内的温度下执行。在上述方法中,沉积或蚀刻中的至少一个在约1torr至约5torr的范围的压力下执行。在上述方法中,通过原子层沉积(ald)工艺、等离子体增强ald(peald)工艺或等离子体增强化学气相沉积(pecvd)工艺中的至少一种执行沉积。

11.另一方面方面是一种在半导体衬底上的三维结构中填充间隙的方法,该方法包括:通过气相沉积工艺将薄膜至少沉积在三维结构上,气相沉积工艺包括用反应气体接触三维结构,三维结构包括沟槽和/或孔;以及使用至少一种蚀刻剂来蚀刻所沉积的薄膜,该至少一种蚀刻剂被频率在约3khz到约13,560khz的范围内的rf功率激活。

12.上述方法还包括重复至少一次沉积和蚀刻的循环,直到沟槽和/或孔被薄膜填充。在上述方法中,沉积包括用在约3khz到约13,560khz的范围内的频率激活反应气体。在上述方法中,沉积包括用在约100khz到约3,000mhz的范围内的频率激活反应气体。在上述方法中,rf功率在约100瓦至约500瓦的范围内。在上述方法中,蚀刻剂包括nf3、clf3、f2、sf6、cf4中的至少一个,或其组合。在上述方法中,沟槽和/或孔的长宽比至少约为20:1。在上述方法中,沉积工艺包括原子层沉积(ald)工艺、等离子体增强ald(peald)工艺或等离子体增强化学气相沉积(pecvd)工艺中的至少一种。

13.另一方面是一种在半导体衬底上方的三维结构中填充间隙的方法,该三维结构包括沟槽和/或孔,该方法包括:使用利用具有第一频率的rf功率激活的反应气体将薄膜至少沉积在三维结构上;以及蚀刻所沉积的薄膜,使得形成在沟槽和/或孔的上表面上的薄膜的第一部分比形成在沟槽和/或孔的其余表面上的薄膜的第二部分蚀刻得更多。

14.上述方法还包括重复至少一次沉积和蚀刻的循环,直到沟槽和/或孔被薄膜填充。在上述方法中,执行蚀刻使得形成在沟槽和/或孔的中间表面上的薄膜的第三部分比形成在沟槽和/或孔的下表面上的薄膜的第四部分蚀刻得更多。在上述方法中,执行蚀刻,使得薄膜的第一部分比形成在三维结构的顶部上的薄膜的第五部分蚀刻得更多。在上述方法中,三维结构的顶部包括邻接沟槽和/或孔的上表面的边缘部分,且其余部分不包括该边缘部分,且其中形成在三维结构的边缘部分上的薄膜的第六部分比形成在三维结构的其余部分上的薄膜的第七部分蚀刻得较少。

15.在上述方法中,使用利用具有小于第一频率的第二频率的rf功率激活的蚀刻剂执行蚀刻。在上述方法中,第二频率在约3khz至约13,560khz的范围内。在上述方法中,执行沉积,使得在沟槽和/或孔的上部被薄膜填充之前,沟槽和/或孔的下部被薄膜填充。在上述方法中,执行沉积使得薄膜的厚度在沟槽和/或孔的整个内表面上基本是均匀的。

16.另一方面是一种在半导体衬底上方的三维结构中填充间隙的方法,该三维结构包括负斜率的沟槽,该方法包括:将负斜率的沟槽转换为正斜率的沟槽;使用反应气体将薄膜沉积在正斜率的沟槽中;使用蚀刻剂蚀刻所沉积的薄膜;以及重复至少一次沉积和蚀刻的循环,直到正斜率的沟槽被薄膜填充。

17.在上述方法中,转换包括将沉积抑制剂提供给负斜率的沟槽,同时将薄膜沉积在负斜率的沟槽中。在上述方法中,沉积抑制剂包括n2抑制剂。在上述方法中,用频率在约3khz至约13,560khz的范围内的rf功率激活蚀刻剂。在上述方法中,rf功率在约100瓦至约500瓦的范围内。在上述方法中,使用利用rf功率激活的反应气体执行沉积,该rf功率的频率在约100khz至约3,000mhz的范围内。在上述方法中,rf功率在约100瓦至约20,000瓦的范围内。在上述方法中,蚀刻包括加宽正斜率的沟槽的上部。

18.另一方面是一种在半导体衬底上方的三维结构中填充间隙的方法,该方法包括:使用反应气体将薄膜至少沉积在三维结构上,三维结构包括具有长宽比的沟槽和/或孔;蚀刻所沉积的薄膜,使得沟槽和/或孔在沟槽和/或孔的不同部分中以不同的蚀刻速率蚀刻;以及重复至少一次沉积和蚀刻的循环,直到沟槽和/或孔被薄膜填充。

19.在上述方法中,执行蚀刻,使得使用用rf功率激活的蚀刻剂蚀刻所沉积的薄膜,该rf功率的频率在约3khz至约13,560khz的范围内,rf功率在约100瓦至约500瓦的范围内。在上述方法中,形成在沟槽和/或孔的上表面上的薄膜的第一部分的蚀刻速率高于形成在沟槽和/或孔的其余表面上的薄膜的第二部分。在上述方法中,沉积包括用rf功率激活反应气体,rf功率的频率在约100kh至约3,000mhz的范围内,rf功率在约100瓦至约20,000瓦的范围内。在上述方法中,长宽比至少约为20:1。在上述方法中,三维结构包括三维nand闪存元件。在上述方法中,填充在沟槽和/或孔中的薄膜基本上没有空隙和/或接缝。

20.另一方面是通过上述方法制造的半导体薄膜图案,其中填充在沟槽和/或孔中的薄膜基本上没有空隙和/或接缝。在上述半导体薄膜图案中,空隙/接缝的体积与沉积的薄膜的体积的比率在约0.001至约0.005或更小的范围内。在上述半导体薄膜图案中,填充在沟槽和/或孔中的薄膜不包含可检测的空隙和/或接缝。

21.另一方面是包括上述半导体薄膜图案的半导体衬底。

22.一方面的任何特征均适用于本文中标识的所有方面。而且,一方面的任何特征可以以任何方式独立地、部分地或全部地与本文描述的其他方面进行组合,例如,一个、两个或三个或更多方面可以全部或部分地组合。此外,一个方面的任何特征可以使得对于其他方面是可选的。

附图说明

23.通过结合附图的以下描述和所附权利要求,本公开的前述和其他特征将变得更加完全显而易见。应当理解,这些附图仅描绘了根据本公开的几个实施例,而不应被认为是对其范围的限制,将通过使用附图以附加的特征和细节来描述本公开。

24.图1示出了根据一些实施例的间隙填充工艺。

25.图2示出了根据一些实施例的另一间隙填充工艺。

26.图3示出了根据一些实施例的示例间隙填充工艺。

27.图4示出了根据一些实施例的在半导体制造工艺中在图案化的半导体衬底中的特

征或结构中填充间隙的示例方法。

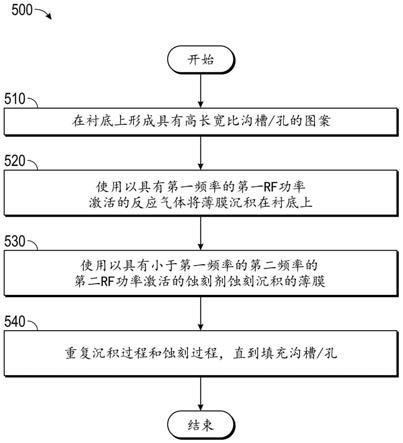

28.图5示出了根据一些实施例的在半导体制造工艺中在图案化的半导体衬底中的特征或结构中填充间隙的另一示例方法。

29.图6示出了根据一些实施例的间隙填充工艺的工艺序列。

30.图7a和7b是示出了根据一些实施例的频率与在沉积步骤期间生成的氧自由基的量之间的关系的示例图示。

31.图8是示出了根据一些实施例的频率与在沉积步骤期间生成的氧自由基的量之间的关系的另一示例图示。

32.图9a和9b是示出了根据一些实施例的频率与蚀刻过程期间的离子轰击效应的量之间的关系的示例图示。

33.图10a、10b和10c是示出了根据一些实施例的蚀刻频率与蚀刻过程期间的离子轰击效应的量之间的关系的附加示例图示。

34.图11a是示出根据一些实施例的在图案化的半导体衬底中的结构的不同部分处的蚀刻速率的图示。

35.图11b是示出根据比较例的在图案化的半导体衬底中的结构的不同部分处的蚀刻速率的图示。

36.图12是使用不同的rf频率的根据一些实施例和根据比较例的图案的不同部分处的不同蚀刻速率的比较图。

37.图13a示出了根据一些实施例的填充在间隙中的无接缝薄膜。

38.图13b示出了根据比较例的在其中具有接缝的薄膜。

39.图14示出了根据一些实施例的在半导体制造工艺中填充半导体图案中的间隙的另一示例方法。

40.图15示出了根据一些实施例的在半导体制造工艺中填充负斜率的半导体图案中的间隙的示例过程。

41.图16示出了根据一些实施例的填充图15的负斜率的半导体图案中的间隙的示例方法。

具体实施方式

42.本文提供了用于填充诸如高长宽比沟槽、通孔或孔的特征或结构的间隙填充方法的各种实施例。在一些实施例中,该方法减少或避免了间隙或接缝的形成。例如,在某些实施例中,本文公开的间隙填充方法使用用于沉积工艺的高频率rf功率和用于蚀刻工艺的低频率rf功率的组合。高频率可以用于在沉积工艺中激活反应气体。高频率的使用可以改善等离子体气体(即,反应气体自由基)向诸如沟槽/孔之类的结构中的渗透,从而在整个结构中获得更均匀的沉积。高频率可以例如在约13.56mhz至约100mhz的范围内。低频率可以用于在蚀刻工艺中激活蚀刻剂。使用低频率可以增加离子轰击效应,使得更多的较高能蚀刻剂气体自由基可以主动与薄膜碰撞,特别地,形成在结构的顶部上的薄膜,而较少的高能蚀刻剂气体自由基与形成在结构的下部上的薄膜碰撞。结果,形成的结构的顶部上的薄膜可以比形成在结构的下部上的薄膜被蚀刻得更多。例如,低频率可以在约3khz至约13,560khz的范围内。通过相对于底部蚀刻顶部,沉积工艺可以从底部向上填充特征。结果,基于高频

率的沉积和基于低频率的蚀刻的组合可以用于在结构中形成基本上没有空隙和接缝的薄膜。尽管基于原子层沉积(ald)或等离子体增强ald(peald)描述了各种实施例,但是所描述的技术不限于此,并且可以应用于诸如等离子体增强化学气相沉积(pecvd)等涉及等离子体气体的其他气相沉积方法。

43.在高长宽比的沟槽或孔内沉积薄膜对于半导体制造领域(例如在间隙填充工艺中)很有用。使用诸如原子层沉积(ald)的方法,可以将薄膜直接沉积在三维(3d)结构中,例如在高长宽比孔内。如上所述,该方法可以包括沉积部分或过程以及蚀刻部分或过程。在一些实施例中,使用诸如ald、peald或pecvd的方法,以在沉积过程(或沉积部分或阶段)中沉积薄膜。接着是蚀刻过程,其中对沉积的薄膜进行蚀刻。可以重复进行沉积和蚀刻过程以填充特征或结构,基本上不会形成空隙或接缝。

44.图1示出了间隙填充工艺100。间隙填充工艺100包括薄膜沉积过程110和蚀刻过程120。沉积过程110可以是气相沉积工艺。在薄膜沉积过程110中,薄膜116沉积在形成在半导体图案114中的孔或沟槽112中。在一些实施例中,沟槽112具有长宽比(ar),其为沟槽112的宽度(w)与高度(h)的比(w/h)。在沉积过程110期间,可能至少在沟槽112的上部上形成悬垂或凸出部分118。在蚀刻过程120中,悬垂或凸出部分118被蚀刻剂蚀刻(参见蚀刻过程120中的虚线)。将沉积过程110和蚀刻过程120重复n次,直到沟槽112被薄膜填充为止,如过程130所示,其中n为自然数。

45.图2示出了另一间隙填充工艺200。间隙填充工艺200包括抑制剂提供过程210和沉积过程220。在抑制剂提供过程210中,将利用等离子体气体激活的抑制剂216提供到包括三维结构(例如沟槽212)的半导体图案214上。在一些实施例中,抑制剂或沉积抑制剂可例如在诸如ald的气相沉积工艺中用于抑制或防止源气体吸附到半导体图案上,以抑制或减少薄膜沉积。在图示的抑制剂提供过程210中,可以用等离子气体(抑制剂等离子体)激活抑制剂。抑制剂216可通过将半导体图案214的顶部和沟槽212的上表面转换成钝化区域来抑制源气体的吸附,从而在半导体图案214的顶部和沟槽212的上表面上形成较少量的薄膜。例如,当氮自由基用作抑制剂时,它可能与半导体图案214表面上的氢元素反应并蒸发成nh3,从而导致源气体在半导体图案214上的结合减少。在一些实施例中,抑制剂改变衬底表面以减少或抑制随后的沉积,使得改变的衬底表面可以具有钝化层的特性。在随后的沉积过程220中,将源气体和反应气体交替提供到沟槽212,以形成薄膜222。由于抑制剂216,与在沟槽212的下部区域相比,较少量的薄膜222沉积在沟槽212的上部区域和图案214的顶部中。将抑制剂提供过程210和沉积过程220重复n次,直到沟槽212被薄膜填充,如过程230所示。

46.然而,上述间隙填充工艺100和200的局限性在于,随着长宽比的增加,例如,大于约20:1,薄膜中可能会形成一个或多个不期望的空隙或接缝。特别地,对于3d nand闪存元件,随着垂直堆叠栅极的高度增加,不期望的空隙或接缝也可能增加。因此,在高的长宽比孔内形成基本上没有空隙或接缝的薄膜将是有利的。

47.本公开的一些实施例在间隙填充工艺中使用薄膜沉积以减少或避免形成空隙或接缝的方式来填充诸如高长宽比沟槽、通孔或孔之类的特征或结构。特征或结构可以被任何期望的材料填充,例如sio2。将参考图3

‑

16描述各种实施例。

48.图3示出了根据一些实施例的示例间隙填充工艺300。间隙填充工艺300包括薄膜沉积过程310和蚀刻过程320。在薄膜沉积过程310中,薄膜316被沉积在形成在衬底(未示

出)的半导体图案314的三维(3d)结构中。为了方便起见,图3中仅示出了半导体图案314的靠近3d结构的上表面的一部分。3d结构可以包括沟槽、孔、间隙或开口中的一个或多个。为了方便起见,本公开将主要使用术语“沟槽”,然而,所公开的实施例不限于填充沟槽。

49.沉积过程310可以通过包括但不限于原子层沉积(ald)、等离子体增强ald(peald)或等离子体增强化学气相沉积(pecvd)的气相沉积方法来执行。可以选择在这些气相沉积方法中使用的反应物以沉积期望的材料。在一些实施例中,在沉积过程310中使用peald工艺。peald工艺可以包括例如交替地和顺序地使衬底与两种或多种反应物接触,其中至少一种被激活。在一些实施例中,在沉积过程310中使用pecvd工艺。例如,在一些实施例中,衬底与一种或多种反应气体接触,其中至少一种被等离子体激活,等等。

50.沟槽312可以具有高长宽比。在一些实施例中,高长宽比可以至少为约20:1。例如,高长宽比可以在约20:1至约80:1的范围内。作为另一示例,高长宽比可以在约30:1至约80:1的范围内。这些仅是示例,也可以使用其他长宽比(例如,小于约20:1或大于约80:1)。

51.如图3所示,可以执行沉积过程310以减少、避免或最小化在沟槽312的上表面和图案314的顶部上的悬垂或凸出的量。沉积过程310可以执行至少一次(一个沉积循环),并且在一些实施例中,可以执行两次或更多次,例如多次(多个沉积循环)。在一些实施例中,沉积过程310可以使用用射频(rf)功率激活的反应气体。在一些实施例中,rf功率具有一定的相对高频率(将在下文更详细地描述)。

52.在蚀刻过程320中,可以蚀刻沉积的薄膜316,使得沟槽312的上表面326和图案314的顶部328可以比沟槽312的其余部分蚀刻得更多。在一些实施例中,形成在沟槽312的上表面326和图案314的顶部328上的薄膜可以比形成在沟槽312的中间表面324和沟槽312的下表面322上的薄膜蚀刻得更多。在一些实施例中,形成在沟槽312的上表面326和图案314的顶部328上的薄膜可以类似地或基本上以相同的量被蚀刻。在其他实施例中,形成在沟槽312的上表面326上的薄膜可以比形成在图案314的顶部328上的薄膜蚀刻得更多或更少。

53.下表面322可以包括沟槽312的底表面。上表面326、中间表面324和下表面322可以以多种不同的方式划分。作为非限制性示例,下表面322可以包括从沟槽312的底表面延伸到沟槽312的大约下三分之一的区域,上表面326可以包括沟槽312的约上三分之一,且中间表面324可以包括沟槽312的上表面326和下表面322之间的区域。

54.在一些实施例中,形成在沟槽312的中间表面324上的薄膜可以比形成在沟槽312的下表面上的薄膜蚀刻得更多。作为另一示例,形成在沟槽312的中间表面324和沟槽312的下表面322上的薄膜可以类似地被蚀刻。

55.在一些实施例中,可以执行蚀刻过程320,使得沉积的薄膜316通常可以从沟槽312的下表面322到沟槽312的上表面326和图案314的顶部328逐渐被更多地蚀刻。在其他实施例中,可以执行蚀刻过程320,使得沉积的薄膜316通常可以从沟槽312的中间表面324到沟槽312的上表面326和图案314的顶表面逐渐被更多地蚀刻。在其他实施例中,可以执行蚀刻过程320,使得被蚀刻的沉积薄膜316的量和/或程度在沟槽312的表面的不同部分中是不同的。

56.在一些实施例中,沟槽312可以划分为上半表面和下半表面(未示出)。在这些实施例中,形成在沟槽312的上半表面上的薄膜可以比形成在沟槽312的下半表面上的薄膜蚀刻得更多。

57.在一些实施例中,可以至少部分地基于施加到蚀刻剂的rf功率的强度和/或频率来控制蚀刻的量和/或程度。在一些实施例中,蚀刻过程320可以使用由具有一定相对较低频率的rf功率激活的蚀刻剂,以使形成在槽312的上表面326和图案314的顶部328上的薄膜比形成在沟槽312的其余部分上的薄膜被蚀刻得更多(如下文详细描述的)。在一些实施例中,示例间隙填充工艺300可以包括蚀刻过程320之前的单独的蚀刻剂激活过程。单独的蚀刻剂激活过程可以使用上述rf功率。蚀刻过程320可以执行至少一次(一个蚀刻循环),例如,执行多次(多个蚀刻循环)。在一些实施例中,可能不需要在每个循环中都提供/应用蚀刻剂和/或施加到蚀刻剂的rf功率。相对于每个蚀刻工艺320,可以重复多次沉积过程310。例如,蚀刻过程可以在整个工艺中以一定间隔进行,或者以与沉积循环成一定比例的方式进行。

58.可以重复n次沉积过程310和蚀刻过程320,直到沟槽312被薄膜316填充,并且图案314的顶部328被薄膜316覆盖,该薄膜316具有基本均匀的厚度,如过程330所示。根据一些实施例,基本上没有空隙和/或接缝的薄膜316可以沉积在沟槽312和图案314的顶部中。

59.图4示出了根据一些实施例的在半导体制造工艺中填充半导体图案中的间隙的示例方法400。尽管本文中参考特定顺序描述了方法400,但是在各种实施例中,本文中的步骤可以以不同的顺序执行或被省略,并且可以添加附加的步骤。例如,激活反应气体的步骤可以在沉积过程之前,和/或激活蚀刻剂的步骤可以在蚀刻过程之前。这可以适用于图5、14和16所示的方法500、1400和1600。

60.在步骤410中,可以将半导体衬底加载到反应器(未示出)的反应空间上。例如,可以将衬底加载到反应器内部的基座或加热块上。衬底可以包括半导体图案,其包括诸如沟槽/孔的3d结构。在一些实施例中,衬底可以包括沟槽,其长宽比可以至少为约20:1,例如约20:1至约80:1,例如约30:1至约80:1(在下文中与高长宽比可互换地使用)。长宽比的这些范围仅是示例,并且可以包括约20:1至约80:1之间的任意范围的值。另外,长宽比还可以包括小于约20:1或大于约80:1的比率。

61.在步骤420中,薄膜可以沉积在包括高长宽比沟槽的衬底的图案上(沉积过程)。在一些实施例中,薄膜可以包括sio2。也可以形成其他类型的薄膜。在使用sio2薄膜时,源气体(si前体)可以包括氨基硅烷、碘硅烷或卤化物类型的si前体。例如,si前体可以包括以下中的一个或多个:dipas,sih3n(ipr)2;tsa,(sih3)3n;dso,(sih3)2;dsma,(sih3)2nme;dsea,(sih3)2net;dsipa,(sih3)2n(ipr);dstba,(sih3)2n(tbu);deas,sih3net2;dtbas,sih3n(tbu)2;bdeas,sih2(net2)2;bdmas,sih2(nme2)2;btbas,sih2(nhtbu)2;bits,sih2(nhsime3)2;teos,si(oet)4;sicl4;hcd,si2cl6;3dmas,sih(n(me)2)3;bemas,si h2[n(et)(me)]2;ahead,si2(nhet)6;teas,si(nhet)4;si3h8;dcs,sih2cl2;sihi3;或sih2i2。

[0062]

沉积过程420可以使用反应气体来形成薄膜。反应气体可以包括氧气。例如,反应气体可以包括o2、o3、h2o、no2、n2o,或其组合。

[0063]

在沉积过程420中,反应气体可以用具有第一频率的第一rf功率激活。第一频率可以在约100khz至约3,000mhz的范围内,例如,约100khz,约500khz,约1,000khz,约5mhz,约50mhz,约500mhz,约1,000mhz,约2,000mhz或约3,000mhz,或其之间的任何值范围。在一些实施例中,第一频率可以在约27.12mhz至约100mhz的范围内。在其他实施例中,第一频率可以为约27.12mhz。第一频率的这些范围可以仅是示例,且可以包括小于约100khz或大于约

3,000mhz的频率。

[0064]

第一rf功率可以在约100瓦至约20,000瓦的范围内,例如,约100瓦、约500瓦、约1,000瓦、约5,000瓦、约10,000瓦或约20,000瓦,或其之间的任何值范围。在一些实施例中,可以用在约500瓦至约3,000瓦的范围内的第一rf功率获得更有效的沉积(例如,薄膜的更均匀的沉积)。第一rf功率的这些范围仅是示例,并且还可以包括小于约100瓦或大于约20,000瓦的rf功率。

[0065]

在执行蚀刻过程430之前,沉积过程420可以具有至少一个沉积循环。随着长宽比变大,即沟槽的深度变大,而沟槽的宽度变小,沉积循环数可以增加。例如,当沟槽的长宽比至少为约20:1,且宽度至少为约200nm时,可以在沉积过程420内使用约1

‑

10个沉积循环。作为另一示例,在相同的长宽比中,对于在约150至约200nm的范围内的沟槽的宽度,可以在沉积过程420内使用约1

‑

20个沉积循环,对于在约100nm至约150nm的范围内的沟槽的宽度,可以在沉积过程420内使用约1

‑

30个沉积循环,对于小于约100nm的沟槽的宽度,可以在沉积过程420内使用约1

‑

40个沉积循环。这些数量的沉积循环仅是示例,也可以使用其他数量的沉积循环。

[0066]

在步骤430中,可以用激活的蚀刻剂来蚀刻沉积的薄膜(蚀刻过程)。在一些实施例中,蚀刻剂可以包括氟。例如,蚀刻剂可以包括nf3、clf3、f2、sf6、cf4,或其组合。这些仅是示例,且也可以使用其他蚀刻剂来进行薄膜蚀刻。蚀刻剂可以利用具有第二频率的第二rf功率被激活成等离子体气体。在一些实施例中,当施加具有第二频率的第二rf功率时,可以在反应空间中在图案上原位地激活蚀刻剂。在其他实施例中,可以在反应空间外部用第二rf功率激活蚀刻剂,且可以将激活的蚀刻剂提供给反应空间。第二rf功率可以小于第一rf功率(将更详细地描述)。第二频率可以小于第一频率(将更详细地描述)。

[0067]

在一些实施例中,第二频率可以在约3khz至约13,560khz的范围内,例如,约3khz,约30khz,约100khz,约500khz,约1,000khz,约5,000khz,约10,000khz或约13,560khz,或其之间的任何值范围。在一些实施例中,可以用约100khz至约5,000khz的范围内的第二频率获得更有效的蚀刻。在其他实施例中,可以用约430khz的第二频率获得甚至更有效的蚀刻。然而,第一频率的这些范围仅是示例,且还可以包括小于约3khz或大于约13,560khz的频率。

[0068]

第二rf功率可以在约100瓦至约500瓦的范围内,例如约100瓦、约200瓦、约300瓦、约400瓦或约500瓦,或其之间的任何值范围。在一些实施例中,可以用约300瓦的第二rf功率获得更有效的蚀刻。然而,第二rf功率的这些范围仅是示例,且还可以包括小于约100瓦或大于约500瓦的rf功率。

[0069]

沉积过程420和蚀刻过程430可以执行n次(n是自然数),直到沟槽被薄膜填充(步骤440)。如上所述,重复的次数可以根据以下各项中的一个或多个来变化:反应气体的类型、蚀刻剂的类型、第一和第二rf功率的强度、第一和第二频率的强度、长宽比的大小、沟槽的宽度,或其他处理参数,包括但不限于,温度、压力、源/反应气体流速、或每单位循环的处理时间,等等。

[0070]

沉积的薄膜可以基本上没有空隙和/或接缝。在一些实施例中,当空隙/接缝的体积与整个薄膜的体积的比率在约0.001至约0.005的范围内或小于该范围时,沉积的薄膜可以视为基本上没有空隙和/或接缝。在确定薄膜是否基本上没有空隙和/或接缝时,可以使

用透射电子显微镜(tem)分析装置。也可以使用其他设备来确定空隙/接缝。

[0071]

图5示出了根据一些实施例的在半导体制造工艺中填充半导体图案中的间隙的另一示例方法500。在步骤510中,可以在衬底上形成具有高长宽比沟槽/孔的半导体图案。如上所述,在一些实施例中,高长宽比可以至少为约20:1。

[0072]

在步骤520中,可以使用用具有第一频率的第一rf功率激活的反应气体将薄膜沉积在包括半导体图案的衬底上(沉积过程)。反应气体可以包括但不限于o2、o3、h2o、no2、n2o,或其组合。第一频率可以在约100khz至约3,000mhz的范围内。第一rf功率可以在约100瓦至约20,000瓦的范围内。

[0073]

在步骤530中,可以使用用具有低于第一频率的第二rf频率的第二rf功率激活的蚀刻剂蚀刻沉积的薄膜(蚀刻过程)。蚀刻剂可以包括但不限于nf3、clf3、f2、sf6、cf4,或其组合。第二频率可以在约3khz至约13,560khz的范围内。第二rf功率可以在约100瓦至约500瓦的范围内。

[0074]

在步骤540中,可以重复沉积过程(步骤520)和蚀刻过程(步骤530)的循环,例如n次(n是自然数),直到沟槽和/或孔被薄膜填充。重复次数可以根据上述处理参数和条件中的一个或多个而变化。tem分析装置可以用于确定沟槽/孔是否被基本上没有空隙和/或接缝的薄膜填充。

[0075]

图6示出了根据一些实施例的间隙填充方法的工艺序列600。图6所示的工艺序列可以用于填充图案化的半导体衬底中的结构中的间隙。在一些实施例中,结构的长宽比可以为约20:1或更大。在一些实施例中,peald可以用于在工艺序列600中形成sio2的薄膜。然而,也可以使用长宽比、沉积方法和薄膜类型等的其他组合。工艺序列600可以包括沉积过程(s1

‑

s4)和蚀刻过程(s5

‑

s7)。图6仅是沉积和蚀刻的示例顺序,并且可以省略一个或多个步骤,可以添加附加步骤,或者可以将至少两个步骤组合为单个步骤。整个序列600可以重复x个循环(x是自然数)。

[0076]

沉积过程

[0077]

在每个循环中,沉积过程(s1

‑

s4)可以执行m个循环(其中m是自然数)。例如,沉积过程(s1

‑

s4)可以执行至少一次。为了方便起见,沉积过程(s1

‑

s4)被示出为用于沉积sio2,使用si前体作为源气体,o2作为反应气体,ar作为载气,其可以从反应空间中清除剩余的气体。但是,也可以使用源气体、反应气体或载气的其他组合。可以仅在步骤s1中提供源气体。可以在整个步骤s1

‑

s4中连续地提供反应气体。可以在整个沉积过程(s1

‑

s4)和蚀刻过程(s5

‑

s7)中连续地提供载气。

[0078]

沉积过程(s1

‑

s4)可以在约20℃至约600℃的范围内的温度下执行,例如约20℃至约30℃,约20℃至约100℃,约50℃至约600℃,或约400℃至约550℃。沉积过程(s1

‑

s4)可以在约1torr至约5torr的范围内的压力下执行,例如约3torr。在沉积过程(s1

‑

s4)期间,可以以在约2,000sccm至约4,000sccm的范围内的气体流速(例如,约3,000sccm),将反应气体(o2)提供给反应室。

[0079]

沉积过程可以包括源气体馈送步骤(s1)、源气体清除步骤(s2)、sio2层形成步骤(s3)和反应气体清除步骤(s4)。在源气体馈送步骤(s1)中,可以提供源气体。例如,可以在衬底上提供si前体蒸气和载气(ar),以使si前体吸附在衬底表面上,例如在诸如沟槽或孔的结构或特征的表面上。在源气体馈送步骤(s1)期间,可以以在约500sccm至约1,500sccm

的范围内的气体流速(例如,约1,000sccm),将载气(ar)提供给反应室。每单位循环的源气体馈送步骤(s2)的处理时间可以在约0.1秒至约0.5秒的范围内,例如约0.3秒。

[0080]

在源气体清除步骤(s2)中,可以使用载气(ar)清除吸附(例如,物理吸附)到衬底中的si蒸汽和/或过量的源气体。在源气体清除步骤(s2)和反应气体清除步骤(s4)期间,可以以在500sccm至约1,000sccm的范围内的气体流速(例如,约700sccm),将载气(ar)提供给反应室。每单位循环的源气体清除步骤(s2)的处理时间可以在约0.1秒至约0.5秒的范围内,例如约0.3秒。

[0081]

在sio2层形成步骤(s3)中,反应气体(o2)可以被提供到衬底,同时具有第一频率的第一rf功率被施加到反应气体以激活反应气体。第一rf功率可以在约300瓦至约2,000瓦的范围内,例如,约950瓦。第一频率可以在约13.56mhz至约100mhz的范围内,例如,约27.12mhz。激活的o2可以与si蒸汽化学反应以形成sio2的单层。每单位循环的sio2层形成步骤(s3)的处理时间可以在约0.1秒至约0.5秒的范围内,例如约0.3秒。

[0082]

当将具有第一频率的第一rf功率施加到反应气体(o2)时,氧自由基(o自由基)的量和/或密度可以增加(例如,与施加到反应气体的低频率相比),使得更大量的氧自由基可以与si蒸汽反应,从而在沟槽中形成基本上均匀的sio2层。例如,上述的第一频率可以在特征或结构中实现期望的沉积均匀性。尽管氧气被描述为反应气体,所述技术不限于氧气,而是可以应用于其他反应气体及其自由基。该操作在下面更详细地描述。

[0083]

图7a和7b是示出了根据一些实施例的频率与在间隙填充方法的沉积过程期间生成的氧自由基的量之间的关系的示例图示。

[0084]

图7a示出了根据比较例的沉积过程710,其中具有例如约430khz的低频率的rf功率被施加至反应气体(o2)。在沉积过程710期间,源气体(si前体)被沉积到图案714和沟槽712上,同时使用电极718将低频率rf功率施加到反应气体(o2)以激活反应气体(o2)。结果,生成氧自由基716并且这些自由基716与si蒸汽反应以在图案714上形成sio2层(薄膜)。然而,由于低频率rf功率,产生的氧自由基716少得多,导致与沟槽712的上表面717相比,较少量的sio2层形成在沟槽712的下表面713和中间表面715中(图7a)。也就是说,sio2层随着从沟槽712的下表面713移动到上表面717而变厚。

[0085]

图7b示出了根据一些实施例的沉积过程720,其中具有诸如约27.12mhz的高频率的rf功率被施加到反应气体(o2)。图7b示出了高频率的使用可以改善等离子体气体(即,反应气体自由基)向诸如沟槽/孔之类的结构中的渗透,从而在整个结构中获得更均匀的沉积。在沉积过程720期间,源气体(si前体)被沉积到图案714和沟槽712上,同时使用电极728将低频率rf功率施加到反应气体(o2)以激活反应气体(o2)。结果,生成氧自由基730并且这些自由基730与si蒸汽反应以在图案734上形成sio2层(薄膜)。由于高频率rf功率,生成了明显更多的氧自由基730,并且这些更多的氧自由基730与si蒸汽反应,从而在沟槽732的下表面722、中间表面724和上表面726中形成基本上均匀的sio2层。也就是说,sio2层的厚度在沟槽732的整个表面上基本上相似或相同。在一些实施例中,至少在沟槽732的下表面和中间表面中的sio2层的厚度在沉积过程720中比在沉积过程710中至少大约5%

‑

约10%。这里,27.12mhz仅是高频率的示例,例如在上述约13.56mhz至约100mhz范围内的其他高频率,也可以达到类似的效果。

[0086]

图8是示出了根据一些实施例的频率与在沉积过程期间生成的氧自由基的量之间

的关系的另一示例图示。尽管图8中示出了氧自由基,但它也可以应用于其他反应气体自由基。参考图8,当在薄膜沉积过程期间使用例如约430khz的低频率820时,可以生成少得多的量的氧自由基,导致在例如上文参考图7a所述的沟槽的特征或结构上形成不均匀的sio2层。与之相比,当使用诸如13.56mhz的高频率810时,会产生明显更大量的氧自由基,从而导致在上文参考图7b所述的沟槽的表面中形成基本上均匀的sio2层。同样,13.56mhz仅是高频率的示例,例如在上述约13.56mhz至约100mhz范围内的其他高频率,也可以达到类似的效果。

[0087]

回来参考图6,在反应气体清除步骤(s4)中,可以清除尚未与源气体反应的剩余的反应气体。在一些实施例中,在反应气体清除步骤(s4)期间,可以以在约500sccm至约1,000sccm的范围内的气体流速(例如,约700sccm),将载气(ar)提供给反应室。每单位循环的反应气体清除步骤(s4)的处理时间可以在约0.1秒至约0.5秒的范围内,例如约0.2秒。s1

‑

s4的循环可以重复至少一次(例如,m个循环,m是自然数)。

[0088]

表1总结了可以用于执行沉积过程(s1

‑

s4)的示例处理参数或条件。同样,上述参数和条件以及表1所示的参数和条件仅是示例,还可以使用其他数字或值。

[0089]

表1

‑

图6的沉积过程(s1至s4)的工艺条件

[0090][0091]

蚀刻过程

[0092]

蚀刻过程(s5

‑

s7)可以执行n个循环(其中n是自然数)。例如,蚀刻过程(s5

‑

s7)可以执行至少一次。为了方便起见,蚀刻过程(s5

‑

s7)可以使用nf3作为蚀刻剂和ar作为载气。

然而,也可以使用蚀刻剂和载气的其他组合。例如,也可以使用其他蚀刻剂,例如clf3、sf6、cf4或f2,或者其他含氟或不含氟的蚀刻剂。可以仅在步骤s6中提供蚀刻剂。可以在整个蚀刻过程(s5

‑

s7)中连续地提供载气。

[0093]

蚀刻过程(s5

‑

s7)可以在约50℃至约600℃的范围内的温度下执行,例如,约400℃至约550℃。蚀刻过程(s5

‑

s7)可以在约1torr至约5torr的范围内的压力下执行,例如约2torr。

[0094]

蚀刻过程(s5

‑

s7)可以包括剩余气体清除步骤(s5)、蚀刻步骤(s6)和剩余蚀刻剂/经蚀刻的薄膜清除步骤(s7)。在剩余气体清除步骤(s5)中,可以清除在沉积过程(s1

‑

s4)期间未反应的剩余气体。在剩余气体清除步骤(s5)期间,可以以在约5,000sccm至约10,000sccm的范围内的气体流速(例如,约7,000sccm),将载气(ar)提供给反应室。每单位循环的剩余气体清除步骤(s5)的处理时间可以在约0.1秒至约10.0秒的范围内,例如约6.0秒。

[0095]

在蚀刻步骤(s6)中,可以用被具有第二频率的第二rf功率激活的蚀刻剂来蚀刻沉积的sio2层的薄膜。蚀刻剂可以包括氟。例如,蚀刻剂可以包括nf3、clf3、f2、sf6、cf4中的至少一个,或其组合。在一些实施例中,sf6或cf4中的至少一个可以用于蚀刻形成在沟槽中的薄膜,该沟槽的长宽比至少约为约20:1,沟槽宽度约为200nm,以获得改进的蚀刻效果。nf3可以用于蚀刻步骤(s6)。第二rf功率可以在约100瓦至约500瓦的范围内,例如,约300瓦。第二频率可以在约3khz至约13,560khz的范围内,例如,约100khz至约5,000khz。

[0096]

在蚀刻步骤(s6)期间,可以以在约200sccm至约1,000sccm的范围内的气体流速(例如,约300sccm),将蚀刻剂提供给反应室。每单位循环的蚀刻步骤(s6)的处理时间可以在约5.0秒至约15.0秒的范围内,例如约11.0秒。

[0097]

将参考图9a

‑

12更详细地描述蚀刻步骤(s6)。当具有第二频率的第二rf功率被施加到蚀刻剂(nf3)时,可以增加氟自由基(f自由基)的离子轰击效应,使得可以在沟槽的上表面上比在沟槽的下表面上实现更多的蚀刻。参考图9a

‑

10c更详细地描述此操作。

[0098]

图9a和9b是示出了根据一些实施例的频率与蚀刻过程期间的离子轰击效应的量之间的关系的示例图示。

[0099]

图9b示出了根据比较例的蚀刻过程920,其中具有例如约27.12mhz的高频率的rf功率被施加到蚀刻剂。在蚀刻过程920期间,蚀刻剂(nf3)被施加到沉积的薄膜930,同时通过电极928将具有高频率(27.12mhz)的rf功率施加到蚀刻剂(nf3)以激活蚀刻剂。由于高频率生成更多的氟自由基(f自由基)926,从而使沟槽932被所生成的f自由基926饱和。然而,由于高频率的较短波长,所生成的f自由基926具有相对较低的能量。在这种情况下,形成在沟槽932的上表面924(例如,上半部)上的薄膜比沟槽932的其余部分和图案934的顶部936上的薄膜蚀刻得更多,这是因为沟槽932的上表面上的薄膜比沟槽的其他部分上的薄膜形成得更弱(即,与其他部分相比,可以通过蚀刻更容易地移除)。结果,形成在图案934的顶部936上的薄膜比形成在沟槽932的上表面924上的薄膜被蚀刻得较少。即,sio2层从沟槽932的上表面924到图案934的顶部936变得更厚。

[0100]

图9a示出了根据一些实施例的蚀刻过程910,其中具有例如约430khz的低频率的rf功率被施加到蚀刻剂。在蚀刻过程910期间,蚀刻剂(nf3)被施加到沉积的薄膜917,同时通过电极918将具有低频率(例如,约430khz)的rf功率施加到蚀刻剂(nf3)以激活蚀刻剂。尽管由于低频率而生成的氟自由基(f自由基)916较少,但由于低频的波长较长,所生成的f

自由基916可以具有相对较强的能量。在这种情况下,更多的高能f自由基会主动与薄膜碰撞,特别地与在图案914的顶部919上形成的薄膜(离子轰击效应增大),而较少的高能f自由基与沟槽912的其余部分上的薄膜917碰撞。结果,形成在图案914的顶部919上的薄膜比形成在沟槽912上的薄膜917蚀刻得更多。例如,随着薄膜从图案914的顶部919移动到沟槽912的上表面和下表面,可以逐渐对薄膜进行更多的蚀刻。也就是说,sio2层可以随着从沟槽912的下表面移动到图案914的上表面而变得更薄。这里,430khz仅是低频率的示例,例如在上述约13.56mhz至约13,560khz范围内的其他低频率,也可以达到类似的效果。

[0101]

图10a、10b和10c是示出了根据一些实施例的频率与蚀刻过程期间的离子轰击效应的量之间的关系的示例图示。在图10a中,场蚀刻量意味着被蚀刻的场部分(形成在图案的顶部上的薄膜)的量。图10a示出了随着蚀刻频率减小,场蚀刻量增加。例如,当将约430khz的频率施加到蚀刻剂时,场部分被蚀刻约而当将约27.12mhz的频率施加到蚀刻剂时,场部分被蚀刻约

[0102]

参考图10b,根据一些实施例,当以低频率(430khz)激活的蚀刻剂蚀刻图案的场部分上的原始厚度为约(蚀刻前厚度)的薄膜时,蚀刻约使得在蚀刻之后,留下约的场部分(蚀刻后厚度)(另参见图11a的左上角的“13”(nm))。

[0103]

参考图10c,根据比较例,当以高频率(例如约27.12mhz)激活的蚀刻剂蚀刻图案的场部分上的原始厚度为约的薄膜时,蚀刻约使得场部分的蚀刻后厚度为约(另参见图11b的左上角的“29nm”)。

[0104]

图11a是示出根据一些实施例的在图案的不同部分处的蚀刻速率的图示。图11b是示出根据比较例的在图案的不同部分处的蚀刻速率的图示。图12是示出根据一些实施例和根据比较例的在图案的不同部分处的不同蚀刻速率的比较图。

[0105]

参考图11a和12,当使用以低频率(例如约430khz)激活的蚀刻剂时,图案的顶边缘1210上的薄膜(sio2)的剩余厚度为约13.4nm。与之相比,参考图11b和12,当使用以高频率(例如约27.12mhz)激活的蚀刻剂时,图案的顶边缘1210上的薄膜(sio2)的剩余厚度为约27.2nm。即,图案的顶边缘1210上的薄膜(sio2)在低频率下比在高频率下被蚀刻得更多。

[0106]

回来参考图11a和12,当使用以低频率(例如约430khz)激活的蚀刻剂时,形成在沟槽1212的上部(沟槽顶部)上的薄膜(sio2)的第一部分的1220的剩余厚度为约12.3nm。与之相比,回来参考图11b和12,当使用以高频率(例如约27.12mhz)激活的蚀刻剂时,薄膜(sio2)的第一部分1220的剩余厚度为约20.0nm。即,沟槽顶部在低频率下比在高频率下被蚀刻得更多。另外,当使用以低频率(例如约430khz)激活的蚀刻剂时,薄膜(sio2)的第一部分1220可以比形成在沟槽1212的其余表面上的薄膜的第二部分(包括但不限于第三部分1230和第四部分1240;未标记的)蚀刻得更多。

[0107]

当使用以低频率(例如约430khz)激活的蚀刻剂时,形成在沟槽1212的中部(沟槽中部)上的薄膜(sio2)的第三部分的1230的剩余厚度为约15.2nm。与之相比,当使用以高频率(例如约27.12mhz)激活的蚀刻剂时,形成在沟槽中部上的薄膜(sio2)的第三部分1230的剩余厚度为约18.6nm。即,沟槽中部在低频率下比在高频率下被蚀刻得更多。

[0108]

当使用以低频率(例如约430khz)激活的蚀刻剂时,形成在沟槽1212的中下部(沟槽中下部)上的薄膜(sio2)的第四部分的1240的剩余厚度为约17.7nm。与之相比,当使用以

高频率(27.12mhz)激活的蚀刻剂时,沟槽中下部上的薄膜(sio2)的第四部分1240的剩余厚度为约23.3nm。即,沟槽中下部在低频率下比在高频率下被蚀刻得明显更多。另外,当使用以低频率(例如约430khz)激活的蚀刻剂时,薄膜(sio2)的第三部分1230(沟槽中部)可以比薄膜(sio2)的第四部分1240(沟槽中下部)蚀刻得更多。

[0109]

图案1214可以包括形成在图案1214的顶部上的薄膜(sio2)的第五部分1216。第五部分1216可以包括形成在图案1214的顶部的边缘上的薄膜(sio2)的第六部分1210和形成在图案1214的其余顶部上的薄膜(sio2)的第七部分1217(即,第五部分1216不包括第六部分1210)。薄膜(sio2)的第六部分1210可以比薄膜(sio2)的第七部分1217蚀刻得较少。第一部分1220、第六部分1210和第七部分1217以用低频率激活的蚀刻剂比以用高频率激活的蚀刻剂显著蚀刻得更多。另外,这三个上部1217、1210和1220上的其余sio2膜的厚度分别为约13nm、约13.4nm和约12.3nm,它们比比较例(约29nm、约27.2nm和约20.0nm)基本上均匀地更薄(参见图11a和图11b)。

[0110]

回来参考图6中的蚀刻过程的清除步骤(s7),剩余的蚀刻剂气体和从薄膜蚀刻的材料可以用载气(ar)清除。每单位循环的清除步骤(s7)的处理时间可以在约2.0秒至约10.0秒的范围内,例如约6.0秒。在清除步骤(s7)期间,可以以在约5,000sccm至约10,000sccm的范围内的气体流速(例如,约7000sccm),继续将载气(ar)提供给反应室。s5

‑

s7的循环可以重复至少一次,例如,n个循环且n是自然数。沉积循环的数量(m)和蚀刻循环的数量(n)的总和可以是x(m+n=x)。

[0111]

表2总结了用于执行蚀刻过程(s5

‑

s7)的示例处理参数和条件。同样,上述参数和条件以及表2所示的参数和条件仅是示例,还可以使用其他数字或值。

[0112]

表2

‑

图6的蚀刻步骤(s5至s7)的工艺条件

[0113][0114][0115]

图13a示出了根据一些实施例的填充在间隙中的无接缝薄膜1310。图13a中所示的薄膜可以通过重复基于高频率的沉积过程和基于低频率的蚀刻过程来制备。如上所述,根

据基于低频率的蚀刻过程,薄膜的上部可以比薄膜的中部和下部蚀刻得更多。即,沟槽的宽度随着从下部移动到上部变得更宽。通过重复沉积过程和蚀刻过程,沟槽的中部和下部可以首先被薄膜填充,然后填充沟槽的上部,使得可以形成基本上没有空隙/接缝的薄膜,如图13a所示。

[0116]

图13b示出了根据比较例的在其中具有接缝1322的薄膜1320。图13b中所示的薄膜可以通过重复基于低频率的沉积过程和基于高频率的蚀刻过程来制备。如上所述,根据基于高频率的蚀刻过程,薄膜的中部壁薄膜的上部和下部蚀刻得更多。即,沟槽的宽度在沟槽的中部最宽。通过重复沉积过程和蚀刻过程,沟槽的上部首先被薄膜填充,且沟槽的间隙从顶部闭合,使得在沟槽的中部中形成一些空隙和/或接缝,如图13b所示。

[0117]

图14示出了根据一些实施例的在半导体制造工艺中填充半导体图案中的间隙的另一示例方法1400。在步骤1410中,可以在衬底上形成具有高长宽比沟槽/孔的半导体图案。如上所述,高长宽比可以至少为约20:1。

[0118]

在步骤1420中,可以通过气相沉积工艺(例如ald、peald或pecvd)使用一种或多种气相反应物来沉积薄膜。例如,可以使用反应气体将薄膜沉积在包括半导体图案的衬底上(沉积过程)。反应气体可以包括一种或多种反应气体。在一些实施例中,反应气体可以用具有第一频率的第一rf功率或具有第二频率的第二rf功率激活。反应气体可以包括但不限于o2、o3、h2o、no2、n2o,或其组合。第一频率可以在约100khz至约3,000mhz的范围内。第一rf功率可以在约100瓦至约20,000瓦的范围内。第二频率可以在约3khz至约13,560khz的范围内。第二rf功率可以在约100瓦至约500瓦的范围内。在其他实施例中,反应气体可以用第三rf功率激活,例如,高于第一rf功率或低于第二rf功率。第三rf功率的频率可以高于第一频率或低于第二频率。图14的方法1400与图5的方法500之间的主要区别在于,图5中的沉积过程用具有第一频率的第一rf功率来执行,该第一频率高于用于激活蚀刻剂的第二频率,而图14中的沉积过程可以用具有可激活反应气体的任何合适的频率的任何合适的rf功率来执行。即,用于在图14中的沉积过程中激活反应气体的频率不必高于用于激活蚀刻剂的频率。

[0119]

在步骤1430中,可以使用以具有低频率的低rf功率激活的蚀刻剂来蚀刻沉积的薄膜(蚀刻过程)。低rf功率可以在约100瓦至约500瓦的范围内。低频率可以与上述第二频率相同,即,在约3khz至约13,560khz的范围内。蚀刻剂可以包括但不限于nf3、clf3、f2、sf6、cf4,或其组合。

[0120]

在步骤1440中,可以重复沉积过程(步骤1420)和蚀刻过程(步骤1430)的循环,例如n次(n是自然数),直到沟槽和/或孔被薄膜填充。重复次数可以根据上述处理参数和/或条件中的一个或多个而变化。

[0121]

图15示出了根据一些实施例的在半导体制造工艺中填充具有负斜率的沟槽的半导体图案中的间隙的示例过程1500。图16示出了根据一些实施例的填充具有图15的负斜率的沟槽的半导体图案中的间隙的示例方法1600。参考图15,半导体图案1512可以具有负斜率的沟槽1514,其在顶部比在上部和中部具有较小的宽度。负斜率的沟槽1514可以被基本上没有空隙和/或接缝的薄膜1522填充。

[0122]

将参考图15描述图16的间隙填充方法1600。在1610中,可以将包括具有负斜率的沟槽1514的半导体图案1512的衬底1510设置在反应器(未示出)上。例如,可以将衬底放置

在反应器内的基座或加热块上(参见图15中的“(a)”)。

[0123]

在步骤1620中,通过在半导体图案1512上沉积薄膜1522时提供沉积抑制剂,可以将负斜率的沟槽1514转变为正斜率的沟槽1520(参见图15中的“(b)”)。在一些实施例中,沉积抑制剂和薄膜可以同时或基本上同时提供。在其他实施例中,提供沉积抑制剂的时间和提供薄膜的时间可以至少部分地彼此重叠。沉积抑制剂可以抑制或减少在沟槽1514的顶部上的薄膜沉积,使得薄膜在顶部的沉积少于沟槽1514的其余部分。在一些实施例中,可以在将薄膜沉积到图案1512上时,将沉积抑制剂提供给图案1512。沉积抑制剂可以例如包括n2(氮)抑制剂。n2抑制剂具有出色的自下而上间隙填充特性。也可以使用具有出色的自下而上间隙填充特性的其他沉积抑制剂,例如乙酰丙酮或聚合物。薄膜可以包括sio2。

[0124]

图15中的步骤(b)可以重复x次(x个循环,且x是自然数),直到负斜率的沟槽1514被转换成正斜率的沟槽1520(参见图15中的“(b)”)。负斜率的沟槽1514向正斜率的沟槽1520的转换在间隙填充工艺中可以是有利的,因为与负斜率的沟槽1514相比,可以在正斜率的沟槽1520中形成基本上没有空隙和/或接缝的薄膜。例如,当将薄膜沉积在负斜率的沟槽中时,会生成更多的空隙和/或接缝。沉积过程可以使用以上述任何合适的频率的rf功率激活的反应气体。

[0125]

在步骤1630中,通过使用以具有第一蚀刻频率的第一蚀刻rf功率激活的蚀刻剂来蚀刻沉积的薄膜,可以加宽正斜率的沟槽1520的顶部(参见图15中的“(c)”)。在一些实施例中,第一蚀刻频率可以是低频率。在一些实施例中,第一蚀刻频率在约3khz至约13,560khz的范围内。在一些实施例中,第一蚀刻频率在约100khz至约5,000khz的范围内。在一些实施例中,第一蚀刻rf功率在约100瓦至约500瓦的范围内。蚀刻剂可以包括但不限于nf3、clf3、f2、sf6、cf4,或其组合。

[0126]

在步骤1640中,使用以具有沉积频率的沉积rf功率激活的反应气体,可以将薄膜沉积在顶部加宽的沟槽1530上。由于沟槽具有加宽的顶部,如上所述,在填充顶部之前,可以将薄膜填充在沟槽1530的底部和中部上。以此方式,可以在沟槽1530中形成基本上没有空隙和/或接缝的薄膜。反应气体可以被可激活反应气体的任何频率的rf功率激活。沉积频率可以是可激活反应气体的任何频率。在一些实施例中,沉积频率低于第一蚀刻频率。在一些实施例中,沉积频率高于第一蚀刻频率。在一些实施例中,沉积频率与第一蚀刻频率相同。在一些实施例中,沉积频率可以是高频率。在一些实施例中,沉积频率可以是低频率。反应气体可以包括但不限于o2、o3、h2o、no2、n2o,或其组合。

[0127]

在步骤1650中,可以使用以具有第二蚀刻频率的第二蚀刻rf功率(或低频率rf功率)激活的蚀刻剂来蚀刻沉积的薄膜。在一些实施例中,第二蚀刻频率可以是低频率。在一些实施例中,第二蚀刻频率可以与步骤1630中的第一蚀刻频率相同。在一些实施例中,第二蚀刻频率可以与步骤1630中的第一蚀刻频率不同。在一些实施例中,第二蚀刻频率在约3khz至约13,560khz的范围内。在一些实施例中,第二蚀刻频率在约100khz至约5,000khz的范围内。在一些实施例中,第二蚀刻rf功率在约100瓦至约500瓦的范围内。如上所述,以低频率rf功率激活的蚀刻剂可以在沟槽的上表面上比在沟槽的中间表面和下表面上更多的蚀刻薄膜,使得薄膜可以在填充沟槽的顶表面之前填充在沟槽的底表面和中间表面上。同样,低频率蚀刻和沉积(通过高频率或低频率rf功率)的组合可以更高效地在沟槽1530中形成基本上没有空隙和/或接缝的薄膜。在步骤1660中,可以重复步骤1640和步骤1650的循

环,直到沟槽1530被薄膜填充(参见图15中的“(d)”)。

[0128]

其他变型

[0129]

在一些实施例中,也可以在不对沉积过程使用高频率rf功率的情况下生成大量的反应气体自由基。例如,o2可以在高温环境(例如,约700℃)中用作反应气体,而无需在沉积过程中施加高频率rf功率。此外,o3可以用作反应气体而不产生等离子气体(例如,o2+高频率rf功率)。

[0130]

在一些实施例中,可以在蚀刻过程中不使用低频率的rf功率的情况下,实现增加的离子轰击效应。例如,在蚀刻过程期间,可以在较低压力的环境中(例如,低于约1torr的压力)使用蚀刻剂。较低的压力可使气体颗粒之间的平均自由程(mfp)更长,从而使较少量的蚀刻剂自由基(例如f自由基)与其他气体颗粒发生碰撞,从而导致离子轰击效应增加。

[0131]

结合特定方面、实施例或示例描述的特征、材料、特性或组应理解为可应用于本节或本说明书中其他地方描述的任何其他方面、实施例或示例,除非与其不兼容。在本说明书(包括任何所附权利要求、摘要和附图)中公开的所有特征,和/或如此公开的任何方法或工艺的所有步骤,可以以任何组合进行组合,除非组合中至少有一些这样的特征和/或步骤是互斥的。保护不限于任何前述实施例的细节。保护扩展到本说明书(包括任何所附权利要求、摘要和附图)中公开的的任何新颖特征的或特征的新颖组合,或如此公开的任何方法或过程的步骤中的任何新颖步骤或步骤的新颖组合。

[0132]

此外,在单独的实施方式的上下文中在本公开中描述的某些特征也可以在单个实施方式中组合实现。相反,在单个实施方式的上下文中描述的各种特征也可以在多个实施方式中单独地或以任何合适的子组合来实现。此外,尽管上面可以将特征描述为以某些组合形式起作用,但是在某些情况下,可以从该组合中删除一个或多个来自所要求保护的组合的特征,并且可以将所述组合声明为子组合或子组合的变体。

[0133]

此外,虽然可以以特定顺序在附图中描绘操作或在说明书中描述操作,但是不需要以所示的特定顺序或以相继次序执行这样的操作,或者不需要执行所有操作来获得期望的结果。未描绘或描述的其他操作可以包含在示例方法和工艺中。例如,可以在任何上述操作之前,之后,同时或之间执行一个或多个其他操作。此外,在其他实施方式中,可以对操作进行重新排列或重新排序。本领域技术人员将理解,在一些实施例中,在所示和/或所公开的工艺中采取的实际步骤可能与图中所示的步骤不同。根据实施例,可以删除上述某些步骤,也可以添加其他步骤。此外,以上公开的特定实施例的特征和属性可以以不同的方式组合以形成另外的实施例,所有这些都落入本公开的范围内。另外,上述实施方式中的各种系统部件的分离不应理解为在所有实施方式中都需要这样的分离,并且应当理解,所描述的部件和系统通常可以集成在单个产品中或包装成多个产品。例如,在此描述的用于能量存储系统的任何部件都可以分开提供,或集成在一起(例如,包装在一起,或附接在一起)以形成能量存储系统。

[0134]

为了本公开的目的,本文描述了某些方面、优点和新颖特征。根据任何特定实施例,不一定可以实现所有这些优点。因此,例如,本领域的技术人员将认识到,可以以实现本文所教导的一个优点或一组优点而不必实现本文所教导或建议的其他优点的方式来实施或实践本公开。

[0135]

除非另有明确说明,或者在所使用的上下文中以其他方式理解,条件语言,诸如

“

可以”、“可能”、“可”或“会”通常旨在表达某些实施例可以包括而其他实施例不包括某些特征、元件和/或步骤。因此,这种条件性语言通常不旨在暗示一个或多个实施例以任何方式要求特征、元件和/或步骤,或者一个或多个实施例必须在有或没有用户输入或提示的情况包含用于进行决定的逻辑,无论这些特征、元件和/或步骤是否包括任何特定实施例中或将在任何特定实施例中执行。

[0136]

除非另有说明,否则短语“x,y和z中的至少一个”等组合语言应按照通常用于表达项目、术语等可以是x,y或z的上下文来理解。因此,这种组合语言通常不旨在暗示某些实施例要求存在x中的至少一个,y中的至少一个和z中的至少一个。

[0137]

本文所用的程度语言,如本文所用的术语“约”、“大约”、“通常”和“基本上”,表示接近规定值、数额或特性的值、数额或特性,其仍可以执行所需的功能或达到所需的结果。

[0138]

本公开的范围不旨在由本部分或本说明书的其他部分中的实施例的具体公开来限制,并且可以由如本部分或本说明书的其他部分中或将来提出的权利要求书限定。权利要求的语言应基于权利要求书中使用的语言来广义地解释,并且不限于在本说明书中或在本技术进行过程中描述的示例,这些示例应解释为非排他性的。

[0139]

尽管已经描述了某些实施例,但是这些实施例仅是通过示例的方式给出的,并且不意图限制本公开的范围。实际上,本文描述的新颖的方法和系统可以以多种其他形式来体现。此外,在不脱离本公开的精神的情况下,可以对本文所述的系统和方法进行各种省略、替代和改变。所附权利要求及其等同物旨在覆盖将落入本公开的范围和精神内的这些形式或修改。因此,本发明的范围仅通过参照所附的权利要求书来限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1