垂直结构LED芯片的制造方法与流程

垂直结构led芯片的制造方法

技术领域

1.本发明属于半导体器件制造技术领域,更具体地,涉及一种垂直结构led芯片的制造方法。

背景技术:

2.垂直结构led芯片相比水平结构led芯片具有高亮度的优势。一方面,垂直结构led芯片是将外延层从绝缘和散热差的蓝宝石衬底转移到导电导热能力优异的键合衬底上,进而能承受更高的工作电流从而获得更高的亮度。另一方面,垂直结构led芯片更容易将出光表面进行微纳加工,进而降低外延层和空气界面的全反射来增加光提取效率。

3.在垂直结构led芯片的制造过程中,衬底转移技术是至关重要的步骤。目前的衬底转移技术中一般会采用共晶键合或热压键合方式。共晶键合工艺是利用具有合适共晶温度的二元或多元键合层实现外延层和键合衬底的粘结,键合层一般由导电性能良好和低熔点的金属组成。然而由于键合衬底和外延层之间存在显著的晶格常数差异和热膨胀系数差异,且部分键合层在制备过程中内部具有较严重的应力,容易导致垂直结构led晶圆发生翘曲现象。热压键合工艺主要采用金金键合工艺,由制造设备提供较大的键合压力。对于键合衬底为金属衬底的情况,由于金属衬底自身具有较高韧性,仅需要缓解翘曲问题即可,但对于键合衬底为硬脆性材料的硅衬底的情况,在衬底剥离过程或后续加工过程中,容易出现碎片现象,进而使得制造得到的垂直结构led芯片良率低、成本高。

技术实现要素:

4.本发明的目的在于提供一种垂直结构led芯片的制造方法,以避免在衬底转移过程中因键合造成的严重翘曲问题和晶圆碎片现象。

5.根据本发明提供的一种垂直结构led芯片的制造方法,包括:在第一晶圆表面形成第一键合层,所述第一晶圆包括第一衬底以及位于所述第一衬底表面的外延层;

6.在第二衬底表面形成第二键合层;

7.在所述第一键合层和/或第二键合层表面上形成第三键合层;

8.通过所述第一键合层、所述第二键合层以及所述第三键合层将所述第一晶圆与所述第二衬底键合在一起;

9.将所述第一衬底剥离;

10.其中,所述第一键合层、所述第二键合层为高熔点金属层,所述第三键合层为低熔点金属层。

11.可选地,采用液相瞬态键合工艺将所述第一晶圆与所述第二衬底键合在一起。

12.可选地,所述第一晶圆和所述第二衬底的键合环境为真空,键合温度比所述第三键合层的熔点温度高5℃~20℃,键合压力为5000kgf~15000kgf,键合时间不小于10分钟。

13.可选地,所述键合温度为160℃~260℃。

14.可选地,在第一晶圆表面形成第一键合层以及在第二衬底表面形成第二键合层的

步骤后,还包括:

15.对所述第一键合层和所述第二键合层进行快速退火处理以形成降低应力的所述第一键合层和降低应力的所述第二键合层。

16.可选地,所述快速退火处理的方法包括激光退火技术或者强光退火技术,所述退火处理的温度为400℃~800℃,所述退火处理的时间小于2分钟。

17.可选地,所述第二衬底为硅、铜、钼、钨、钼铜合金、钨铜合金、铝硅合金衬底中的一种,所述第一衬底为氧化镓、碳化硅、硅、蓝宝石、氧化锌、镓酸锂单晶衬底或耐高温金属衬底中的一种。

18.可选地,所述第一键合层为金、铜、镍单层或二元金属体系中的一种,所述第一键合层的厚度为200纳米~2微米。

19.可选地,所述第二键合层为金、铜、镍单层或二元金属体系中的一种,所述第二键合层的厚度为200纳米~2微米。

20.可选地,所述第三键合层为锡、铟单层或二元金属体系中的一种,所述第三键合层的厚度为100纳米~2微米。

21.可选地,在第一衬底表面形成外延层的步骤包括:

22.在所述第一衬底表面上形成依次堆叠的缓冲层、本征半导体层、第一半导体层、发光层、电子阻挡层以及第二半导体层。

23.可选地,还包括:

24.在所述第二半导体层表面依次形成第一欧姆接触层、反射镜层以形成所述第一晶圆;

25.在所述反射镜层和所述第二衬底表面分别形成金属阻挡层,

26.所述金属阻挡层分别位于所述第二衬底和所述第二键合层之间,以及位于所述反射镜层和所述第一键合层之间。

27.可选地,采用激光剥离、化学机械减薄、化学湿法腐蚀、干法刻蚀中的一种或多种工艺组合将所述第一衬底剥离。

28.可选地,将所述第一衬底剥离包括:

29.对所述缓冲层进行分解,采用化学湿法腐蚀技术将所述缓冲层分解后的产物去除,以露出所述本征半导体层。

30.可选地,还包括:

31.采用光刻工艺和刻蚀工艺依次刻蚀所述本征半导体层、所述第一半导体层、所述发光层、所述电子阻挡层、所述第二半导体层的边缘以形成暴露所述第一欧姆接触层的表面的第一台阶,所述第一台阶的侧壁与所述第一欧姆接触层的表面形成第一夹角;

32.在所述本征半导体层中形成开口并在所述开口中形成与所述第一半导体层接触的第一电极;

33.在所述第二衬底远离所述第二键合层的表面形成第二电极;以及

34.在所述本征半导体层的表面、所述第一台阶的侧壁和所述第一欧姆接触层的表面形成钝化层。

35.可选地,还包括:

36.对所述本征半导体层的表面进行粗化。

37.可选地,所述第一夹角为30

°

~60

°

。

38.可选地,还包括:

39.形成依次贯穿所述第二半导体层、所述电子阻挡层、所述发光层的通孔,所述通孔暴露所述第一半导体层的表面;

40.在所述通孔中形成与所述第一半导体层接触的第二欧姆接触层;

41.在所述第二半导体层表面依次形成第一欧姆接触层、反射镜层、金属阻挡层;

42.在所述金属阻挡层表面以及所述通孔中形成介质层,并在所述介质层中形成暴露所述第二欧姆接触层的开口,以形成所述第一晶圆;

43.在所述介质层表面形成所述第一键合层,在所述第二衬底表面形成所述第二键合层。

44.可选地,在所述第二衬底和所述第二键合层之间形成金属阻挡层。

45.可选地,将所述第一衬底剥离的步骤包括:

46.对所述第一衬底减薄并刻蚀以去除所述第一衬底以及所述缓冲层,露出所述本征半导体层的表面。

47.可选地,还包括:

48.对所述本征半导体层的表面进行粗化;

49.采用光刻工艺和刻蚀工艺依次刻蚀所述本征半导体层、所述第一半导体层、所述发光层、所述电子阻挡层、所述第二半导体层、所述第一欧姆接触层、所述反射镜层的边缘以形成暴露金属阻挡层表面的第二台阶;

50.在所述第二台阶的下表面形成与所述金属阻挡层接触的第二电极;

51.在所述本征半导体层表面以及所述第二台阶的侧壁形成钝化层;以及

52.对所述第二衬底远离所述第二键合层的表面减薄并形成第一电极。

53.根据本发明实施例提供的垂直结构led芯片的制造方法,在第一晶圆表面形成第一键合层,在第二衬底表面形成第二键合层,其中,第一键合层、第二键合层为高熔点金属层,采用快速热退火处理高熔点金属层使其释放其内部较严重的应力(即应力调整层),同时避免了常规高温退火对垂直结构led芯片中其他半导体结构的性能的影响。接着在第一键合层表面和/或第二键合层表面形成第三键合层,其中第三键合层为低熔点金属层,进而在较低温度环境下将第一晶圆(外延层)和第二衬底键合,以降低因材料晶格常数和热膨胀系统差异所导致的键合后晶圆翘曲严重的问题,提升工艺良率。

54.更进一步地,在真空且键合温度略高于第三键合层的熔点温度的环境下,并在一定键合压力下,采用低温键合工艺将第一晶圆和第二衬底键合,以防止因第三键合层在较高温下氧化造成制造得到的垂直结构led芯片良率下降。

55.更进一步地,采用具有高导电能力铜和镍取代贵金属材料金、钯和银作为键合层材料,大幅降低了垂直结构led芯片的制造成本。

附图说明

56.通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚,在附图中:

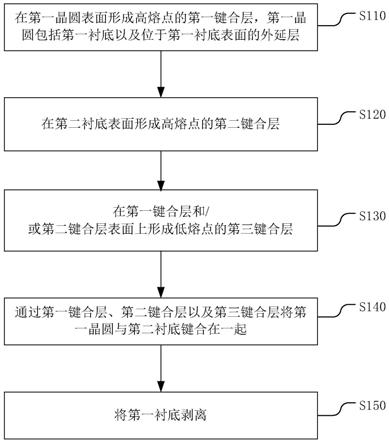

57.图1示出根据本发明实施例提供的垂直结构led芯片的制造方法流程示意图;

58.图2a至2h示出根据本发明实施例提供的一种垂直结构led芯片在制造过程中不同阶段的结构截面图;

59.图3a至3i示出根据本发明实施例提供的另一种垂直结构led芯片在制造过程中不同阶段的结构截面图。

具体实施方式

60.以下将参照附图更详细地描述本发明的各种实施例。在各个附图中,相同的元件采用相同或类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。

61.本发明可以各种形式呈现,以下将描述其中一些示例。

62.根据本发明实施例提供的垂直结构led芯片的制造方法,在第一晶圆表面形成第一键合层,在第二衬底表面形成第二键合层,其中,第一键合层、第二键合层为高熔点金属层,采用快速热退火处理高熔点金属层使其释放其内部较严重的应力(即应力调整层)。接着在第一键合层表面和/或第二键合层表面形成第三键合层,其中第三键合层为低熔点金属层,进而在较低温度环境下将第一晶圆(外延层)和第二衬底键合,以降低因材料晶格常数和热膨胀系统差异所导致的键合后晶圆翘曲严重的问题,提升工艺良率。

63.图1示出根据本发明实施例提供的垂直结构led芯片的制造方法流程示意图。图2a至2h示出根据本发明实施例提供的一种垂直结构led芯片在制造过程中不同阶段的结构截面图,本实施例提供的制造方法是对整片晶圆操作的,为方便理解,附图仅仅示出一个垂直结构led芯片单元。

64.如图1所示,垂直结构led芯片的制造方法包括以下步骤。

65.步骤s110:在第一晶圆表面形成高熔点的第一键合层,第一晶圆包括第一衬底以及位于第一衬底表面的外延层。具体地,如图2a所示,首先在第一衬底110的表面上形成外延层120。外延层120的总厚度为5微米~10微米。进一步地,制备外延层120例如采用金属有机物化学气相沉积工艺在第一衬底110的第一表面上依次形成缓冲层121、本征半导体层122、第一半导体层123、发光层124、电子阻挡层125、第二半导体层126。

66.接着,在第二半导体层126的表面上依次形成第一欧姆接触层131和反射镜层132,进而形成第一晶圆。更进一步地,采用光刻、物理气相沉积工艺在第二半导体层126的表面上形成第二掺杂类型的第一欧姆接触层131、以及在第一欧姆接触层131的表面上形成反射镜层132。第一欧姆接触层131例如为氧化铟锡,反射镜层132例如为银层。

67.在可替代的实施例中,还可以采用激光辅助分子束外延、激光溅射或氢化物气相外延等工艺形成外延层120。其中,本征半导体层122为非掺杂的氮化镓材料层,第一半导体层123为第一掺杂类型(n型)的氮化镓材料层,发光层124例如为多量子阱(mqw,multiple quantum well)层,电子阻挡层125例如为第二掺杂类型(p型)的氮化铝镓材料层,第二半导体层126例如为第二掺杂类型(p型)的氮化镓材料层,其中,外延层120可以是多晶结构层或单晶结构层。其中,多量子阱层例如由氮化镓/氮化铟镓/氮化铝镓材料所组成。

68.第一衬底110包含但不限于镜面或微米级/纳米级图形化蓝宝石衬底中的一种,在优选的实施例中,第一衬底110为微米级图形化蓝宝石。在其他可替代的实施例中,第一衬底110为异质衬底的一种,第一衬底110还可以是氧化镓、碳化硅、硅、氧化锌、镓酸锂单晶衬底或耐高温金属衬底。第一衬底110的厚度为300微米~2毫米,第一衬底110的直径为1英寸

~8英寸。其中,外延层120包含以氮化镓或者氮化铟镓材料体系组成的往复连续递进式led外延结构中的一种,其优选的实施例中外延层120为含不同铟组分的氮化铟镓结构。其中,在可替代的实施例中,第一欧姆接触层131还可以是氧化铟锡(ito)、氧化锌铝(azo)、镍金、镍银、镍铝中的一种,第一欧姆接触层131的厚度为1纳米~200纳米。反射镜层132还可以是铝层、镁层、铂层、铑层、金层中的一种,反射镜层132的厚度为60纳米~200纳米。

69.然后在反射镜层132远离第一欧姆接触层131的表面(第一晶圆的表面)依次形成金属阻挡层133和第一键合层134。第一键合层134为高熔点金属键合层,例如为高熔点的镍层。金属阻挡层133例如为钛铂叠层。在其他可替代的实施例中,金属阻挡层133还可以是铬、钛、镍、铂、金中的二元或多元体系中的一种,金属阻挡层133的厚度为50纳米~1微米。第一键合层134还可以是高熔点的金、镍层、铜层或者二元体系中的一种,第一键合层134的厚度为200纳米~2微米。更进一步地,形成第一键合层134的步骤包括:在金属阻挡层133表面形成第一键合层134,在温度为400℃~800℃的环境下对金属阻挡层133表面的第一键合层134进行快速退火处理以形成应力降低或者彻底释放的第一键合层134(应力调整层),其中退火处理的时间小于2分钟,以避免高温退火对其他半导体结构的影响。更进一步地,退火工艺选自激光退火技术或强光退火技术的其中一种。

70.步骤s120:在第二衬底表面形成高熔点的第二键合层。具体地,如图2b所示,在第二衬底210的表面上依次形成金属阻挡层133和第二键合层144。更进一步地,第二衬底210例如为直径4英寸、厚度200微米的铜钨金属衬底。金属阻挡层133例如为钛铂叠层。第二键合层144为高熔点金属键合层,例如为高熔点的镍层。在其他可替代的实施例中,第二衬底210可以是硅、铜、钼、钨、钼铜合金、铝硅合金衬底中的一种,第二衬底210的直径为1英寸~8英寸,第二衬底210的厚度为100微米~1微米。第二键合层144还可以是高熔点的金、镍层、铜层或者二元体系中的一种,第二键合层144的厚度为200纳米~2微米。更进一步地,形成第二键合层144的步骤包括:在金属阻挡层133表面形成第二键合层144,在温度为400℃~800℃的环境下对金属阻挡层133表面的第二键合层144进行快速退火处理以形成应力降低或者彻底释放的第二键合层144(应力调整层),其中退火处理的时间小于2分钟,以避免高温退火对其他半导体结构的影响。更进一步地,退火工艺选自激光退火技术或强光退火技术的其中一种。

71.步骤s130:在第一键合层和/或第二键合层表面上形成低熔点的第三键合层。具体地,如图2c所示,例如在第二衬底210上的第二键合层144表面,以及在第一晶圆上的第一键合层134表面分别形成低熔点的第三键合层135。第三键合层135例如为锡、铟单层或二元金属体系中的一种,第三键合层135的厚度为100纳米~2微米。在其他可替代的实施例中,例如仅在第二衬底210上的第二键合层144表面或者仅在第一晶圆表面的第一键合层134表面形成第三键合层135。

72.步骤s140:通过第一键合层、第二键合层以及第三键合层将第一晶圆与第二衬底键合在一起。具体地,如图2d所示,第一晶圆和第二衬底210的键合环境为真空,键合温度比第三键合层135的熔点温度高5℃~20℃,键合压力为5000kgf~15000kgf,键合时间不小于10分钟。更进一步地,采用液相瞬态键合工艺,键合温度为160℃~260℃。具体地,在温度约240℃的真空环境下将第一晶圆和第二衬底210键合在一起。

73.步骤s150:将第一衬底剥离。具体地,如图2e所示,通过衬底转移技术将第一衬底

110剥离。更进一步地,衬底转移技术可以是激光剥离、化学机械减薄、化学湿法腐蚀、干法刻蚀中的一种或多种工艺的组合。例如采用边长为200微米的正方形小光斑的激光将缓冲层121剥离分解,进而剥离位于缓冲层121表面的第一衬底110,实现第一衬底110与外延层120的分离,并采用稀盐酸溶液腐蚀本征半导体层122的表面以去除被分解形成的金属镓材料,进而得到如图2e所示的半导体结构。其中,激光为波长为248nm的紫外激光。

74.更进一步地,还包括形成第一台阶。具体地,如图2f所示,采用光刻工艺和刻蚀工艺对去除了缓冲层121的外延层120的边缘进行刻蚀以形成第一台阶154。具体的,依次刻蚀本征半导体层122、第一半导体层123、发光层124、电子阻挡层125、第二半导体层126以露出第一欧姆接触层131的表面。其中,第一台阶154的侧壁与第一欧姆接触层131的表面形成第一夹角,第一夹角为30

°

~60

°

,优选地,第一夹角为40

°

。进一步的,对本征半导体层122的表面进行粗化,例如采用浓度约为2mol/l的热氢氧化钾溶液腐蚀本征半导体层122以得到粗化表面。在其他实施例中,也可以采用湿法腐蚀或干法刻蚀形成粗化表面。接着采用干法刻蚀工艺对本征半导体层122进行刻蚀以形成露出第一半导体层123的开口,该开口中后续可以形成第一电极(n电极)。

75.更进一步地,还包括形成第一电极和第二电极。具体地,如图2g所示,采用光刻工艺和电子束蒸发工艺在本征半导体层122的开口中制备第一电极(n电极)137,第一电极137与第一半导体层123接触。然后对第二衬底210远离第二键合层144的表面进行减薄,并在减薄的第二衬底210表面形成第二电极139(p电极)。第一电极137的材料例如为al/ti/au。第二电极139同时起到电流扩展、欧姆接触、固晶焊接的作用。

76.更进一步地,还包括形成钝化层。具体地,如图2h所示,采用化学气相淀积工艺在本征半导体层122的表面、第一台阶154的侧壁和第一欧姆接触层131的表面形成钝化层138,钝化层138例如为二氧化硅层。

77.接着采用激光切割和裂片工艺得到多个垂直结构led芯片。

78.图3a至3i示出根据本发明实施例提供的另一种垂直结构led芯片在制造过程中不同阶段的结构截面图,本实施例提供的制造方法是对整片晶圆操作的,为方便理解,附图仅仅示出一个垂直结构led芯片单元。

79.结合图1,制造另一种垂直结构led芯片的制造方法包括以下步骤。

80.步骤s110:在第一晶圆表面形成高熔点的第一键合层,第一晶圆包括第一衬底以及位于第一衬底表面的外延层。具体地,首先,如图3a所示,在第一衬底410的表面上依次形成外延层420。外延层420的总厚度为5微米~10微米。进一步地,制备外延层420例如采用金属有机物化学气相沉积工艺在第一衬底410的第一表面上依次形成缓冲层421、本征半导体层422、第一半导体层423、发光层424、电子阻挡层425、第二半导体层426。

81.接着,采用光刻和干法刻蚀工艺在外延层420中形成阵列分布的至少一个通孔401,通孔401依次贯穿第二半导体层426、电子阻挡层425、发光层424并露出第一半导体层423。其中,本征半导体层422为非掺杂的氮化镓材料层,第一半导体层423为第一掺杂类型(n型)的氮化镓材料层,发光层424例如为多量子阱(mqw,multiple quantum well)层,电子阻挡层425例如为第二掺杂类型(p型)的氮化铝镓材料层,第二半导体层426例如为第二掺杂类型(p型)的氮化镓材料层,其中,外延层420可以是多晶结构层或单晶结构层。第一衬底410例如为硅衬底。第一衬底410的直径例如为6英寸。

82.接着,如图3b所示,采用光刻和物理气相沉积工艺在通孔401中形成第一掺杂类型的第二欧姆接触层427。第二欧姆接触层427例如是铬、铝、钛、钒、铪、镍、铂、金中的一种或多种金属叠层,总厚度例如为800nm。之后在第二半导体层426表面依次形成第一欧姆接触层431、反射镜层432以及金属阻挡层433。更进一步地,采用光刻、湿法腐蚀和溅射工艺在外延层420除通孔401区域外的第二半导体层426表面形成第二掺杂类型的第一欧姆接触层431、在第一欧姆接触层431表面形成反射镜层432、以及在反射镜层432的表面形成金属阻挡层433。第一欧姆接触层431例如为镍金层,反射镜层432例如为厚度100纳米的铝层,金属阻挡层433例如为厚度200纳米的钛钨叠层。

83.接着,采用化学气相沉积工艺在金属阻挡层433的表面以及通孔401中形成介质层404。介质层404例如为氮化硅层,厚度例如为500nm。接着采用光刻和干法刻蚀技术在介质层404中形成与第二欧姆接触层427连通的开口402,进而形成第一晶圆。介质层404覆盖金属阻挡层433的表面、通孔的侧壁,并露出第二欧姆接触层427的表面,也即第二欧姆接触层427与外延层420的侧壁之间设置有介质层404。在其他实施例中,介质层404也可以是氧化硅、氧化铝等其他绝缘材料。

84.接着,如图3c所示,采用物理气相沉积工艺在介质层404远离金属阻挡层433的表面以及开口402中(第一晶圆的表面)形成粘附层(图中未示出),以及在粘附层表面形成高熔点的第一键合层434。更进一步地,形成于介质层404表面以及开口402中的粘附层例如为厚度100纳米的钛层,第一键合层434例如为厚度800纳米的镍层。更进一步地,在粘附层表面形成第一键合层434的步骤包括:在粘附层表面形成第一键合层434,在温度为400℃~800℃的环境下对第一键合层434进行快速退火处理以形成应力降低或者彻底释放的第一键合层434(应力调整层),其中退火处理的时间小于2分钟,以避免高温退火对其他半导体结构的影响。更进一步地,退火工艺选自激光退火技术或强光退火技术的其中一种。

85.步骤s120:在第二衬底表面形成高熔点的第二键合层。具体地,如图3d所示,采用物理气相沉积工艺在第二衬底520的表面依次形成粘附层(图中未示出)和高熔点的第二键合层444。第二衬底520例如为直径6英寸、厚度1毫米的硅衬底。形成于第二衬底520表面的粘附层例如为厚度50纳米的钛层,第二键合层444例如为厚度600纳米的镍层。更进一步地,在粘附层表面形成第二键合层444的步骤包括:在粘附层表面形成第二键合层444,在温度为400℃~800℃的环境下对第二键合层444进行快速退火处理以形成应力降低或者彻底释放的第二键合层444(应力调整层),其中退火处理的时间小于2分钟,以避免高温退火对其他半导体结构的影响。更进一步地,退火工艺选自激光退火技术或强光退火技术的其中一种。在可替代的实施例中,在第二衬底520和粘附层之间还形成金属阻挡层433。

86.步骤s130:在第一键合层和/或第二键合层表面上形成低熔点的第三键合层。具体地,如图3e所示,例如在第二衬底520上的第二键合层444表面,以及在第一晶圆上的第一键合层434表面分别形成低熔点的第三键合层435。第三键合层435例如为锡、铟单层或二元金属体系中的一种,第三键合层435的厚度为100纳米~2微米。在其他可替代的实施例中,例如仅在第二衬底520上的第二键合层444表面或者仅在第一晶圆表面的第一键合层434表面形成第三键合层435。

87.步骤s140:通过第一键合层、第二键合层以及第三键合层将第一晶圆与第二衬底键合在一起。具体地,如图3f所示,第一晶圆和第二衬底520的键合环境为真空,键合温度比

第三键合层435的熔点温度高5℃~20℃,键合压力为5000kgf~15000kgf,键合时间不小于10分钟。更进一步地,采用液相瞬态键合工艺,键合温度为160℃~260℃。具体地,在温度约180℃的真空环境下将第一晶圆和第二衬底520键合在一起。

88.步骤s150:将第一衬底剥离。具体地,如图3g所示,通过衬底转移技术将第一衬底410剥离。更进一步地,采用减薄设备将第一衬底410减薄50微米,随后采用硅蚀刻液将剩余第一衬底410以及缓冲层421腐蚀去除,暴露出外延层420的本征半导体层422。接着采用化学湿法腐蚀工艺利用浓度约6mol/l的氢氧化钾热溶液,在温度约70℃的环境下对本征半导体层422表面进行粗化处理以形成粗化表面,有利于增加出光。

89.更进一步地,还包括形成第二台阶。具体地,如图3h所示,采用光刻和干法刻蚀工艺对去除了缓冲层421的外延层420的边缘进行刻蚀以形成第二台阶454。具体的,依次刻蚀本征半导体层422、第一半导体层423、发光层424、电子阻挡层425、第二半导体层426、第一欧姆接触层431、反射镜层432以暴露金属阻挡层433表面。在第二台阶454的下表面的金属阻挡层433上后续可以形成第二电极(p电极)。

90.更进一步地,还包括形成第一电极、第二电极以及钝化层。具体地,如图3i所示,采用光刻工艺和电子束蒸发工艺在第二台阶454的下表面形成与金属阻挡层433接触的第二电极439。第二电极439例如为cr/pt/au。然后对第二衬底520远离第二键合层444的表面进行减薄,并在减薄的第二衬底520表面形成第一电极437(n电极),第一电极437例如为钛金金属层。进一步的,采用化学气相淀积工艺在本征半导体层422表面以及第二台阶454的侧壁形成钝化层438,钝化层438例如为厚度200纳米的二氧化硅层。

91.接着采用激光表面切割、激光隐形切割和裂片工艺得到多个垂直结构led芯片。

92.依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明的保护范围应当以本发明权利要求所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1