一种MOSFET器件结构及制造方法与流程

一种mosfet器件结构及制造方法

技术领域

1.本发明属于半导体分立器件技术领域,特别涉及一种mosfet器件结构及制造方法。

背景技术:

2.mosfet因其开关速度快、导通电阻低而在电源领域得到广泛的应用。近几年,随着高频高效率电源的需求,对于速度更快、功耗和导通电阻更低的功率mosfet的需求越来越多。电路设计师为了提高电路的工作效率,主要关心器件的品质优质fom=(rds(on)

×

qgd)。栅漏电荷qgd反映了器件的开关损耗,qgd越小开关损耗越小,qgd越大开关损耗越大;导通电阻rds(on)反映了器件的导通损耗,rds(on)越小导通损耗越小,rds(on)越小导通损耗越大。

3.传统的功率mosfet存在导通电阻和击穿电压、导通电阻和开关时间两个重要的矛盾。在有源区面积相同的情况下,击穿电压越高导通电阻越大,击穿电压越低导通电阻越小。导通电阻和开关时间与有源区的面积有关,有源区面积越大,导通电阻越小,开关时间越长;有源区面积越小,导通电阻越大,开关时间越短。

技术实现要素:

4.本发明的目的是提供一种mosfet器件结构及制造方法,以解决上述问题。

5.为实现上述目的,本发明采用以下技术方案:

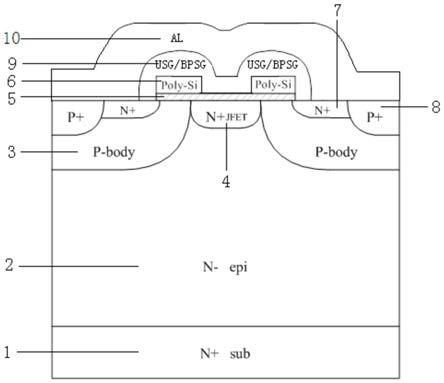

6.一种mosfet器件结构,包括n+衬底1、n

‑

外延层2、p

‑

body扩散窗口3、n+jfet扩散窗口4、栅介质层5、栅极多晶硅6、源n+扩散窗口7、源p+扩散窗口8和栅源隔离层9;n

‑

外延层2设置在n+衬底1上,n

‑

外延层2的左右两侧设置了器件的单胞主结p

‑

body扩散窗口3,两个p

‑

body扩散窗口3之间设置了n+jfet扩散窗口4、p

‑

body扩散窗口3和n+jfet扩散窗口4上的纵向方向设置了栅介质层5,栅介质层5上依次设置有栅极多晶硅6和栅源隔离层9,金属层10设置在栅源隔离层9上,栅介质层5设置有源n+扩散窗口7和源p+扩散窗口8,源n+扩散窗口7、源p+扩散窗口8和源极金属10连接构成源极,栅极金属11通过开孔与栅极多晶硅6连接构成栅极,漏极金属与n+衬底1连接构成漏极,源极金属10与结终端12相连。

7.进一步的,器件结构为条形结构或元胞结构;栅极多晶硅6在元胞上刻蚀成两段。

8.进一步的,n+衬底1材料为si,掺as或掺sb,电阻率0.002ω.cm~0.004ω.cm;n

‑

外延层2材料为外延法生长的si材料,掺p,电阻率0.4ω.cm~70ω.cm。

9.进一步的,源极金属10为al/alsicu,栅极金属为al/alsicu

10.进一步的,一种mosfet器件结构的制造方法,包括以下步骤:

11.完整的制造工艺流程为:外延片

→

激光打标

→

牺牲氧化层生长

→

场限环光刻

→

场限环注入

→

去胶

→

场限环退火

→

氧化层去除

→

场氧生长

→

场氧光刻+刻蚀

→

去胶

→

牺牲氧化层生长

→

n+jfet光刻

→

n+jfet注入

→

去胶

→

n+jfet退火

→

去牺牲氧化层

→

栅氧化层生长

→

多晶硅淀积

→

多晶硅掺杂

→

多晶硅光刻+刻蚀

→

去胶

→

p

‑

body注入

→

p

‑

body扩散

→

去

掉多余残氧

→

nsd光刻

→

nsd注入

→

去胶

→

激活

→

隔离层淀积

→

回流

→

引线孔光刻+刻蚀

→

去胶

→

psd注入

→

回流

→

正面金属铝溅射

→

铝光刻+刻蚀

→

去胶

→

钝化层淀积

→

pad光刻+刻蚀

→

去胶

→

合金

→

背面减薄

→

背面金属化

→

cp测试

→

入库。

12.进一步的,确定外延层电阻率和外延层厚度:利用公式(1)计算出满足一定击穿电压的外延浓度和厚度,击穿电压给10%~20%的设计余量;

[0013][0014]

由(1)式可知:选取最优的wb和nb,须先确定外延电阻率的下限值和外延厚度的上限值:

[0015]

①

外延电阻率的下限值

[0016]

外延浓度的上限值由以下(2)式计算,

[0017][0018]

bvdss留10%~20%的设计余量,相应电阻率的下限值可以由以下(3)式计算:

[0019][0020]

其中q为元电荷q=1.6

×

10

‑

19

c,μ

n

为电子迁移率;

[0021]

②

漂移区厚度的上限值

[0022]

在外延浓度上限值确定后,外延厚度的上限值可由以下(4)式计算:

[0023][0024]

耗尽层在高阻外延区展宽的厚度xmn由(5)式计算得到:

[0025][0026]

耗尽层在p阱区展宽的厚度xmp由(6)式计算得到:

[0027][0028]

进一步的,n+jfet扩散窗口4的工艺制造方法是:在牺牲氧化层生长之后,n+jfet注入之前,增加一步局部n+jfet光刻工艺,具体工艺制造流程为:牺牲氧化层生长

→

n+jfet光刻

→

n+jfet注入。

[0029]

进一步的,jfet普注工艺流程为:外延片

→

激光打标

→

牺牲氧化层生长

→

场限环光刻

→

场限环注入

→

去胶

→

场限环退火

→

氧化层去除

→

场氧生长

→

场氧光刻+刻蚀

→

去胶

→

牺牲氧化层生长

→

n+jfet注入

→

去胶

→

n+jfet退火

→

去牺牲氧化层

→

栅氧化层生长

→

多晶硅淀积

→

多晶硅掺杂

→

多晶硅光刻+刻蚀

→

去胶

→

p

‑

body注入

→

p

‑

body扩散

→

去掉多余残氧

→

nsd光刻

→

nsd注入

→

去胶

→

激活

→

隔离层淀积

→

回流

→

引线孔光刻+刻蚀

→

去胶

→

psd注入

→

回流

→

正面金属铝溅射

→

铝光刻+刻蚀

→

去胶

→

钝化层淀积

→

pad光刻+刻蚀

→

去胶

→

合金

→

背面减薄

→

背面金属化

→

cp测试

→

入库。

[0030]

与现有技术相比,本发明有以下技术效果:

[0031]

⑴

减小开关参数的机理

[0032]

密勒电容cgd相当于平行板电容器,根据电容的计算公式εr为相对介电常数,s为电容极板的正对面积,d为电容极板的距离,k为静电力常数。采用图1的新结构,通过减小密勒电容的正对面积s来降低cgd。

[0033]

⑵

减小外延电阻的机理

[0034]

外延电阻相当于一段粗导线的电阻,根据欧姆定理电阻的计算公式ρ为电阻的电阻率,l为电阻的长度,s为电阻的横截面积。由上式可以看出,材料的电阻大小正比于材料的电阻率和长度,反比于材料的面积。外延穿通的设计方法是通过减小外延电阻率ρ和外延厚度(相当于电阻长度l)来降低图2外延层电阻r

epi

。

[0035]

⑶

局部jfet注入减小jfet电阻机理

[0036]

通过局部jfet注入,可以提高图2中jfet区的电阻率ρ,增加jfet区的面积s,已达到减小jfet区电阻r

jfet

的目的。同时局部jfet注入可以减小图2中沟道的长度l,也可以间接起到降低沟道电阻rch的作用。

[0037]

本发明涉及一种优化的mosfet设计和制造方法,在版图、工艺条件和产品静态参数基本不变的情况下,采用图1所示的mosfet新结构可以使开关参数降低17%~23.8%;在版图不变的情况下,采用外延穿通的设计方法,可以使高压mosfet的导通电阻降低12.5%~27.6%;在版图和其他工艺条件基本不变的情况下,采用图1新结构中“4.n+jfet扩散窗口”进行局部jfet注入,可以使低压mosfet的导通电阻降低11.3%~25.4%。

附图说明

[0038]

图1是本发明结构的单胞示意图;

[0039]

其中,1.n+衬底;2.n

‑

外延层;3.p

‑

body扩散窗口;4.n+jfet扩散窗口;5.栅介质层;6.栅极多晶硅;7.源n+扩散窗口;8.源p+扩散窗口;9.栅源隔离层;10金属层。

[0040]

图2为mosfet芯片的电阻组成;

[0041]

图3是本发明结构的版图示意图;

[0042]

其中,9.栅源隔离层;10源极金属层;11.栅极金属;12结终端。

具体实施方式

[0043]

下面结合附图和具体实施方式对本发明进行详细说明。

[0044]

⑴

减小开关参数技术方案

[0045]

请参阅图1,本发明公开了一种优化的mosfet设计和制造方法。器件的基本单元结构为条形结构或元胞结构,包括n+衬底1、n

‑

外延层2、p

‑

body扩散窗口3、n+jfet扩散窗口4、栅介质层5、栅极多晶硅6、栅极多晶硅6在元胞上刻蚀成两段、源n+扩散窗口7、源p+扩散窗口8和栅源隔离层9、n

‑

外延层2设置在n+衬底1上,n

‑

外延层2的左右两侧设置了器件的单胞主结p

‑

body扩散窗口3,两个p

‑

body扩散窗口3之间设置了n+jfet扩散窗口4、p

‑

body扩散窗口3和n+jfet扩散窗口4上的纵向方向设置了栅介质层5,栅介质层5上依次设置有栅极多晶

硅6和栅源隔离层9,栅介质层设置有源n+扩散窗口7和源p+扩散窗口8,源n+扩散窗口7、源p+扩散窗口8和源极金属10连接构成源极,栅极金属与栅极多晶硅6连接构成栅极,漏极金属与n+衬底1连接构成漏极。

[0046]

⑵

减小导通电阻技术方案——外延穿通的设计方法

[0047]

外延穿通的设计方法是采用外延穿通型设计理念,利用公式(1)计算出满足一定击穿电压的外延浓度和厚度,在这里为了满足器件的可靠性,击穿电压给10%~20%的设计余量。

[0048][0049]

由(1)式可知:对于一定的击穿电压,存在无限的(nb,wb)组合,都可以满足要求,设计中要选取一组使导通电阻最小。要选取最优的wb和nb,必须先确定外延电阻率的下限值和外延厚度的上限值。

[0050]

①

外延电阻率的下限值

[0051]

外延浓度的上限值可以由以下(2)式计算,

[0052][0053]

在设计中,考虑器件的可靠性,bvdss一般留10%~20%的设计余量。相应电阻率的下限值可以由以下(3)式计算:

[0054][0055]

其中q为元电荷q=1.6

×

10

‑

19

c,μ

n

为电子迁移率,与外延浓度有关。

[0056]

②

漂移区厚度的上限值

[0057]

在外延浓度上限值确定后,外延厚度的上限值可由以下(4)式计算:

[0058][0059]

即:外延厚度超过wb,对击穿电压起不到任何作用,反而会造成导通电阻ron的增加。

[0060]

耗尽层在高阻外延区展宽的厚度xmn可以由(5)式计算得到:

[0061][0062]

耗尽层在p阱区展宽的厚度xmp可以由(6)式计算得到:

[0063][0064]

p阱结深xjp要超过xmp,在保证击穿电压的同时避免沟道穿通。

[0065]

⑶

局部jfet注入技术方案

[0066]

n+jfet扩散窗口4的工艺制造方法是:在牺牲氧化层生长之后,n+jfet注入之前,增加一步局部n+jfet光刻工艺,具体工艺制造流程为:牺牲氧化层生长

→

n+jfet光刻

→

n+

jfet注入,牺牲氧化层生长之前和n+jfet注入之后的工艺制造流程与jfet普注流程一致。

[0067]

n+jfet扩散窗口4在两个p

‑

body扩散窗口3之间,针对不同击穿电压的产品,n+jfet扩散窗口4长度为1.2~7μm,工艺参数为:注入材料ash3,注入剂量1e15~1.5e15,注入能量80kev~90kev,激活温度850~900℃,激活时间10min~15min。

[0068]

本技术方案以n沟道mosfet为例,适用于p沟道mofet。

[0069]

本发明结构的实现,不需要额外增加工艺设备,和现有mosfet平面工艺兼容,适用于辐照mosfet产品。

[0070]

工艺制造过程中,需要增加两步工艺:

⑴

在牺牲氧化层生长之后,n+jfet注入之前,增加一步局部n+jfet光刻工艺;

⑵

需要增加一步jfet上局部栅极多晶硅的刻蚀工艺。

[0071]

本方案可以减小mosfet器件的导通电阻,减小栅电荷,提高器件的品质优质fom。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1