半导体元件及其制作方法与流程

1.本发明涉及半导体技术领域,特别是涉及一种鳍式场效晶体管(finfet)半导体元件及其制作方法。

背景技术:

2.鳍式场效晶体管(finfet)是非平面的多栅极晶体管,具有从栅极垂直延伸并形成晶体管的源极和漏极的“鳍”。多个finfet可以彼此耦合以提供集成电路元件。导电层可以形成在鳍之上以在相邻的finfet之间提供局部互连。

3.使用局部互连可实现更高的封装密度和更低的阻值rsd。然而,局部互连的槽接触的形成增加了寄生边缘电容(cof),这显著降低了电路速度。因此,本领域需要提供一种改进的半导体元件,其能够抑制栅极与槽接触之间的电容耦合。

技术实现要素:

4.本发明的主要目的在于提供一种改良的半导体元件及其制造方法,以解决现有技术的不足与缺点。

5.本发明一方面提供一种半导体元件,包含一鳍片,从一基底突出并沿第一方向延伸;一栅极结构,在所述鳍片上沿第二方向延伸;一密封层,位于所述栅极结构的侧壁上;一第一碳峰值浓度,位于所述密封层中;一第一间隙壁层,位于所述密封层上;一第二碳峰值浓度,位于所述第一间隙壁层中;以及一第二间隙壁层,位于所述第一间隙壁层上。

6.根据本发明实施例,所述密封层包含siocn且厚度为40埃,其中所述第一间隙壁层包含siocn且厚度为70埃。

7.根据本发明实施例,所述第一碳峰值浓度位于所述第一间隙壁层和所述第二间隙壁层之间的界面下方80埃至84埃处。

8.根据本发明实施例,所述第二间隙壁层为富硅氮化硅层,厚度为55埃。

9.根据本发明实施例,所述第二碳峰值浓度位于所述第二间隙壁层的顶面下方80~84埃处。

10.根据本发明实施例,所述栅极结构包含栅极介电层和位于所述栅极介电层上的金属栅极。

11.根据本发明实施例,所述半导体元件还包含与所述第二间隙壁层相邻的源/漏极区。

12.根据本发明实施例,所述半导体元件还包含在所述源/漏极区中的外延层。

13.根据本发明实施例,所述外延层包含sip、sic或sige。

14.根据本发明实施例,所述密封层的介电常数小于4。

15.本发明另一方面提供一种形成半导体元件的方法,包含:形成从基底突出并沿第一方向延伸的鳍片;在所述鳍片上形成沿第二方向延伸的栅极结构;在所述栅极结构的侧壁上形成密封层;在所述密封层上形成第一间隙壁层;进行第一碳注入制作工艺,以将碳注

入所述密封层,使得所述密封层中具有第一碳峰值浓度;在所述第一间隙壁层上形成第二间隙壁层;以及进行第二碳注入制作工艺,以将碳注入所述第一间隙壁层,使得所述第一间隙壁层具有第二碳峰值浓度。

16.根据本发明实施例,所述密封层包含siocn且厚度为40埃,其中所述第一间隙壁层包含siocn且厚度为70埃。

17.根据本发明实施例,所述第一碳峰值浓度位于所述第一间隙壁层和所述第二间隙壁层之间的界面下方80埃至84埃处。

18.根据本发明实施例,所述第二间隙壁层为富硅氮化硅层,厚度为55埃。

19.根据本发明实施例,所述第二碳峰值浓度位于所述第二间隙壁层的顶面下方80~84埃处。

20.根据本发明实施例,所述方法是以30度的倾角、2kev的注入能量和5e15原子/cm2的注入剂量执行所述第一碳注入制作工艺和所述第二碳注入制作工艺。

21.根据本发明实施例,所述方法还包含:形成与所述第二间隙壁层相邻的源/漏极区。

22.根据本发明实施例,所述方法还包含:在所述源/漏极区形成外延层。

23.根据本发明实施例,所述外延层包含sip、sic或sige。

24.根据本发明实施例,所述密封层的介电常数小于4。

25.本发明的主要优点在于:密封层中形成第一碳峰值浓度且第一间隙壁层中形成第二碳峰值浓度,使得密封层和第一间隙壁层的介电常数可以明显降低,达到降低寄生边缘电容的作用。

附图说明

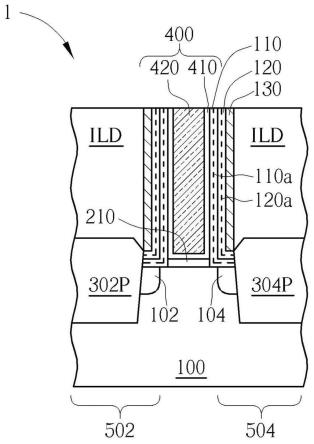

26.图1至图6为本发明实施例所绘示的半导体元件的制作方法示意图。

27.主要元件符号说明

28.1 半导体元件

29.100 基底

30.102、104 轻掺杂漏极区域

31.110 密封层

32.110a 第一碳峰值浓度

33.120 第一间隙壁层

34.120a 第二碳峰值浓度

35.130 第二间隙壁层

36.200 栅极结构

37.210 栅极介电层

38.220 导电层

39.230 硬掩模层

40.302、304 凹陷区域

41.302p、304p 外延层

42.400 栅极结构

43.410 栅极介电层

44.420 金属栅极

45.502、504 源/漏极区

46.f 鳍片

47.ild 介电层

48.im 离子注入制作工艺

49.cim-1、cim-2 碳注入制作工艺

50.θ 倾角

51.r

p1

、r

p2 碳注入投射范围

具体实施方式

52.在下文中,将参照附图说明细节,该些附图中的内容也构成说明书细节描述的一部分,并且以可实行该实施例的特例描述方式来绘示。下文实施例已描述足够的细节使该领域的一般技术人士得以具以实施。

53.当然,也可采行其他的实施例,或是在不悖离文中所述实施例的前提下作出任何结构性、逻辑性、及电性上的改变。因此,下文的细节描述不应被视为是限制,反之,其中所包含的实施例将由随附的权利要求来加以界定。

54.请参阅图1至图6,其为根据本发明实施例所绘示的半导体元件1的制作方法示意图。如图1所示,首先提供一基底100,例如,硅基底或其它合适的半导体基底。接着形成从基底100突出并沿第一方向延伸的鳍片f,然后,在鳍片f上形成沿第二方向延伸的栅极结构200,其中,第一方向可以垂直于第二方向。由于在基底100上形成鳍片f和栅极结构200为现有随机数,因此其细节不另赘述。

55.根据本发明实施例,栅极结构200可以包含栅极介电层210、导电层220和硬掩模层230,但不限于此。例如,栅极介电层210可以是硅氧层,导电层220可以是多晶硅层,硬掩模层230可以是氮化硅层。

56.接着,在栅极结构200和鳍片f上形成密封层110。根据本发明实施例,密封层110包含siocn且具厚度介于35至45埃,例如,40埃。根据本发明实施例,密封层110的介电常数小于4。

57.根据本发明实施例,密封层110可以利用化学气相沉积(cvd)或原子层沉积(ald)等方法形成。根据本发明实施例,密封层110均匀地沉积在栅极结构200的侧壁上和鳍片f的表面上。

58.如图2所示,接着,进行离子注入制作工艺im,将n型或p型掺质注入到鳍片f中,形成轻掺杂漏极(ldd)区域102和104。在栅极结构200两侧是源/漏极区502和504。

59.如图3所示,接着在密封层110上形成第一间隙壁层120。根据本发明实施例,第一间隙壁层120包含siocn。根据本发明实施例,第一间隙壁层120的厚度介于65至75埃,例如,70埃。第一间隙壁层120可以利用化学气相沉积或原子层沉积等方法形成。

60.在沉积第一间隙壁层120之后,进行第一次的碳注入制作工艺cim-1,将碳注入密封层110,使得密封层110中具有第一碳峰值浓度110a。根据本发明实施例,第一碳注入制作工艺cim-1是以30度的倾角θ、2kev的注入能量和5e15原子/cm2的注入剂量进行。在上述条

件下,碳注入投射范围(carbon implant projected range)r

p1

为80~84埃,例如,82埃。

61.根据本发明实施例,如图3中圆圈处所示的放大示意图所示,第一碳峰值浓度110a位于第一间隙壁层120表面下方80埃至84埃处,例如,82埃。

62.如图4所示,接着,在第一间隙壁层120上形成第二间隙壁层130。根据本发明实施例,第二间隙壁层130为富硅(silicon-rich)氮化硅层。根据本发明实施例,第二间隙壁层130的厚度约为55埃。第二间隙壁层130可以利用化学气相沉积或原子层沉积等方法形成。

63.在沉积第二间隙壁层130之后,进行第二次的碳注入制作工艺cim-2,将碳注入第一间隙壁层120和第二间隙壁层130,使得第一间隙壁层120中具有第二碳峰值浓度120a。根据本发明实施例,第二碳注入制作工艺cim-2可以同样以30度的倾角θ、2kev的注入能量和5e15原子/cm2的注入剂量进行。在上述条件下,碳注入投射范围r

p2

为80~84埃,例如,82埃。

64.接着,如图5所示,进行各向异性干蚀刻制作工艺,蚀刻第二间隙壁层130、第一间隙壁层120和密封层110,在栅极结构200两侧的源/漏极区502和504内的鳍片f中分别形成凹陷区域302和304。

65.根据本发明实施例,如图5中圆圈处所示的放大示意图所示,第二碳峰值浓度120a位于第二间隙壁层130的顶面下方80~84埃处,例如,82埃。第一碳峰值浓度110a位于第一间隙壁层120和第二间隙壁层130之间的界面下方80埃至84埃处。

66.如图6所示,接着进行外延制作工艺,从栅极结构200两侧的源/漏极区502和504内的凹陷区域302和304中成长出外延层302p和304p。根据本发明实施例,外延层302p和304p可以包含sip、sic或sige,但不限于此。接着,沉积介电层ild,再进行置换金属栅极(rmg)制作工艺,形成栅极结构400。

67.根据本发明实施例,栅极结构400包含栅极介电层410和位于栅极介电层410上的金属栅极420,其中,栅极介电层410可以是任何合适的高介电常数材料,金属栅极420可以包含钛、氮化钛、铜、钨、铝,其合金或任意组合。

68.本发明的主要优点在于:密封层110中具有第一碳峰值浓度110a且第一间隙壁层120中具有第二碳峰值浓度120a,使得成分为siocn的密封层110和第一间隙壁层120的介电常数(k)可以明显降低,达到降低寄生边缘电容(cof)的作用。

69.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1