一种叠层式三维多芯片组件封装结构及其封装方法与流程

1.本发明涉及3d封装技术领域,具体地涉及一种基于二维多芯片组件垂直叠层实现的叠层式三维多芯片组件封装结构及其封装方法。

背景技术:

2.电子器件的封装技术是制约集成电路发展的关键环节。电子封装是将各种功能的芯片、元器件和承载基板提供保护并保障信号和功率的输入与输出,同时使器件工作中产生的热量传输到外部环境,确保器件稳定正常地运行。

3.常规的mcm技术是一个二维平面技术,它是将多个ic裸芯片、塑封器件或片式器件紧密排列在一个平面衬底上封装而成的。这种封装技术目前已接近其理论的最大封装密度。一般情况下,采用常规工艺加工金属外壳封装的mcm集成电路组装密度在18%~42%之间;环氧涂覆双面混装的mcm集成电路组装密度在30%~50%之间;采用倒装焊工艺、bga器件和ltcc空腔工艺技术能够提高电路的组装密度,也只能做到70%~80%的组装密度。

4.上述常规工艺的封装结构的组装密度比较低,还有待进一步提高。为进一步提高组装密度、减少体积,必须使封装技术从二维向三维发展,即在z轴方向上实现多层结构。这种z轴方向上的紧密堆积可以是芯片(即3d硅,裸芯片或封装芯片皆可)的堆垛,也可以是mcm叠层(构成所谓的3d-mcm)。

技术实现要素:

5.针对上述存在的技术问题,本发明目的是:提供一种叠层式三维多芯片组件封装结构及其封装方法,解决现有技术中采用常规工艺的封装结构封装密度低的问题。

6.本发明的技术方案是:本发明的一个目的在于提供一种叠层式三维多芯片组件封装结构,包括:至少一层第一基板,所述第一基板包括本体和设于所述本体四周的弯折部,所述本体的第一正面和第一背面上按需设计有元器件和走线;空腔部,由所述弯折部的内侧面和所述本体的第一正面围合形成,用于容纳设于所述本体的第一正面的元器件;bga焊点阵列,设置在所述弯折部的远离所述本体的端部上;第二基板,与所述第一基板在垂直方向上下排布设置,所述第二基板的第二正面朝向所述第一基板的所述空腔部且第二正面上设有面阵i/o端子焊盘;bga焊点端子,设置在所述面阵i/o端子焊盘上,与所述bga焊点阵列配合连接;外引线,设置在所述第二基板的第二背面上并沿背离所述第二背面的方向向外延伸,所述第二背面背向所述第一基板的所述空腔部的一面设置。

7.可选的,所述第一基板包括两层,两层所述第一基板在垂直方向上下排布;且上层第一基板的空腔部朝向下层第一基板的第一背面设置,以使上层第一基板的空腔部可容纳下层第一基板的第一背面上的元器件;

下层第一基板的空腔部朝向所述第二基板的第二正面设置,以使下层第一基板的空腔部可容纳第二基板的第二正面上的电子元器件;下层第一基板的第一背面上设有与上层第一基板上的bga焊点阵列相匹配的bga焊点阵列。

8.可选的,所述bga焊点端子为由第二正面朝向背离所述第二背面方向凸出延伸的bga焊球凸点端子。

9.可选的,所述第一基板为ltcc基板。

10.可选的,所述第二基板为一体化pga基板。

11.可选的,所述外引线的数量为多个,多个所述外引线呈阵列排布。

12.本发明的另一个目的在于提供一种叠层式三维多芯片组件封装结构的封装方法,包括以下步骤:在第一基板的第一正面上形成有朝向第一背面凹陷的空腔部,空腔部的外周形成为弯折部;在弯折部的端部形成bga焊点阵列;在第二基板的第二正面上的面阵i/o端子焊盘上制作出bga焊点端子;在第二基板的第二背面上制作出外引线;将第一基板上的bga焊点阵列与第二基板上的bga焊点端子上下压接在一体,实现垂直互连。

13.可选的,采用smt表面组装工艺实现表面贴装元器件与第一基板及第二基板的物理与电学互连。

14.可选的,采用置球工艺在所述第二基板上制作出所述bga焊点端子。

15.可选的,所述外引线采用钎焊工艺形成在所述第二基板的第二背面上。

16.与现有技术相比,本发明的优点是:本发明的叠层式三维多芯片组件封装结构,通过第一基板上设置有空腔部,使得在进行三维垂直方向封装时基板的正面和背面均可以组装元器件,从而可以提高封装结构的组装密度,使得封装结构的组装密度可以达到100%,解决了现有技术中采用常规工艺导致组装密度比较低的问题。

附图说明

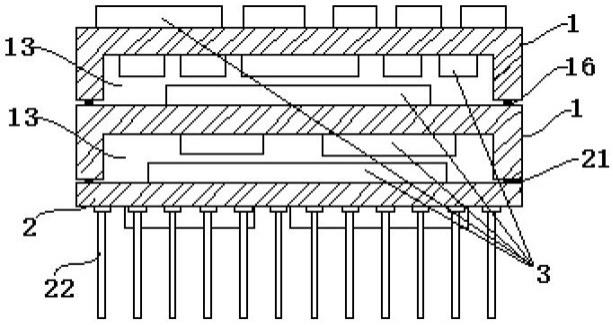

17.下面结合附图及实施例对本发明作进一步描述:图1为本发明实施例的叠层式三维多芯片组件封装结构的第一基板的结构示意图;图2为本发明实施例的叠层式三维多芯片组件封装结构的第二基板的结构示意图;图3为本发明实施例的叠层式三维多芯片组件封装结构的结构示意图。

18.其中:1、第一基板;11、本体;12、弯折部;13、空腔部;14、第一正面;15、第一背面;16、bga焊点阵列;2、第二基板;21、bga焊点端子;22、外引线;23、第二正面;24、第二背面;3、元器件。

具体实施方式

19.为使本发明的目的、技术方案和优点更加清楚明了,下面结合具体实施方式并参照附图,对本发明进一步详细说明。应该理解,这些描述只是示例性的,而并非要限制本发明的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本发明的概念。

20.实施例:参见图1至图3,本发明实施例的叠层式三维多芯片组件封装结构,包括两层第一基板1和一个第二基板2,两层第一基板1和一个第二基板2在垂直方向也即如图3所示的上下方向依次堆垛而成。其中第一基板1包括本体11和弯折部12,本体11为平板状,其的上下两个面分别用第一背面15和第一正面14表述,第一正面14和第二背面24均为平面,可按需求设计元器件3和布置走线,弯折部12由本体11的四周或者是本体11的第二正面23向下弯折延伸而成,本体11的第一正面14和弯折部12的内侧面共同围合形成一空腔部13,也就是说第一基板1呈大致冂字型结构,空腔部13可以容纳基板上设置的元器件3,从而使得第一基板1在垂直方向与其他第一基板1和/或第二基板2组装时,下层的第一基板1的第一背面15上的元器件3以及该层的第一基板1的第一正面14上的元器件3可以容纳在该第一基板1的空腔部13内,也就是说在基板的正面和背面均可以组装元器件3,从而可以提高封装结构的组装密度,使得封装结构的组装密度可以达到100%,解决了现有技术中采用常规工艺导致组装密度比较低的问题。

21.为了实现上下垂直互连的基板之间能够实现电学和力学的互连,在上层第一基板1的弯折部12的端部、下层第一基板1的弯折部12的端部及下层第一基板1的第一背面15上均设有bga焊点阵列16,在第二基板2的第二正面23上设有bga焊点端子21。bga焊点端子21由第二基板2的第二正面23朝向远离第二背面24的方向凸出延伸也即如图3所示的向上凸出延伸,上下两层第一基板1之间通过bga焊点阵列16焊接互连,下层第一基板1和第二基板2通过bga焊点阵列16和bga焊点端子21焊接互连。具体的,在第一基板1的bga焊点阵列16的焊盘处印刷助焊剂,然后将第一基板1置于回流焊炉中回流,完成焊盘处植球形成gba焊点阵列,同理在第二基板2的bga焊点端子21的焊盘处印刷有助焊剂,然后将第二基板2置于回流焊炉中回流,完成焊盘处植球形成gba焊球凸点端子。bga焊点阵列16和bga焊点端子21不仅作为层间堆叠的力学支撑,同时又作为层间信号互连的通道,另外还可以作为组装对位的对位点,减少组装难度。需要说明的是,上述的第一基板1上的走线是与其上的bga焊点阵列16连接的。

22.为了实现整个封装结构与外部的电连接,在第二基板2的第二背面24也即如图3所示的第二基板2的下表面上设有远离第二背面24方向向外延伸也即如图3所示的向下凸出延伸的外引线22。第二基板2上的走线是与其上的bga焊点端子21连接,外引线22也是与其上的bga焊点端子21连接的。从而实现各层基板组装后各层间信号互连。

23.在一些实施例中,第一基板1的数量还可以为其他,比如一层、三层等等。

24.在一些实施例中,本实施例中的bga焊点端子21为bga焊球凸点端子。

25.在一些实施例中,本实施例中的第一基板1采用ltcc基板也即低温共烧陶瓷基板。

26.在一些实施例中,本实施例中的第二基板2为一体化pga基板。

27.在一些实施例中,本实施例中的外引线22的数量为多个,多个外引线22呈阵列排

布设置在第二基板2的第二背面24上。如图3所示,多个外引线22沿第二基板2的长度方向也即如图3所示的左右方向均匀间隔排布。

28.对于bga焊球凸点端子及bga焊点阵列16的高度及宽度等参数不做详细描述。比如宽度可选为0.4-0.5mm,高度为0.3-0.35mm。

29.本实施还包括一种封装方法,包括以下步骤:在第一基板1的第一正面14上形成有朝向第一背面15凹陷的空腔部13,空腔部13的外周形成为弯折部12;在弯折部12的端部形成bga焊点阵列16;在第二基板2的第二正面23上的面阵i/o端子焊盘上制作出bga焊点端子21;在第二基板2的第二背面24上制作出外引线22;将第一基板1上的bga焊点阵列16与第二基板2上的bga焊点端子21上下压接在一体,实现垂直互连。

30.在一些实施例中,采用smt(surface mounted technology)表面组装工艺实现表面贴装元器件3与第一基板1及第二基板2的物理与电学互连。具体工艺以及工艺参数不做详细描述和限定,为现有常规的smt流程。

31.在一些实施例中,采用置球工艺在所述第二基板2上制作出所述bga焊点端子21。具体的,选取ltcc基板作为承载基板,在ltcc基板底面的面阵i/o端子焊盘上制作出bga焊球凸点端子,在第二背面24上也即如图3所示的下表面上通过钎焊工艺形成有外引线22,从而形成一体化的pga基板。对于钎焊工艺及具体工艺参数在此不做详细描述,为现有常规钎焊工艺。

32.在一些实施例中,外引线22采用钎焊工艺形成在第二基板2的第二背面24上。具体工艺以及工艺参数不做详细描述和限定,为现有常规的钎焊工艺。

33.与传统的封装方式相比,本实施例的封装结构的层间电学和力学的互连一次性成型,减少了焊接梯度和难度,无需层间信号的互连传输焊接和封装焊接工序分开多次焊接。

34.应当理解的是,本发明的上述具体实施方式仅仅用于示例性说明或解释本发明的原理,而不构成对本发明的限制。因此,在不偏离本发明的精神和范围的情况下所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。此外,本发明所附权利要求旨在涵盖落入所附权利要求范围和边界、或者这种范围和边界的等同形式内的全部变化和修改例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1