显示面板的制作方法

1.本技术涉及显示技术领域,具体涉及一种显示面板。

背景技术:

2.有机电致发光技术(organic light emitting diode,oled)是一种新型的显示技术。随着面板制造技术的发展,人们对面板的尺寸要求越来越大,分辨率越来越高,现阶段制造oled屏幕时通常采用蒸镀的方式将oled发光材料蒸镀到玻璃基板上,考虑蒸镀时oled蒸镀掩模版与玻璃基板上金属层之间存在分子间作用力,所以在玻璃基板上制作ps(支撑柱),ps使蒸镀掩模版与玻璃基板上的金属层之间存在较小的gap,但ps受到掩模版的挤压以及摩擦会导致ps出现划伤,在后续的工艺中ps被刮伤的部分会导致封装失效,影响屏体的使用寿命,在进行可靠性实验,ps划伤部位会出现像素失效,出现小黑点。

技术实现要素:

3.有鉴于此,本技术提供一种能够有效的增强支撑柱强度、减少支撑柱划伤,从而减少可靠性测试中出现的小黑点、提高产品的使用寿命的显示面板。

4.本技术提供一种显示面板,包括:

5.阵列基板,包括像素定义层;及

6.支撑柱,形成在所述像素定义层上;所述支撑柱包括支撑柱本体及保护层,所述支撑柱本体及所述保护层均形成在所述像素定义层上,所述保护层包覆所述支撑柱本体;所述支撑柱本体上形成有至少一第一凹槽,部分所述保护层填充在所述第一凹槽内。

7.在本技术一可选实施例中,所述像素定义层包括一第一表面,所述支撑柱形成在所述第一表面上;所述保护层包括第二表面,所述第二表面平行且远离所述第一表面;所述第一凹槽包括第一子槽及第二子槽,所述第一子槽与所述第二子槽相连通,所述第一子槽靠近所述第二表面,所述第二子槽靠近所述第一表面,所述第二子槽的尺寸大于所述第一子槽的尺寸,所述第一子槽在所述第一表面上的垂直投影落在所述第二子槽在所述第一表面上的垂直投影内。

8.在本技术一可选实施例中,所述保护层的材质为氮化硅或氧化硅。

9.在本技术一可选实施例中,所述保护层的材质与所述支撑柱本体的材质不同。

10.在本技术一可选实施例中,所述保护层的材质与所述支撑柱本体的材质相同,所述保护层与所述支撑柱本体一体成型。

11.在本技术一可选实施例中,所述像素定义层还包括至少一第二凹槽,部分所述支撑柱填充在所述第二凹槽内。

12.在本技术一可选实施例中,所述显示面板包括多组所述支撑柱,每组所述支撑柱的高度相同,相邻组的所述支撑柱的高度不同。

13.在本技术一可选实施例中,多组所述支撑柱的高度呈梯度降低。

14.在本技术一可选实施例中,所述支撑柱的组数为3至5组。

15.在本技术一可选实施例中,相邻两组的所述支撑柱的高度差为0.1um至0.5um。

16.本技术提供的显示面板,在ps的支撑柱本体上形成第一凹槽并使得包覆所述支撑柱本体的保护层部分填充在凹槽内,可以增强ps的抗损伤能力,减少ps划伤,提高良率;进一步地,采用氮化硅或氧化硅制作ps,在所述像素定义层上形成第二凹槽,并将部分ps填充在所述第二凹槽内,ps的强度和刚度大大增强,减小ps刮伤的概率,降低ps划伤不良,从而减少可靠性测试中出现的小黑点、提高产品的使用寿命。

附图说明

17.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

18.图1为本技术第一实施例提供的一种显示面板的膜层示意图。

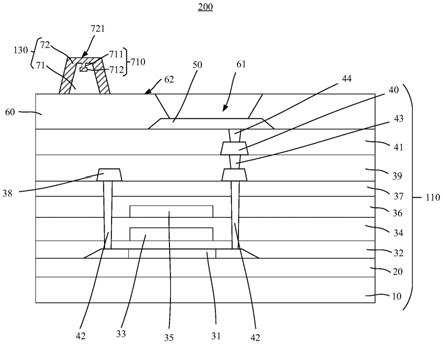

19.图2为本技术第二实施例提供的一种显示面板的膜层示意图。

20.图3为本技术第三实施例提供的一种显示面板的膜层示意图。

21.图4为本技术第四实施例提供的一种显示面板的膜层示意图。

22.图5为本技术第五实施例提供的一种显示面板的膜层示意图。

具体实施方式

23.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

24.在本技术的描述中,需要理解的是,术语“上”、“下”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

25.本技术可以在不同实施中重复参考数字和/或参考字母,这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施方式和/或设置之间的关系。

26.本技术针对现有的显示面板的ps易出现划伤,在后续的工艺中ps被刮伤的部分会导致封装失效,影响屏体的使用寿命,在进行可靠性实验,ps划伤部位会出现像素失效,出现小黑点的技术问题,通过在ps的支撑柱本体上形成第一凹槽并使得包覆所述支撑柱本体的保护层部分填充在凹槽内,可以增强ps的抗损伤能力,减少ps划伤,提高良率;进一步地,采用氮化硅或氧化硅制作ps,在所述像素定义层上形成第二凹槽,并将部分ps填充在所述第二凹槽内,ps的强度和刚度大大增强,减小ps刮伤的概率,降低ps划伤不良,从而减少可靠性测试中出现的小黑点、提高产品的使用寿命。

27.请参阅图1,本技术第一实施例提供了一种显示面板100。所述显示面板100包括阵列基板110及支撑柱120,所述支撑柱120形成在所述阵列基板110的一表面上。

28.具体地,在本实施例中,所述阵列基板110包括衬底10、形成在所述衬底10上的缓冲层20、形成在所述缓冲层20上的有源层31、形成在所述缓冲层20上且包覆所述有源层31的第一层间绝缘层32、形成在所述层间绝缘层32上的第一栅极层33、形成在所述第一栅极层33上的第二层间绝缘层34、形成在所述第二层间绝缘层34上的第二栅极层35、形成在所述第二层间绝缘层34上且包覆所述第二栅极层35的第三层间绝缘层36、形成在所述第三层间绝缘层36上的第四层间绝缘层37、形成在所述第四层间绝缘层37上的第一源漏极层38、形成在所述第四层间绝缘层37上且包覆所述第一源漏极层38的第一平坦层39、形成在所述第一平坦层39上的第二源漏极层40、形成在所述第一平坦层39上且包覆所述第二源漏极层40的第二平坦层41、形成在所述第二平坦层41上的电极层50及形成在所述第二平坦层41上且包覆所述电极层50的像素定义层60。其中,所述第一源漏极层38的源极和漏极分别与所述有源层31的源极区和漏极区电连接。具体地,所述第一源漏极层38的源极和漏极分别通过第一过孔42与所述有源层31的源极区和漏极区电连接。所述第二源漏极层40与所述第一源漏极层38电连接。具体地,所述第二源漏极层40与所述第一源漏极层38通过第二过孔43电连接。所述电极层50与所述第二源漏极层40电连接。具体地,所述电极层50与所述第二源漏极层40通过第三过孔44电连接。

29.在其他实施例中,所述阵列基板110还可以不包括所述缓冲层20。

30.在其他实施例中,所述阵列基板110还可以不包括所述第二源漏极层40。

31.其中,所述像素定义层60上还包括多个像素开口61,部分所述电极层50从所述像素开口61内裸露出来。

32.其中,所述支撑柱120位于所述像素开口61的一侧。所述支撑柱120用于支撑蒸镀掩模版,以使所述蒸镀掩模版与所述阵列基板110上的所述电极层50之间存在较小的间隔,便于将发光材料蒸镀在从所述像素定义开口61裸露出来的所述电极层50上。

33.在本实施例中,所述支撑柱120包括支撑柱本体71及保护层72。所述支撑柱本体71形成在所述像素定义层60上,所述保护层72形成在所述像素定义层60上且包覆所述支撑柱本体71。其中,所述支撑柱本体71的材质即为现有技术中常用的有机树脂材料等。所述保护层72的材质为氮化硅或氧化硅等耐磨损材料。

34.在本实施例中,所述保护层72通过化学气相沉积(chemical vapordeposition,cvd)工艺形成。

35.在本实施例中,所述保护层72的厚度为0.1至0.5um。

36.本实施例提供的显示面板100通过化学气相沉积工艺在所述支撑柱本体71上沉积一耐磨损的保护层72,可以增强所述支撑柱120的抗损伤能力,进而提高所述显示面板100的良率。

37.请参阅图2,本技术第二实施例提供一种显示面板200,所述显示面板200包括阵列基板110及支撑柱130,所述支撑柱130形成在所述阵列基板110的一表面上。

38.具体地,在本实施例中,所述阵列基板110包括衬底10、形成在所述衬底10上的缓冲层20、形成在所述缓冲层20上的有源层31、形成在所述缓冲层20上且包覆所述有源层31的第一层间绝缘层32、形成在所述层间绝缘层32上的第一栅极层33、形成在所述第一栅极

层33上的第二层间绝缘层34、形成在所述第二层间绝缘层34上的第二栅极层35、形成在所述第二层间绝缘层34上且包覆所述第二栅极层35的第三层间绝缘层36、形成在所述第三层间绝缘层36上的第四层间绝缘层37、形成在所述第四层间绝缘层37上的第一源漏极层38、形成在所述第四层间绝缘层37上且包覆所述第一源漏极层38的第一平坦层39、形成在所述第一平坦层39上的第二源漏极层40、形成在所述第一平坦层39上且包覆所述第二源漏极层40的第二平坦层41、形成在所述第二平坦层41上的电极层50及形成在所述第二平坦层41上且包覆所述电极层50的像素定义层60。其中,所述第一源漏极层38的源极和漏极分别与所述有源层31的源极区和漏极区电连接。具体地,所述第一源漏极层38的源极和漏极分别通过第一过孔42与所述有源层31的源极区和漏极区电连接。所述第二源漏极层40与所述第一源漏极层38电连接。具体地,所述第二源漏极层40与所述第一源漏极层38通过第二过孔43电连接。所述电极层50与所述第二源漏极层40电连接。具体地,所述电极层50与所述第二源漏极层40通过第三过孔44电连接。

39.在其他实施例中,所述阵列基板110还可以不包括所述缓冲层20。

40.在其他实施例中,所述阵列基板110还可以不包括所述第二源漏极层40。

41.其中,所述像素定义层60上还包括多个像素开口61,部分所述电极层50从所述像素开口61内裸露出来。

42.其中,所述支撑柱130位于所述像素开口61的一侧。所述支撑柱130用于支撑蒸镀掩模版,以使所述蒸镀掩模版与所述阵列基板110上的所述电极层50之间存在较小的间隔,便于将发光材料蒸镀在从所述像素定义开口61裸露出来的所述电极层50上。

43.所述支撑柱130包括所述保护层72及所述支撑柱本体71,所述支撑柱本体71上形成有一第一凹槽710,部分所述保护层72填充在所述第一凹槽710内。

44.在本实施例中,所述像素定义层60还包括第一表面62,所述支撑柱130形成在所述第一表面62上;所述保护层72包括第二表面721,所述第二表面721平行且远离所述第一表面62。所述第一凹槽710包括第一子槽711及第二子槽712,所述第一子槽711与所述第二子槽712相连通,所述第一子槽711靠近所述第二表面721,所述第二子槽712靠近所述第一表面62,所述第二子槽712的尺寸大于所述第一子槽711的尺寸,所述第一子槽711在所述第一表面62上的垂直投影落在所述第二子槽712在所述第一表面62上的垂直投影内。当然,在其他实施例中,所述第一凹槽710还可以不具有如上所述的结构,可以是截面呈倒梯形、倒三角形等的凹槽。

45.在本实施例中,所述第一凹槽710为半径为3~5um,深度0.1~0.5um的凹坑。

46.在本实施例中,所述保护层72的厚度为0.5~1um的一层氮化硅或氧化硅薄膜。其中,所述保护层72的厚度不包括位于所述第一凹槽710内的保护层的厚度。

47.本实施例提供的显示面板200在所述支撑柱130上方刻蚀出第一凹槽710,并通过cvd工艺进行一层氮化硅或氧化硅沉积,可以增强ps的抗损伤能力,提高所述显示面板200的良率。

48.请参阅图3,本技术第三实施例提供一种显示面板300,所述显示面板300包括阵列基板110及支撑柱140,所述支撑柱140形成在所述阵列基板110的一表面上。

49.具体地,在本实施例中,所述阵列基板110包括衬底10、形成在所述衬底10上的缓冲层20、形成在所述缓冲层20上的有源层31、形成在所述缓冲层20上且包覆所述有源层31

的第一层间绝缘层32、形成在所述层间绝缘层32上的第一栅极层33、形成在所述第一栅极层33上的第二层间绝缘层34、形成在所述第二层间绝缘层34上的第二栅极层35、形成在所述第二层间绝缘层34上且包覆所述第二栅极层35的第三层间绝缘层36、形成在所述第三层间绝缘层36上的第四层间绝缘层37、形成在所述第四层间绝缘层37上的第一源漏极层38、形成在所述第四层间绝缘层37上且包覆所述第一源漏极层38的第一平坦层39、形成在所述第一平坦层39上的第二源漏极层40、形成在所述第一平坦层39上且包覆所述第二源漏极层40的第二平坦层41、形成在所述第二平坦层41上的电极层50及形成在所述第二平坦层41上且包覆所述电极层50的像素定义层60。其中,所述第一源漏极层38的源极和漏极分别与所述有源层31的源极区和漏极区电连接。具体地,所述第一源漏极层38的源极和漏极分别通过第一过孔42与所述有源层31的源极区和漏极区电连接。所述第二源漏极层40与所述第一源漏极层38电连接。具体地,所述第二源漏极层40与所述第一源漏极层38通过第二过孔43电连接。所述电极层50与所述第二源漏极层40电连接。具体地,所述电极层50与所述第二源漏极层40通过第三过孔44电连接。

50.在其他实施例中,所述阵列基板110还可以不包括所述缓冲层20。

51.在其他实施例中,所述阵列基板110还可以不包括所述第二源漏极层40。

52.其中,所述像素定义层60上还包括多个像素开口61,部分所述电极层50从所述像素开口61内裸露出来。

53.其中,所述支撑柱140位于所述像素开口61的一侧。所述支撑柱140用于支撑蒸镀掩模版,以使所述蒸镀掩模版与所述阵列基板110上的所述电极层50之间存在较小的间隔,便于将发光材料蒸镀在从所述像素定义开口61裸露出来的所述电极层50上。

54.其中,所述支撑柱140材质为氮化硅或氧化硅等耐磨损材料。在本实施例中,可以将所述支撑柱140看作如本技术第三实施例的所述支撑柱130的结构,只是本实施例的支撑柱140的保护层和支撑柱本体采用同一种材料制成且支撑柱140的保护层和支撑柱本体一体成型。因此,所述支撑柱140与所述支撑柱130的区别仅在于:所述支撑柱140的支撑柱本体的材质为氮化硅或氧化硅等耐磨损材料。

55.本实施例提供的显示面板300将支撑柱本体和保护层均采用氮化硅或氧化硅等耐磨损材料制成,可以进一步增强ps的抗损伤能力,降低可靠性试验后小黑点的数量,提高所述显示面板300的良率。

56.请参阅图4,本技术第四实施例提供一种显示面板400,所述显示面板400包括阵列基板110及支撑柱150,所述支撑柱150形成在所述阵列基板110的一表面上。

57.具体地,在本实施例中,所述阵列基板110包括衬底10、形成在所述衬底10上的缓冲层20、形成在所述缓冲层20上的有源层31、形成在所述缓冲层20上且包覆所述有源层31的第一层间绝缘层32、形成在所述层间绝缘层32上的第一栅极层33、形成在所述第一栅极层33上的第二层间绝缘层34、形成在所述第二层间绝缘层34上的第二栅极层35、形成在所述第二层间绝缘层34上且包覆所述第二栅极层35的第三层间绝缘层36、形成在所述第三层间绝缘层36上的第四层间绝缘层37、形成在所述第四层间绝缘层37上的第一源漏极层38、形成在所述第四层间绝缘层37上且包覆所述第一源漏极层38的第一平坦层39、形成在所述第一平坦层39上的第二源漏极层40、形成在所述第一平坦层39上且包覆所述第二源漏极层40的第二平坦层41、形成在所述第二平坦层41上的电极层50及形成在所述第二平坦层41上

且包覆所述电极层50的像素定义层60。其中,所述第一源漏极层38的源极和漏极分别与所述有源层31的源极区和漏极区电连接。具体地,所述第一源漏极层38的源极和漏极分别通过第一过孔42与所述有源层31的源极区和漏极区电连接。所述第二源漏极层40与所述第一源漏极层38电连接。具体地,所述第二源漏极层40与所述第一源漏极层38通过第二过孔43电连接。所述电极层50与所述第二源漏极层40电连接。具体地,所述电极层50与所述第二源漏极层40通过第三过孔44电连接。

58.在其他实施例中,所述阵列基板110还可以不包括所述缓冲层20。

59.在其他实施例中,所述阵列基板110还可以不包括所述第二源漏极层40。

60.其中,所述像素定义层60上还包括多个像素开口61,部分所述电极层50从所述像素开口61内裸露出来。

61.其中,所述支撑柱150位于所述像素开口61的一侧。所述支撑柱150用于支撑蒸镀掩模版,以使所述蒸镀掩模版与所述阵列基板110上的所述电极层50之间存在较小的间隔,便于将发光材料蒸镀在从所述像素定义开口61裸露出来的所述电极层50上。

62.其中,所述像素定义层60上开设有至少一第二凹槽63,部分所述支撑柱150填充在所述第二凹槽63内。

63.在本实施例中,所述第二凹槽63为半径为10~20um,深度为0.5~1.5um的凹槽。

64.在本实施例中,所述支撑柱150的厚度为1至2um。其中,所述支撑柱150的厚度不包括填充在所述第二凹槽63内的支撑柱的厚度。

65.本实施例提供的显示面板400将支撑柱本体和保护层均采用氮化硅或氧化硅等耐磨损材料制成,并在像素定义层60上形成第二凹槽,部分支撑柱150填充在所述第二凹槽63内,可以大大增强ps的强度和刚度,从而能够减小ps被刮伤的概率,进而能够降低可靠性试验后小黑点的数量,提高所述显示面板400的良率。

66.请参阅图5,本技术第五实施例提供一种显示面板500,所述显示面板500包括阵列基板110及支撑柱160,所述支撑柱160形成在所述阵列基板110的一表面上。

67.具体地,在本实施例中,所述阵列基板110包括衬底10、形成在所述衬底10上的缓冲层20、形成在所述缓冲层20上的有源层31、形成在所述缓冲层20上且包覆所述有源层31的第一层间绝缘层32、形成在所述层间绝缘层32上的第一栅极层33、形成在所述第一栅极层33上的第二层间绝缘层34、形成在所述第二层间绝缘层34上的第二栅极层35、形成在所述第二层间绝缘层34上且包覆所述第二栅极层35的第三层间绝缘层36、形成在所述第三层间绝缘层36上的第四层间绝缘层37、形成在所述第四层间绝缘层37上的第一源漏极层38、形成在所述第四层间绝缘层37上且包覆所述第一源漏极层38的第一平坦层39、形成在所述第一平坦层39上的第二源漏极层40、形成在所述第一平坦层39上且包覆所述第二源漏极层40的第二平坦层41、形成在所述第二平坦层41上的电极层50及形成在所述第二平坦层41上且包覆所述电极层50的像素定义层60。其中,所述第一源漏极层38的源极和漏极分别与所述有源层31的源极区和漏极区电连接。具体地,所述第一源漏极层38的源极和漏极分别通过第一过孔42与所述有源层31的源极区和漏极区电连接。所述第二源漏极层40与所述第一源漏极层38电连接。具体地,所述第二源漏极层40与所述第一源漏极层38通过第二过孔43电连接。所述电极层50与所述第二源漏极层40电连接。具体地,所述电极层50与所述第二源漏极层40通过第三过孔44电连接。

68.在其他实施例中,所述阵列基板110还可以不包括所述缓冲层20。

69.在其他实施例中,所述阵列基板110还可以不包括所述第二源漏极层40。

70.其中,所述像素定义层60上还包括多个像素开口61,部分所述电极层50从所述像素开口61内裸露出来。

71.其中,所述支撑柱160位于所述像素开口61的一侧。所述支撑柱160用于支撑蒸镀掩模版,以使所述蒸镀掩模版与所述阵列基板110上的所述电极层50之间存在较小的间隔,便于将发光材料蒸镀在从所述像素定义开口61裸露出来的所述电极层50上。

72.其中,所述显示面板500包括多组支撑柱160,每组所述支撑柱160的高度相同,相邻组的所述支撑柱160的高度不同。

73.在本技术一可选实施例中,多组所述支撑柱160的高度呈梯度降低。

74.在本技术一可选实施例中,所述支撑柱160的组数为3至5组。

75.在本技术一可选实施例中,相邻两组的所述支撑柱160的高度差为0.1um至0.5um。

76.当然,本实施例中的支撑柱的排列方式还适用于实施例1至实施例4。

77.由于当支撑柱160受到的挤压力达到一定度时,支撑柱160会被划伤,因此,本实施例提供的显示面板500将相邻组的支撑柱160呈梯度降低排列,通过调控相邻的支撑柱160之间的高度差可以缓解较高的支撑柱160受到的压力,可以降低ps受损伤的机率,进而降低可靠性试验后小黑点的数量,提高所述显示面板500的良率。

78.以上对本技术的实施例所提供的显示面板进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1