带通滤波器的制作方法

1.本发明涉及一种包括多个谐振器的带通滤波器。

背景技术:

2.目前,开始提供使用了第五代移动通信系统(以下称为5g。)的通信服务。5g中,假定使用10ghz以上的频带,特别是10~30ghz的亚毫米波波段或30~300ghz的毫米波波段。

3.作为用于通信装置的电子部件之一,有具备多个谐振器的带通滤波器。多个谐振器分别具有例如在一方向上较长的导体部。特别是在用于小型的通信装置的带通滤波器中要求小型化。

4.在日本专利申请公开平10-209708号公报中公开了如下带通滤波器:其配置为形成有两个一端接地且另一端开放的u字型带状线谐振器,且u字型带状线谐振器的接地侧彼此相邻。在日本专利申请公开特开2004-266696号公报中公开了如下带通滤波器:其配置为形成有两个一端开放且另一端短路的

コ

字型的谐振器电极,且谐振器电极的开放端侧彼此相邻。在日本专利申请公开平10-209708号公报、日本专利申请公开特开2004-266696号公报所公开的带通滤波器中,通过将构成谐振器的导体折弯,将带通滤波器小型化。

5.在中国专利申请公开第110970695a号说明书中公开了如下带通滤波器:其形成有直线形状的谐振器,该直线形状的谐振器具有包括窄幅部和位于窄幅部的两侧的两个宽幅部的谐振器导体部。上述结构的谐振器是阶梯阻抗谐振器(以下也记为sir。)的一种。中国专利申请公开第110970695a号说明书的谐振器是两端开放型的1/2波长谐振器。

6.在包括多个1/2波长谐振器的带通滤波器中,因为1/2波长谐振器长,所以存在难以小型化等的问题。在中国专利申请公开第110970695a号说明书中,通过使用sir缩短谐振器导体部,将带通滤波器小型化。但是,从小型化的观点看,在该带通滤波器中有改善的余地。

技术实现要素:

7.本发明的目的在于,提供一种包括多个两端开放型谐振器的带通滤波器,其能够小型化。

8.本发明的带通滤波器具备:第一输入输出端口;第二输入输出端口;多个谐振器,其在电路结构上设置于第一输入输出端口和第二输入输出端口之间,且构成为在电路结构上相邻的两个谐振器电磁耦合;层叠体,其用于将第一输入输出端口、第二输入输出端口及多个谐振器一体化。层叠体包括层叠的多个电介质层。

9.多个谐振器分别是由层叠体内的导体的线路构成的两端开放型谐振器。多个谐振器中的至少一个具有谐振器导体部,所述谐振器导体部包括配置于在与多个电介质层的层叠方向正交的方向上相互分离的位置的第一线路部分及第二线路部分和将第一线路部分和第二线路部分连接的第三线路部分。第一至第三线路部分以包围第一线路部分和第二线路部分之间的空间的方式延伸。

10.在本发明的带通滤波器中,多个谐振器也可以包括在电路结构上最靠近第一输入输出端口的第一谐振器、在电路结构上最靠近第二输入输出端口的第二谐振器、以及在电路结构上设置于第一谐振器和第二谐振器之间的至少一个中间谐振器。在该情况下,第一及第二谐振器也可以分别具有所述谐振器导体部。另外,第一谐振器的所述谐振器导体部的第三线路部分和第二谐振器的所述谐振器导体部的第三线路部分也可以相邻且分别沿着与层叠方向正交的相同的方向延伸。

11.另外,在多个谐振器包括至少一个中间谐振器的情况下,至少一个中间谐振器也可以是多个中间谐振器。在该情况下,多个中间谐振器中的至少一个也可以具有所述谐振器导体部。或者,至少一个中间谐振器也可以是第三谐振器、第四谐振器及第五谐振器。第四谐振器在电路结构上设置于第三谐振器和第五谐振器之间。在该情况下,第三及第五谐振器也可以分别具有所述谐振器导体部。

12.另外,本发明的带通滤波器也可以还具备至少一个电容器。在该情况下,第一及第二线路部分也可以分别具有处于在所述谐振器导体部的长边方向上距第三线路部分最远的位置的端部。至少一个电容器也可以在长边方向上朝向第三线路部与所述端部分离的位置上与所述谐振器导体部连接。

13.另外,在本发明的带通滤波器中,第一线路部分也可以包括短边方向的尺寸恒定的第一宽度恒定部分,第二线路部分也可以包括短边方向的尺寸恒定的第二宽度恒定部分。在该情况下,第三线路部分的短边方向的尺寸也可以小于第一及第二宽度恒定部分各自的短边方向的尺寸。

14.在本发明的带通滤波器中,多个谐振器中的至少一个具有谐振器导体部,该谐振器导体部包括配置于在与多个电介质层的层叠方向正交的方向上相互分离的位置的第一线路部分及第二线路部分和将第一线路部分和第二线路部分连接的第三线路部分。第一至第三线路部分以包围第一线路部分和第二线路部分之间的空间的方式延伸。由此,根据本发明的带通滤波器,能够实现小型化。

15.通过以下的说明,本发明的其他目的、特征及利益变得显而易见。

附图说明

16.图1是表示本发明的第一实施方式的带通滤波器的结构的立体图。

17.图2是表示本发明的第一实施方式的带通滤波器的电路结构的电路图。

18.图3是表示图1所示的层叠体中的第一层电介质层的图案形成面的说明图。

19.图4是表示图1所示的层叠体中的第二层电介质层的图案形成面的说明图。

20.图5是表示图1所示的层叠体中的第三层电介质层的图案形成面的说明图。

21.图6是表示图1所示的层叠体中的第四层电介质层的图案形成面的说明图。

22.图7是表示图1所示的层叠体中的第五层及第六层电介质层的图案形成面的说明图。

23.图8是表示图1所示的层叠体中的第七层电介质层的图案形成面的说明图。

24.图9是表示图1所示的层叠体中的第八层电介质层的图案形成面的说明图。

25.图10是表示图1所示的层叠体中的第九层电介质层的图案形成面的说明图。

26.图11是表示图1所示的层叠体中的第十层至第十七层电介质层的图案形成面的说

明图。

27.图12是表示图1所示的层叠体中的第十八层电介质层的图案形成面的说明图。

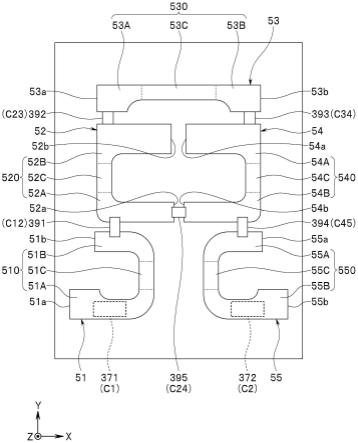

28.图13是表示本发明的第一实施方式的带通滤波器的主要部分的俯视图。

29.图14是表示通过模拟求出的带通滤波器的插入损失及反射损失的频率特性的一个例子的特性图。

30.图15是放大表示图14所示的插入损失的频率特性的一部分的特性图。

31.图16是放大表示图14所示的反射损失的频率特性的一部分的特性图。

32.图17是表示本发明的第二实施方式的带通滤波器的结构的立体图。

33.图18是表示本发明的第二实施方式中的第八层电介质层的图案形成面的说明图。

34.图19是表示本发明的第二实施方式的带通滤波器的主要部分的俯视图。

具体实施方式

35.[第一实施方式]

[0036]

以下,参照附图对本发明的实施方式详细地进行说明。首先,参照图1及图2,对本发明的第一实施方式的带通滤波器的结构进行说明。图1是表示本实施方式的带通滤波器的结构的立体图。图2是表示本实施方式的带通滤波器的电路结构的电路图。

[0037]

如图1及图2所示,本实施方式的带通滤波器1具备第一输入输出端口3、第二输入输出端口4、构成为在电路结构上相邻的两个谐振器电磁耦合的多个谐振器、以及用于将第一输入输出端口3、第二输入输出端口4及多个谐振器一体化的层叠体2。层叠体2包括层叠的多个电介质层。多个谐振器分别是由层叠体2内的导体的线路构成的两端开放型谐振器且是1/2波长谐振器。此外,在本技术中,“电路结构上”这样的表达用于指电路图上的配置,而不是物理结构中的配置。

[0038]

在此,如图1所示,定义x方向、y方向及z方向。x方向、y方向及z方向相互正交。在本实施方式中,将多个电介质层的层叠方向(在图1中朝向上侧的方向)设为z方向。另外,将与x方向相反的方向设为-x方向,将与y方向相反的方向设为-y方向,将与z方向相反的方向设为-z方向。

[0039]

层叠体2具有长方体形状。层叠体2具有位于z方向上的层叠体2的两端的下表面2a及上表面2b和将下表面2a和上表面2b连接的四个侧面2c、2d、2e、2f。下表面2a位于层叠体2中的-z方向的一端。上表面2b位于层叠体2中的z方向的一端。侧面2c位于层叠体2中的-x方向的一端。侧面2d位于层叠体2中的x方向的一端。侧面2e位于层叠体2中的-y方向的一端。侧面2f位于层叠体2中的y方向的一端。

[0040]

多个谐振器在电路结构上设置于第一输入输出端口3和第二输入输出端口4之间。如图2所示,在本实施方式中,特别是多个谐振器是五个谐振器51、52、53、54、55。五个谐振器51、52、53、54、55在电路结构上从第一输入输出端口3侧依次配置。谐振器51在电路结构上最靠近第一输入输出端口3,谐振器55在电路结构上最靠近第二输入输出端口4。谐振器51与本发明中的“第一谐振器”对应。谐振器55与本发明中的“第二谐振器”对应。

[0041]

谐振器52~54在电路结构上设置于谐振器51和谐振器55之间。谐振器52~54与本发明中的“中间谐振器”对应。谐振器53在电路结构上设置于谐振器52和谐振器54之间。谐振器52与本发明中的“第三谐振器”对应。谐振器53与本发明中的“第四谐振器”对应。谐振

器54与本发明中的“第五谐振器”对应。

[0042]

谐振器51~55构成为:谐振器51、52在电路结构上相邻且电磁耦合,谐振器52、53在电路结构上相邻且电磁耦合,谐振器53、54在电路结构上相邻且电磁耦合,谐振器54、55在电路结构上相邻且电磁耦合。另外,在本实施方式中,特别是在电路结构上相邻的两个谐振器之间的电磁耦合是电容耦合。

[0043]

带通滤波器1具备实现谐振器51、52之间的电容耦合的电容器c12、实现谐振器52、53之间的电容耦合的电容器c23、实现谐振器53、54之间的电容耦合的电容器c34、以及实现谐振器54、55之间的电容耦合的电容器c45。

[0044]

在此,将具备构成为在电路结构上相邻的两个谐振器耦合的三个以上的谐振器的带通滤波器中的、在电路结构上不相邻的两个谐振器之间的电磁耦合称为交叉耦合。本实施方式的带通滤波器1如以下所述具有两个交叉耦合。

[0045]

在本实施方式中,五个谐振器51~55中在电路结构上最靠近第一输入输出端口3的谐振器51和五个谐振器51~55中在电路结构上最靠近第二输入输出端口4的谐振器55在电路结构上不相邻,但磁耦合。

[0046]

另外,在本实施方式中,五个谐振器51~55中在电路结构上第二靠近第一输入输出端口3的谐振器52和五个谐振器51~55中在电路结构上第二靠近第二输入输出端口4的谐振器54在电路结构上不相邻,但电容耦合。带通滤波器1还具备实现谐振器52、54之间的电容耦合的电容器c24。

[0047]

带通滤波器1还具备设置于第一输入输出端口3和谐振器51之间的电容器c1和设置于第二输入输出端口4和谐振器55之间的电容器c2。

[0048]

带通滤波器1还具备屏蔽6、第一分隔部7以及第二分隔部8。屏蔽6由导体构成,与层叠体2一体化。另外,屏蔽6接地。屏蔽6具有防止电磁波向带通滤波器1的周围放射的功能。屏蔽6配置为包围五个谐振器。第一分隔部7和第二分隔部8分别由导体构成,设置于层叠体2内,与屏蔽6电连接。

[0049]

第一分隔部7沿z方向延伸。另外,第一分隔部7贯通构成层叠体2的两个以上的电介质层。第一分隔部7具有抑制te模式的功能。在本实施方式中,第一分隔部7包括分别贯通构成层叠体2的两个以上的电介质层的多个第一通孔列。在图1中,由圆柱表示各个第一通孔列。多个第一通孔列分别包括串联连接的两个以上的通孔。多个第一通孔列分别沿z方向延伸。另外,多个第一通孔列以沿y方向排列的方式排列。在本实施方式中,第一通孔列的数量是四个。

[0050]

第二分隔部8沿z方向延伸。另外,第二分隔部8贯通构成层叠体2的两个以上的电介质层。在本实施方式中,第二分隔部8包括分别贯通构成层叠体2的两个以上的电介质层的多个第二通孔列。在图1中,由圆柱表示各个第二通孔列。多个第二通孔列分别包括串联连接的两个以上的通孔。多个第二通孔列分别沿z方向延伸。另外,多个第二通孔列以沿x方向排列的方式排列。在本实施方式中,第二通孔列的数量是四个。

[0051]

接下来,参照图1及图2,对谐振器51~55的结构详细地进行说明。谐振器51、52、53、54、55分别具有谐振器导体部510、520、530、540、550。谐振器导体部510、520、530、540、550分别沿与多个电介质层的层叠方向即z方向正交的方向延伸。

[0052]

如上所述,谐振器51~55分别是两端开放型谐振器。因此,谐振器导体部510、520、

530、540、550各自的两端开放。谐振器导体部510、520、530、540、550分别具有与带通滤波器1的通带的中心频率对应的波长的1/2或与其接近的长度。

[0053]

谐振器导体部510、520、530、540、550分别包括配置于在与z方向正交的方向上相互分离的位置的第一线路部分及第二线路部分和将第一线路部分和第二线路部分连接的第三线路部分。

[0054]

以下,分别使用符号51a、51b、51c表示谐振器导体部510的第一线路部分、第二线路部分及第三线路部分。另外,分别使用符号52a、52b、52c表示谐振器导体部520的第一线路部分、第二线路部分及第三线路部分。另外,分别使用符号53a、53b、53c表示谐振器导体部530的第一线路部分、第二线路部分及第三线路部分。另外,分别使用符号54a、54b、54c表示谐振器导体部540的第一线路部分、第二线路部分及第三线路部分。另外,分别使用符号55a、55b、55c表示谐振器导体部550的第一线路部分、第二线路部分及第三线路部分。

[0055]

接下来,参照图3至图12,对构成层叠体2的多个电介质层和形成于该多个电介质层的多个导体层及多个通孔的结构的一个例子进行说明。在该例中,层叠体2具有层叠的十八层电介质层。以下,将该十八层电介质层从下依次称为第一层至第十八层电介质层。另外,由符号31~48表示第一层至第十八层电介质层。在图3至图12中,多个圆表示多个通孔。

[0056]

图3表示第一层电介质层31的图案形成面。在电介质层31的图案形成面形成有构成第一输入输出端口3的导体层311、构成第二输入输出端口4的导体层312、以及构成屏蔽6的导体层313、314、315、316。

[0057]

另外,在电介质层31形成有与导体层311连接的通孔31t1、与导体层312连接的通孔31t2、以及构成屏蔽6的多个通孔6t1。在图3中,由标注符号6t1的圆表示多个通孔6t1中的任意一个,由未标注符号的多个圆表示其他通孔6t1。此外,在用于之后的说明的与图3同样的图中,也对构成屏蔽6的多个通孔使用与图3同样的表示方式。多个通孔6t1分别与导体层313~316中的任一个连接。

[0058]

图4表示第二层电介质层32的图案形成面。在电介质层32的图案形成面形成有构成屏蔽6的导体层321。

[0059]

另外,在电介质层32形成有通孔32t1、32t2。图3所示的通孔31t1、31t2分别与通孔32t1、32t2连接。

[0060]

在电介质层32还形成有构成屏蔽6的多个通孔6t2、构成第一分隔部7的四个通孔7t2、以及构成第二分隔部8的四个通孔8t2。多个通孔6t2的一部分、四个通孔7t2、四个通孔8t2以及图3所示的多个通孔6t1的一部分与导体层321连接。多个通孔6t2中未与导体层321连接的多个通孔与多个通孔6t1中未与导体层321连接的多个通孔连接。

[0061]

图5表示第三层电介质层33的图案形成面。在电介质层33形成有通孔33t1、33t2。图4所示的通孔32t1、32t2分别与通孔33t1、33t2连接。

[0062]

在电介质层33还形成有构成屏蔽6的多个通孔6t3、构成第一分隔部7的四个通孔7t3、以及构成第二分隔部8的四个通孔8t3。图4所示的多个通孔6t2与多个通孔6t3连接。图4所示的四个通孔7t2与四个通孔7t3连接。图4所示的四个通孔8t2与四个通孔8t3连接。

[0063]

图6表示第四层电介质层34的图案形成面。在电介质层34的图案形成面形成有两个导体层341、342。图5所示的通孔33t1与导体层341连接。图5所示的通孔33t2与导体层342连接。

[0064]

另外,在电介质层34形成有与导体层341连接的通孔34t1和与导体层342连接的通孔34t2。

[0065]

在电介质层34还形成有构成屏蔽6的多个通孔6t4、构成第一分隔部7的四个通孔7t4、以及构成第二分隔部8的四个通孔8t4。图5所示的多个通孔6t3与多个通孔6t4连接。图5所示的四个通孔7t3与四个通孔7t4连接。图5所示的四个通孔8t3与四个通孔8t4连接。

[0066]

图7表示第五层及第六层电介质层35、36的图案形成面。在电介质层35、36的各个形成有通孔35t1、35t2。图6所示的通孔34t1、34t2分别与形成于第五层电介质层35的通孔35t1、35t2连接。

[0067]

在电介质层35、36的各个还形成有构成屏蔽6的多个通孔6t5、构成第一分隔部7的四个通孔7t5、以及构成第二分隔部8的四个通孔8t5。图6所示的多个通孔6t4与形成于第五层电介质层35的多个通孔6t5连接。图6所示的四个通孔7t4与形成于第五层电介质层35的四个通孔7t5连接。图6所示的四个通孔8t4与形成于第五层电介质层35的四个通孔8t5连接。

[0068]

另外,在电介质层35、36中,上下相邻的相同符号的通孔彼此相互连接。

[0069]

图8表示第七层电介质层37的图案形成面。在电介质层37的图案形成面形成有用于构成图2所示的电容器c1的导体层371和用于构成图2所示的电容器c2的导体层372。在导体层371连接有形成于第六层电介质层36的通孔35t1。在导体层372连接有形成于第六层电介质层36的通孔35t2。

[0070]

另外,在电介质层37形成有构成屏蔽6的多个通孔6t7、构成第一分隔部7的四个通孔7t7、以及构成第二分隔部8的四个通孔8t7。形成于第六层电介质层36的多个通孔6t5与多个通孔6t7连接。形成于第六层电介质层36的四个通孔7t5与四个通孔7t7连接。形成于第六层电介质层36的四个通孔8t5与四个通孔8t7连接。

[0071]

图9表示第八层电介质层38的图案形成面。在电介质层38的图案形成面形成有分别由导体的线路构成的谐振器导体部510、520、530、540、550。稍后对谐振器导体部510、520、530、540、550的形状及配置详细地进行说明。

[0072]

另外,在电介质层38形成有构成屏蔽6的多个通孔6t8、构成第一分隔部7的四个通孔7t8、以及构成第二分隔部8的四个通孔8t8。多个通孔6t8配置于谐振器导体部510、520、530、540、550的周围。四个通孔7t8配置于谐振器导体部510和谐振器导体部550之间。四个通孔8t8配置于由谐振器导体部520、540包围的空间。图8所示的多个通孔6t7与多个通孔6t8连接。图8所示的四个通孔7t7与四个通孔7t8连接。图8所示的四个通孔8t7与四个通孔8t8连接。

[0073]

图10表示第九层电介质层39的图案形成面。在电介质层39的图案形成面形成有用于分别构成图2所示的电容器c12、c23、c34、c45、c24的导体层391、392、393、394、395。

[0074]

另外,在电介质层39形成有构成屏蔽6的多个通孔6t9、构成第一分隔部7的四个通孔7t9、以及构成第二分隔部8的四个通孔8t9。图9所示的多个通孔6t8与多个通孔6t9连接。图9所示的四个通孔7t8与四个通孔7t9连接。图9所示的四个通孔8t8与四个通孔8t9连接。

[0075]

图11表示第十层至第十七层电介质层40~47的图案形成面。在电介质层40~47的各个形成有构成屏蔽6的多个通孔6t10、构成第一分隔部7的四个通孔7t10、以及构成第二分隔部8的四个通孔8t10。图10所示的多个通孔6t9与形成于第十层电介质层40的多个通孔

6t10连接。图10所示的四个通孔7t9与形成于第十层电介质层40的四个通孔7t10连接。图10所示的四个通孔8t9与形成于第十层电介质层40的四个通孔8t10连接。

[0076]

在电介质层40~47中,上下相邻的相同符号的通孔彼此相互连接。

[0077]

图12表示第十八层电介质层48的图案形成面。在电介质层48的图案形成面形成有构成屏蔽6的导体层481。形成于第十七层电介质层47的通孔6t10、7t10、8t10与导体层481连接。

[0078]

本实施方式的带通滤波器1以第一层电介质层31的图案形成面成为层叠体2的下表面2a的方式层叠第一层至第十八层电介质层31~48而构成。第十八层电介质层48中的图案形成面的相反侧的面成为层叠体2的上表面2b。

[0079]

接下来,参照图13,对谐振器导体部510、520、530、540、550的形状及配置进行说明。图13是表示带通滤波器1的主要部分的俯视图。谐振器51~55各自的谐振器导体部510、520、530、540、550在z方向上配置于层叠体2内的相同位置。

[0080]

谐振器导体部510包括配置于在y方向上分离的位置的第一线路部分51a及第二线路部分51b和将第一线路部分51a和第二线路部分51b连接的第三线路部分51c。在图13中,分别由虚线表示第一线路部分51a和第三线路部分51c的边界、第二线路部分51b和第三线路部分51c的边界。第一至第三线路部分51a~51c以包围第一线路部分51a和第二线路部分51b之间的空间的方式延伸。具体而言,从z方向观察,谐振器导体部510的整体即第一至第三线路部分51a~51c具有包围上述空间的u字形状。第一及第二线路部分51a、51b各自的大部分沿着x方向延伸。第三线路部分51c沿着y方向延伸。

[0081]

第一线路部分51a具有处于在谐振器导体部510的长边方向上距第三线路部分51c最远的位置的端部51a。第二线路部分51b具有处于在谐振器导体部510的长边方向上距第三线路部分51c最远的位置的端部51b。

[0082]

在此,将各线路部分的短边方向的尺寸称为宽度。第一线路部分51a包括宽度恒定的第一宽度恒定部分。第二线路部分51b包括宽度恒定的第二宽度恒定部分。第三线路部分51c的宽度小于第一及第二宽度恒定部分各自的宽度。在本实施方式中,特别是第一线路部分51a包括包含端部51a的部分和位于该部分和第三线路部分51c之间的部分来作为第一宽度恒定部分。第二宽度恒定部分包括端部51b。第三线路部分51c的宽度与第三线路部分51c的长边方向的位置无关,是恒定的。另外,第三线路部分51c的宽度小于第一线路部分51a的最大宽度及第二线路部分51b的最大宽度,且与第一线路部分51a的最小宽度及第二线路部分51b的最小宽度相等。

[0083]

谐振器导体部520包括配置于在y方向上分离的位置的第一线路部分52a及第二线路部分52b和将第一线路部分52a和第二线路部分52b连接的第三线路部分52c。在图13中,分别由虚线表示第一线路部分52a和第三线路部分52c的边界、第二线路部分52b和第三线路部分52c的边界。第一至第三线路部分52a~52c以包围第一线路部分52a和第二线路部分52b之间的空间的方式延伸。具体而言,从z方向观察,谐振器导体部520的整体即第一至第三线路部分52a~52c具有包围上述空间的u字形状。第一及第二线路部分52a、52b各自的大部分沿着x方向延伸。第三线路部分52c沿着y方向延伸。

[0084]

第一线路部分52a具有处于在谐振器导体部520的长边方向上距第三线路部分52c最远的位置的端部52a。第二线路部分52b具有处于在谐振器导体部520的长边方向上距第

三线路部分52c最远的位置的端部52b。

[0085]

第一线路部分52a包括宽度恒定的第一宽度恒定部分。第二线路部分52b包括宽度恒定的第二宽度恒定部分。第三线路部分52c的宽度小于第一及第二宽度恒定部分各自的宽度。在本实施方式中,特别是第一宽度恒定部分包括端部52a。第二宽度恒定部分包括端部52b。第三线路部分52c的宽度与第三线路部分52c的长边方向的位置无关,是恒定的。另外,第三线路部分52c的宽度小于第一线路部分52a的最大宽度及第二线路部分52b的最大宽度,且与第一线路部分52a的最小宽度及第二线路部分52b的最小宽度相等。

[0086]

谐振器导体部530包括配置于在x方向上分离的位置的第一线路部分53a及第二线路部分53b和将第一线路部分53a和第二线路部分53b连接的第三线路部分53c。在图13中,分别由虚线表示第一线路部分53a和第三线路部分53c的边界、第二线路部分53b和第三线路部分53c的边界。谐振器导体部530的整体即第一至第三线路部分53a~53c沿着x方向延伸。

[0087]

第一线路部分53a具有处于在谐振器导体部530的长边方向上距第三线路部分53c最远的位置的端部53a。第二线路部分53b具有处于在谐振器导体部530的长边方向上距第三线路部分53c最远的位置的端部53b。

[0088]

第一线路部分53a包括宽度恒定的第一宽度恒定部分。第二线路部分53b包括宽度恒定的第二宽度恒定部分。第三线路部分53c的宽度小于第一及第二宽度恒定部分各自的宽度。在本实施方式中,特别是第一宽度恒定部分包括端部53a。第二宽度恒定部分包括端部53b。第三线路部分53c的宽度与第三线路部分53c的长边方向的位置无关,是恒定的。另外,第三线路部分53c的宽度小于第一线路部分53a的最大宽度及第二线路部分53b的最大宽度,且与第一线路部分53a的最小宽度及第二线路部分53b的最小宽度相等。

[0089]

谐振器导体部520和谐振器导体部540具有相对于yz平面对称的形状。如果将对谐振器导体部520的第一至第三线路部分52a~52c的说明中的谐振器导体部520、第一线路部分52a、第二线路部分52b及第三线路部分52c分别替换成谐振器导体部540、第一线路部分54a、第二线路部分54b及第三线路部分54c,则成为对谐振器导体部540的第一至第三线路部分54a~54c的说明。

[0090]

第一线路部分54a具有处于在谐振器导体部540的长边方向上距第三线路部分54c最远的位置的端部54a。第二线路部分54b具有处于在谐振器导体部540的长边方向上距第三线路部分54c最远的位置的端部54b。

[0091]

第一线路部分54a包括宽度恒定的第一宽度恒定部分。第二线路部分54b包括宽度恒定的第二宽度恒定部分。第三线路部分54c的宽度小于第一及第二宽度恒定部分各自的宽度。在本实施方式中,特别是第一宽度恒定部分包括端部54a。第二宽度恒定部分包括端部54b。第三线路部分54c的宽度与第三线路部分54c的长边方向的位置无关,是恒定的。另外,第三线路部分54c的宽度小于第一线路部分54a的最大宽度及第二线路部分52b的最大宽度,且与第一线路部分54a的最小宽度及第二线路部分54b的最小宽度相等。

[0092]

谐振器导体部510和谐振器导体部550具有相对于yz平面对称的形状。如果将对谐振器导体部510的第一至第三线路部分51a~51c的说明中的谐振器导体部510、第一线路部分51a、第二线路部分51b及第三线路部分51c分别替换成谐振器导体部550、第一线路部分55a、第二线路部分55b及第三线路部分55c,则成为对谐振器导体部550的第一至第三线路

部分55a~55c的说明。

[0093]

第一线路部分55a具有处于在谐振器导体部550的长边方向上距第三线路部分55c最远的位置的端部55a。第二线路部分55b具有处于在谐振器导体部550的长边方向上距第三线路部分55c最远的位置的端部55b。

[0094]

第一线路部分55a包括宽度恒定的第一宽度恒定部分。第二线路部分55b包括宽度恒定的第二宽度恒定部分。第三线路部分55c的宽度小于第一及第二宽度恒定部分各自的宽度。在本实施方式中,特别是第一宽度恒定部分包括端部55a。第二线路部分55b包括包含端部55b的部分和位于该部分和第三线路部分55c之间的部分来作为第二宽度恒定部分。第三线路部分55c的宽度与第三线路部分55c的长边方向的位置无关,是恒定的。另外,第三线路部分55c的宽度小于第一线路部分55a的最大宽度及第二线路部分55b的最大宽度,且与第一线路部分55a的最小宽度及第二线路部分55b的最小宽度相等。

[0095]

谐振器导体部550配置于谐振器导体部510的x方向的前端。谐振器导体部520、540分别配置于谐振器导体部510、550的y方向的前端。谐振器导体部530配置于谐振器导体部520、540的y方向的前端。

[0096]

在谐振器导体部510中,第二线路部分51b配置于第一线路部分51a的y方向的前端。在谐振器导体部520中,第二线路部分52b配置于第一线路部分52a的y方向的前端。在谐振器导体部530中,第二线路部分53b配置于第一线路部分53a的x方向的前端。在谐振器导体部540中,第二线路部分54b配置于第一线路部分54a的-y方向的前端。在谐振器导体部550中,第二线路部分55b配置于第一线路部分55a的-y方向的前端。

[0097]

谐振器导体部510的第二线路部分51b和谐振器导体部520的第一线路部分52a相邻且通过电容器c12耦合。谐振器导体部520的第二线路部分52b和谐振器导体部530的第一线路部分53a相邻且通过电容器c23耦合。谐振器导体部530的第二线路部分53b和谐振器导体部540的第一线路部分54a相邻且通过电容器c34耦合。谐振器导体部540的第二线路部分54b和谐振器导体部550的第一线路部分55a相邻且通过电容器c45耦合。

[0098]

谐振器导体部510的第三线路部分51c和谐振器导体部550的第三线路部分55c相邻且分别沿着y方向延伸。由此,谐振器51和谐振器55磁耦合。

[0099]

谐振器导体部520的第一线路部分52a和谐振器导体部540的第二线路部分54b以端部52a和端部54b沿x方向相邻的方式配置且通过电容器c24耦合。谐振器导体部520的第二线路部分52b和谐振器导体部540的第一线路部分54a以端部52b和端部54a沿x方向相邻的方式配置。

[0100]

接下来,参照图2至图13,对带通滤波器1的构成要素和层叠体2的内部的构成要素的对应关系进行说明。构成第一输入输出端口3的导体层311经由通孔31t1、32t1、33t1、导体层341及通孔35t1与图8所示的导体层371连接。如图13所示,导体层371经由电介质层37与谐振器导体部510的第一线路部分51a相对。图2所示的电容器c1由导体层371、谐振器导体部510以及其之间的电介质层37构成。电容器c1在谐振器导体部510的长边方向上朝向第三线路部分51c与端部51a分离的位置上与谐振器导体部510的第一线路部分51a连接。

[0101]

构成第二输入输出端口4的导体层312经由通孔31t2、32t2、33t2、导体层342及通孔35t2与图8所示的导体层372连接。如图13所示,导体层372经由电介质层37与谐振器导体部550的第二线路部分55b相对。图2所示的电容器c2由导体层372、谐振器导体部550、以及

其之间的电介质层37构成。电容器c2在谐振器导体部550的长边方向上朝向第三线路部分55c与端部55b分离的位置上与谐振器导体部550的第二线路部分55b连接。

[0102]

如图13所示,导体层391经由电介质层38与谐振器导体部510的第二线路部分51b和谐振器导体部520的第一线路部分52a相对。图2所示的电容器c12由导体层391、谐振器导体部510、520、以及其之间的电介质层38构成。电容器c12在谐振器导体部510的长边方向上朝向第三线路部分51c与端部51b分离的位置上与谐振器导体部510的第二线路部分51b连接。另外,电容器c12在谐振器导体部520的长边方向上朝向第三线路部分52c与端部52a分离的位置上与谐振器导体部520的第一线路部分52a连接。

[0103]

如图13所示,导体层392经由电介质层38配置于谐振器导体部520的第二线路部分52b和谐振器导体部530的第一线路部分53a的附近。图2所示的电容器c23由导体层392、谐振器导体部520、530、以及其之间的电介质层38构成。电容器c23在谐振器导体部520的长边方向上朝向第三线路部分52c与端部52b分离的位置上与谐振器导体部520的第二线路部分52b连接。另外,电容器c23在谐振器导体部530的长边方向上朝向第三线路部分53c与端部53a分离的位置上与谐振器导体部530的第一线路部分53a连接。

[0104]

如图13所示,导体层393经由电介质层38配置于谐振器导体部530的第二线路部分53b和谐振器导体部540的第一线路部分54a的附近。图2所示的电容器c34由导体层393、谐振器导体部530、540、以及其之间的电介质层38构成。电容器c34在谐振器导体部530的长边方向上朝向第三线路部分53c与端部53b分离的位置上与谐振器导体部530的第二线路部分53b连接。另外,电容器c34在谐振器导体部540的长边方向上朝向第三线路部分54c与端部54a分离的位置上与谐振器导体部540的第一线路部分54a连接。

[0105]

如图13所示,导体层394经由电介质层38与谐振器导体部540的第二线路部分54b和谐振器导体部550的第一线路部分55a相对。图2所示的电容器c45由导体层394、谐振器导体部540、550、以及其之间的电介质层38构成。电容器c45在谐振器导体部540的长边方向上朝向第三线路部分54c与端部54b分离的位置上与谐振器导体部540的第二线路部分54b连接。另外,电容器c45在谐振器导体部550的长边方向上朝向第三线路部分55c与端部55a分离的位置上与谐振器导体部550的第一线路部分55a连接。

[0106]

如图13所示,导体层395经由电介质层38与谐振器导体部520的第一线路部分52a和谐振器导体部540的第二线路部分54b相对。图2所示的电容器c24由导体层395、谐振器导体部520、540、以及其之间的电介质层38构成。

[0107]

第一分隔部7的四个第一通孔列分别通过将通孔7t2、7t3、7t4、7t5、7t7、7t8、7t9、7t10沿z方向串联连接而构成。在图3至图12所示的例子中,第一分隔部7以通过谐振器导体部510和谐振器导体部550之间的方式延伸,且与导体层321和导体层481相接。

[0108]

第二分隔部8的四个第二通孔列分别通过将通孔8t2、8t3、8t4、8t5、8t7、8t8、8t9、8t10沿z方向串联连接而构成。在图3至图12所示的例子中,第二分隔部8以通过由谐振器导体部520和谐振器导体部540包围的空间之间的方式延伸,且与导体层321和导体层481相接。

[0109]

屏蔽6通过连接导体层313~316、321、481和通孔6t1、6t2、6t3、6t4、6t5、6t7、6t8、6t9、6t10而构成。

[0110]

本实施方式的带通滤波器1设计及构成为例如通带存在于10~30ghz的亚毫米波

波段或30~300ghz的毫米波波段。

[0111]

接下来,对本实施方式的带通滤波器1的作用及效果进行说明。本实施方式的带通滤波器1具备两端开放型的谐振器51、52、53、54、55。谐振器51、52、53、54、55分别具有谐振器导体部510、520、530、540、550。除去谐振器导体部530之外的谐振器导体部510、520、540、550均为与本发明中的“谐振器导体部”对应的特定的谐振器导体部。谐振器导体部510、520、540、550分别包括以包围第一线路部分和第二线路部分之间的空间的方式延伸的第一至第三线路部分。由此,根据本实施方式,与所有谐振器导体部为直线形状的情况相比,能够将带通滤波器1小型化。

[0112]

此外,在本实施方式中,从z方向观察,谐振器导体部510、520、540、550分别具有u字形状。但是,谐振器导体部510、520、540、550的形状不限于u字形状,也可以是c字形状、弓形形状等形状。例如,第一线路部分和第二线路部分也可以不平行。如果将谐振器导体部的长度设为相同进行比较,则在上述任一形状中,与谐振器导体部的形状为直线形状或l字形状的情况相比,能够减小用于配置谐振器导体部的面积。

[0113]

另外,在本实施方式中,具有u字形状的谐振器导体部的数量是四个。但是,即使具有u字形状的谐振器导体部的数量是一个,与所有谐振器导体部为直线形状的情况相比,能够将带通滤波器1小型化。

[0114]

另外,在本实施方式中,在谐振器导体部510、520、530、540、550的任一个中,第三线路部分的宽度小于第一线路部分的第一宽度恒定部分及第二线路部分的第二宽度恒定部分各自的宽度。包括这样的第三线路部分的谐振器51~55均为阶梯阻抗谐振器(以下,也记为sir。)的一种。根据本实施方式,通过将谐振器51~55设为sir,能够缩短谐振器导体部的长度。由此,根据本实施方式,也能够将带通滤波器1小型化。

[0115]

另外,在本实施方式中,将在电路结构上最靠近第一输入输出端口3的谐振器51的谐振器导体部510和在电路结构上最靠近第二输入输出端口4的谐振器55的谐振器导体部550沿着x方向配置,同时将在电路结构上设置于谐振器51和谐振器55之间的中间谐振器即谐振器52~54的谐振器导体部520、530、540配置于谐振器导体部510、550的y方向的前端。x方向是与层叠体2的多个电介质层的层叠方向正交的第一方向,y方向是与层叠体2的多个电介质层的层叠方向正交的第二方向。根据本实施方式,通过沿第一方向和第二方向排列谐振器导体部510、520、530、540、550,与将所有谐振器导体部排列成一列的情况相比,能够将带通滤波器1小型化。

[0116]

另外,在本实施方式中,谐振器51的谐振器导体部510的第三线路部分51c和谐振器55的谐振器导体部550的第三线路部分55c以平行的方式相邻且分别沿着y方向延伸。根据本实施方式,通过如上所述将谐振器导体部520、530、540配置于谐振器导体部510、550的y方向的前端,能够容易地实现谐振器51、55之间的交叉耦合。

[0117]

另外,在本实施方式中,电容器c1、c2、c12、c23、c34、c45分别在离开对应的谐振器导体部的两端的位置上与对应的谐振器导体部连接。这些电容器的连接位置优选为高阶模式下的电压最小点及其附近。由此,能够抑制高阶模式。高阶模式也可以是二次模式。

[0118]

接下来,示出通过模拟求出的本实施方式的带通滤波器1的特性的一个例子。在模拟中,使用本实施方式的带通滤波器1的模型,求出带通滤波器1的插入损失的频率特性和反射损失的频率特性。在模拟中,以带通滤波器1的通带的中心频率成为约26ghz的方式设

计带通滤波器1。

[0119]

图14是表示插入损失及反射损失的频率特性的一个例子的特性图。图15是放大表示图14所示的插入损失的频率特性的一部分的特性图。图16是放大表示图14所示的反射损失的频率特性的一部分的特性图。图14至图16的横轴表示频率。图14的纵轴表示衰减量,图15的纵轴表示插入损失,图16的纵轴表示反射损失。在图14中,标注符号81的曲线表示插入损失的频率特性,标注符号82的曲线表示反射损失的频率特性。

[0120]

[第二实施方式]

[0121]

接下来,参照图17至图19,对本发明的第二实施方式进行说明。图17是表示本实施方式的带通滤波器的结构的立体图。图18是表示本实施方式中的第八层电介质层的图案形成面的说明图。图19是表示本实施方式的带通滤波器的主要部分的俯视图。

[0122]

本实施方式的带通滤波器1在以下的点上与第一实施方式不同。在本实施方式中,带通滤波器1的谐振器51、52、53、54、55分别具有谐振器导体部1510、1520、1530、1540、1550来替代第一实施方式中的谐振器导体部510、520、530、540、550。谐振器导体部1510、1520、1530、1540、1550分别沿与多个电介质层的层叠方向即z方向正交的方向延伸。

[0123]

谐振器导体部1510、1520、1530、1540、1550各自的两端开放。谐振器导体部1510、1520、1530、1540、1550分别具有与带通滤波器1的通带的中心频率对应的波长的1/2或与其相近的长度。

[0124]

谐振器导体部1510、1520、1530、1540、1550分别包括配置于在与z方向正交的方向上相互分离的位置的第一线路部分及第二线路部分和将第一线路部分和第二线路部分连接的第三线路部分。

[0125]

以下,分别使用符号151a、151b、151c表示谐振器导体部1510的第一线路部分、第二线路部分及第三线路部分。另外,分别使用符号152a、152b、152c表示谐振器导体部1520的第一线路部分、第二线路部分及第三线路部分。另外,分别使用符号153a、153b、153c表示谐振器导体部1530的第一线路部分、第二线路部分及第三线路部分。另外,分别使用符号154a、154b、154c表示谐振器导体部1540的第一线路部分、第二线路部分及第三线路部分。另外,分别使用符号155a、155b、155c表示谐振器导体部1550的第一线路部分、第二线路部分及第三线路部分。

[0126]

另外,在本实施方式中,带通滤波器1的层叠体2具有第八层电介质层138来替代第一实施方式中的第八层电介质层38。如图18所示,在电介质层138的图案形成面形成有分别由导体的线路构成的谐振器导体部1510、1520、1530、1540、1550。

[0127]

另外,在电介质层138形成有构成屏蔽6的多个通孔6t18、构成第一分隔部7的四个通孔7t18、以及构成第二分隔部8的四个通孔8t18。多个通孔6t18配置于谐振器导体部1510、1520、1530、1540、1550的周围。四个通孔7t18配置于谐振器导体部1510和谐振器导体部1550之间。四个通孔8t18配置于由谐振器导体部1520、1540包围的空间。

[0128]

谐振器导体部1510、1520、1530、1540、1550及通孔6t18、7t18、8t18和层叠体2的内部的其他构成要素的关系与第一实施方式中的谐振器导体部510、520、530、540、550及通孔6t8、7t8、8t8和层叠体2的内部的其他构成要素的关系相同。

[0129]

谐振器导体部1510、1520、1530、1540、1550所包含的所有线路部分的配置基本上与第一实施方式中的谐振器导体部510、520、530、540、550所包含的所有线路部分的配置相

同。

[0130]

在本实施方式中,从z方向观察,谐振器导体部1510的整体即第一至第三线路部分151a~151c具有包围第一线路部分151a和第二线路部分151b之间的空间的c字形状。第一线路部分151a具有处于在谐振器导体部1510的长边方向上距第三线路部分151c最远的位置的端部151a。第二线路部分151b具有处于在谐振器导体部1510的长边方向上距第三线路部分151c最远的位置的端部151b。

[0131]

另外,从z方向观察,谐振器导体部1520的整体即第一至第三线路部分152a~152c具有包围第一线路部分152a和第二线路部分152b之间的空间的c字形状。第一线路部分152a具有处于在谐振器导体部1520的长边方向上距第三线路部分152c最远的位置的端部152a。第二线路部分152b具有处于在谐振器导体部1520的长边方向上距第三线路部分152c最远的位置的端部152b。

[0132]

另外,谐振器导体部1530的整体即第一至第三线路部分153a~153c沿着x方向延伸。第一线路部分153a具有处于在谐振器导体部1530的长边方向上距第三线路部分153c最远的位置的端部153a。第二线路部分153b具有处于在谐振器导体部1530的长边方向上距第三线路部分153c最远的位置的端部153b。

[0133]

另外,从z方向观察,谐振器导体部1540的整体即第一至第三线路部分154a~154c具有包围第一线路部分154a和第二线路部分154b之间的空间的c字形状。第一线路部分154a具有处于在谐振器导体部1540的长边方向上距第三线路部分154c最远的位置的端部154a。第二线路部分154b具有处于在谐振器导体部1540的长边方向上距第三线路部分154c最远的位置的端部154b。

[0134]

另外,从z方向观察,谐振器导体部1550的整体即第一至第三线路部分155a~155c具有包围第一线路部分155a和第二线路部分155b之间的空间的c字形状。第一线路部分155a具有处于在谐振器导体部1550的长边方向上距第三线路部分155c最远的位置的端部155a。第二线路部分155b具有处于在谐振器导体部1550的长边方向上距第三线路部分155c最远的位置的端部155b。

[0135]

在谐振器导体部1510、1520、1530、1540、1550的任一个中,第一线路部分具有宽度恒定的第一宽度恒定部分,第二线路部分具有宽度恒定的第二宽度恒定部分,第三线路部分的宽度小于第一及第二宽度恒定部分各自的宽度。

[0136]

本实施方式中的其它结构、作用及效果与第一实施方式同样。

[0137]

此外,本发明不限于上述各实施方式,能够进行各种变更。例如,谐振器的数量或结构不限于各实施方式所示,满足权利要求书中的范围即可。谐振器的数量可以是三个,也可以是四个,也可以是六个以上。

[0138]

基于以上的说明,显然能够实施本发明的各种方式或变形例。因此,在权利要求书中的范围的等同的范围内,也能够以上述的最佳方式以外的方式实施本发明。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1