碳化硅半导体装置以及使用碳化硅半导体装置的电力变换装置的制作方法

本公开涉及碳化硅半导体装置以及使用碳化硅半导体装置的电力变换装置。

背景技术:

1、已知内置mosfet(metal-oxide-semiconductor field-effect-transistor:绝缘栅极型场效应晶体管)等单极型的开关元件、和肖特基势垒二极管(sbd:schottky barrierdiode)等单极型的回流二极管的电力用的半导体装置(例如专利文献1)。这样的半导体装置能够通过在同一芯片并联地配置mosfet单元和sbd单元来实现,一般而言,能够通过在芯片内的特定的区域设置肖特基电极并使该区域作为sbd动作来实现。

2、通过在开关元件的芯片中内置回流二极管,能够比对开关元件外装回流二极管的情况降低成本。特别,在将碳化硅(sic)用作母材的mosfet中,还能够通过内置sbd来抑制由寄生pn二极管引起的双极性动作。

3、现有技术文献

4、专利文献

5、专利文献1:日本特开2007-234925号公报

技术实现思路

1、在这样的内置sbd的mosfet中,有由肖特基电极和某个导电类型(例如n型)的半导体层构成的肖特基二极管,该某个导电类型(例如n型)的半导体层被与该导电类型相反的导电类型(例如p型)的阱区域夹住地形成,距两侧的相反的导电类型(例如p型)的阱区域的距离越大,施加到肖特基界面的电场变得越大。

2、另一方面,关于在肖特基二极管中流过的电流,由于两侧的相反的导电类型(例如p型)的阱区域,电流路径在空间上受到限制,而有时无法充分增大在肖特基二极管中流过的电流的最大值。

3、本公开是为了解决如上述的课题而完成的,其目的在于,通过不提高施加到肖特基界面的电场而增大在肖特基二极管中流过的电流,提供可靠性高的碳化硅半导体装置。

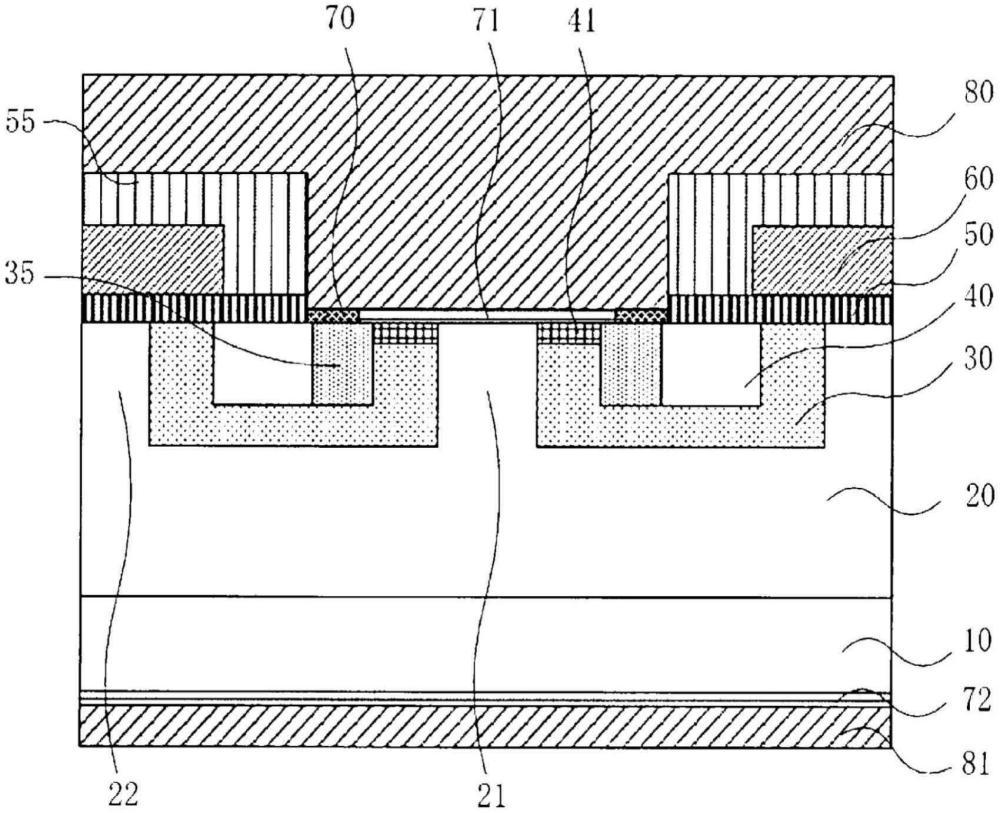

4、本公开的碳化硅半导体装置具备:碳化硅半导体的第1导电类型的漂移层,形成于第1导电类型的半导体基板的第1主面上;第2导电类型的阱区域,在漂移层表层在剖面横向上分离地形成,其间具备第1导电类型的第1分离区域;第1导电类型的第2分离区域,形成于阱区域与阱区域之间,形成于未形成第1分离区域的区域;第1导电类型的源极区域,形成于阱区域内的半导体表层的剖面横向的内部;第2导电类型的接触区域,形成于阱区域内的半导体表层的剖面横向的内部的比源极区域更靠第1分离区域侧的位置;第1导电类型的电流扩散区域,形成于接触区域与第1分离区域之间的阱区域的表层部;栅极绝缘膜,形成于第2分离区域以及与第2分离区域邻接的阱区域上;栅电极,形成于栅极绝缘膜上;欧姆电极,形成于接触区域上;肖特基电极,形成于第1分离区域上,与第1分离区域肖特基连接;源电极,形成于欧姆电极和肖特基电极上;以及漏电极,形成于所述半导体基板的与第1主面相反的第2主面。

5、根据本公开所涉及的碳化硅半导体装置,能够得到可靠性高的碳化硅半导体装置。

技术特征:

1.一种碳化硅半导体装置,具备:

2.根据权利要求1所述的碳化硅半导体装置,其中,

3.根据权利要求1或者2所述的碳化硅半导体装置,其中,

4.根据权利要求1至3中的任意一项所述的碳化硅半导体装置,其中,

5.根据权利要求1至4中的任意一项所述的碳化硅半导体装置,其中,

6.根据权利要求1至5中的任意一项所述的碳化硅半导体装置,其中,

7.根据权利要求1至6中的任意一项所述的碳化硅半导体装置,其中,

8.根据权利要求1至7中的任意一项所述的碳化硅半导体装置,其中,

9.一种电力变换装置,具备:

技术总结

本公开的碳化硅半导体装置具备n型半导体基板(10)上的n型漂移层(20)、漂移层的表层的p型阱区域(30)、阱区域间n型第1分离区域(21)、n型第2分离区域(22)、阱区域内的n型源极区域(40)、p型接触区域(35)、阱区域表层的n型电流扩散区域、栅极绝缘膜(50)、栅电极(60)、欧姆电极(70)、以及第1分离区域上肖特基电极(71)。

技术研发人员:日野史郎,川原洸太朗

受保护的技术使用者:三菱电机株式会社

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!