半导体装置的制作方法

半导体装置

1.本技术以日本专利申请2021-148365号(申请日:2021年9月13日)作为基础申请而享有优先权。本技术通过参照该基础申请而包括基础申请的全部内容。

技术领域

2.实施方式涉及一种半导体装置。

背景技术:

3.作为功率器件,例如可采用使用了氮化镓(gan)的横式的hemt(high electron mobility transistor:高电子迁移率晶体管)。作为这样的gan器件特有的现象,有时在开关中导通电阻会提高。为了抑制该现象,有时在gan器件中使基板成为源极电位。

技术实现要素:

4.实施方式提供一种能够抑制因漏极电极与基板之间的基板电容引起的振铃的半导体装置。

5.根据实施方式,半导体装置具备:第一端子;第二端子;第一芯片,具有与所述第二端子电连接的基板、设置在所述基板上的氮化物半导体层、设置在所述氮化物半导体层上并与所述第一端子电连接的第一漏极电极、设置在所述氮化物半导体层上并与所述第二端子电连接的第一源极电极、以及所述第一漏极电极与所述基板之间的基板电容;以及电阻部,串联连接在所述第一漏极电极与所述第二端子之间的包括所述基板电容的路径上。

附图说明

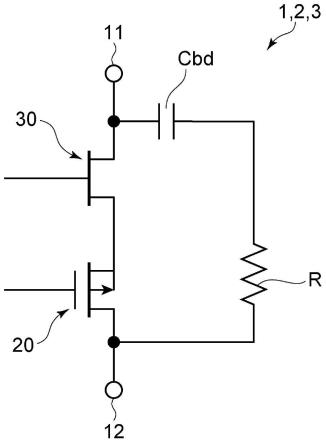

6.图1是第一~第四实施方式的半导体装置的等效电路图。

7.图2是第一实施方式的半导体装置的示意俯视图。

8.图3是表示图2中的a-a剖面的示意剖视图。

9.图4是第一~第三、第五~第七实施方式的第一芯片的示意剖视图。

10.图5是第二实施方式的半导体装置的示意俯视图。

11.图6是表示图5中的b-b剖面的示意剖视图。

12.图7是第三实施方式的半导体装置的示意俯视图。

13.图8是第四实施方式的第一芯片的示意剖视图。

14.图9是第五~第八实施方式的半导体装置的等效电路图。

15.图10是第五实施方式的半导体装置的示意俯视图。

16.图11是表示图10中的c-c剖面的示意剖视图。

17.图12是第六实施方式的半导体装置的示意俯视图。

18.图13是表示图12中的d-d剖面的示意剖视图。

19.图14是第七实施方式的半导体装置的示意俯视图。

20.图15是第九实施方式的半导体装置的等效电路图。

21.图16的(a)是使用了图15的电路的模拟所涉及的vds的波形图,图16的(b)是此时的id的波形图。

22.图17的(a)是使用了图15的电路的模拟所涉及的vds的波形图,图17的(b)是此时的id的波形图。

23.图18的(a)是使用了图15的电路的模拟所涉及的vds的波形图,图18的(b)是此时的id的波形图。

24.图19的(a)是使用了图15的电路的模拟所涉及的vds的波形图,图19的(b)是此时的id的波形图。

25.图20是表示使用了图15的电路的模拟所涉及的栅极电阻rg与开关损耗eon的关系的图表。

具体实施方式

26.以下,参照附图对实施方式进行说明。其中,在各附图中,对相同的构成赋予相同的附图标记。

27.[第一实施方式]

[0028]

参照图1~图4对第一实施方式的半导体装置1进行说明。

[0029]

如图1所示,半导体装置1具有第一端子11、第二端子12、第一芯片30以及第二芯片20。第一芯片30与第二芯片20级联(cascode)连接在第一端子11与第二端子12之间。

[0030]

第一芯片30例如包括在对栅极没有输入信号的情况下成为导通的常开型的hemt(high electron mobility transistor)。

[0031]

如图4所示,第一芯片30具有基板31、和设置在基板31上的第一半导体层40。第一半导体层40具有第一氮化物半导体层41与第二氮化物半导体层42的异质结构造。在基板31上设置有第一氮化物半导体层41,在第一氮化物半导体层41上设置有第二氮化物半导体层42。第二氮化物半导体层42的带隙大于第一氮化物半导体层41的带隙。例如,第一氮化物半导体层41是不掺杂的gan层,第二氮化物半导体层42是algan层。在第一氮化物半导体层41中的与第二氮化物半导体层42的界面附近形成为二维电子气36。

[0032]

在第二氮化物半导体层42上设置有第一漏极电极32和第一源极电极33。第一漏极电极32以及第一源极电极33与第二氮化物半导体层42相接。在第二氮化物半导体层42上的第一漏极电极32与第一源极电极33之间的区域,隔着绝缘膜35设置有第一栅极电极34。

[0033]

基板31例如是硅基板。基板31的电阻值例如为1mω

·

cm以上1ω

·

cm以下。第一芯片30在第一漏极电极32与基板31之间具有基板电容cbd。

[0034]

如图2以及图3所示,半导体装置1还具有裸片焊盘(die pad)13、第一栅极端子14、第二栅极端子16以及电源端子15。第一端子11、第二端子12、裸片焊盘13、第一栅极端子14、第二栅极端子16以及电源端子15构成作为金属部件的引线框架。引线框架、第一芯片30以及第二芯片20由树脂覆盖而被封装。

[0035]

第一芯片30被搭载于裸片焊盘13上。第一芯片30的基板31通过接合部件51而接合于裸片焊盘13。接合部件51的材料例如是焊料、ag膏等。

[0036]

第一芯片30的第一漏极电极32通过金属线w而与第一端子11电连接。第一芯片30的第一源极电极33通过金属线w而与电源端子15电连接。第一芯片30的第一栅极电极34通

过金属线w而与第一栅极端子14电连接。

[0037]

第二芯片20是在对栅极没有输入信号的情况下成为截止的常闭型,例如包括p型沟道的mosfet(metal-oxide-semiconductor field effect transistor:金属氧化物半导体场效应晶体管)。

[0038]

第二芯片20具有第二半导体层21、设置在第二半导体层21的厚度方向上的一个面的第二漏极电极22、设置在第二半导体层21的厚度方向上的另一个面的第二源极电极23、以及设置于所述另一个面的第二栅极电极24。第二半导体层21例如是硅层,包括p型的沟道。第二芯片20是在第二半导体层21的厚度方向(将第二漏极电极22与第二源极电极23连结的纵向)流动电流的纵型器件。

[0039]

第二芯片20被搭载于第二端子12上。第二芯片20的第二漏极电极22例如通过焊料等接合部件而与第二端子12接合。第二漏极电极22与第二端子12电连接。

[0040]

第二芯片20的第二源极电极23通过金属线w而与电源端子15以及第一芯片30的第一源极电极33电连接。第二芯片20的第二栅极电极24通过金属线w而与第二栅极端子16电连接。第一芯片30的第一源极电极33经由第二芯片20而与第二端子12电连接。

[0041]

如图1所示,半导体装置1具有电阻部r,该电阻部r串联连接于第一芯片30的第一漏极电极32与第二端子12之间的包括基板电容cbd的路径上。电阻部r不是寄生电阻而是有意地插入至上述路径的电阻部。例如,电阻部r的电阻比第一芯片30的基板31的电阻高。

[0042]

第一实施方式的半导体装置1包括图2所示的芯片电阻器61作为电阻部r。芯片电阻器61电连接在与第一芯片30的基板31接合的裸片焊盘13和第二端子12之间。

[0043]

如果第一芯片30的基板电容cbd与金属线、布线等的寄生电感引起串联共振,则成为漏极电流的振铃的一个因素。通常,为了抑制这样的振铃而插入大的外带栅极电阻来降低dv/dt(在开关过渡期产生的每单位时间的漏极/源极间的电压变化量)。但是,如果dv/dt下降,则开关损耗增加、电路效率降低。

[0044]

根据本实施方式,在第一芯片30的第一漏极电极32与第二端子12之间的包括基板电容cbd的路径上串联连接电阻部r。电阻部r构成基板电容cbd和rc缓冲电路。基板电容cbd与寄生电感的串联共振的能量被电阻部r(缓冲电阻)消耗(吸收),能够抑制漏极电流的振铃。

[0045]

通过抑制漏极电流的振铃,能够降低栅极电阻而实现高的dv/dt下的稳定动作。结果是,开关损耗降低,电路效率提高。

[0046]

以下,对其他实施方式进行说明。在其他实施方式中,对与第一实施方式相同的构成赋予相同的附图标记,并省略其详细的说明。在其他实施方式中,也与第一实施方式同样,在第一芯片30的第一漏极电极32与第二端子12之间的包括基板电容cbd的路径上串联连接有电阻部r。因此,在其他实施方式中,基板电容cbd与寄生电感的串联共振的能量也被电阻部r(缓冲电阻)消耗(吸收),能够抑制漏极电流的振铃。

[0047]

[第二实施方式]

[0048]

参照图5以及图6对第二实施方式的半导体装置2进行说明。

[0049]

在第二实施方式中,在第二端子12上搭载有第一芯片30以及第二芯片20。即,第二端子12还兼作搭载第一芯片30的裸片焊盘。第一芯片30的基板31通过接合部件51接合于第二端子12。第二实施方式中的电阻部r包括将基板31与第二端子12(兼作裸片焊盘)接合的

接合部件51。优选作为电阻部r的接合部件51的材料例如是减少了ag的比例后的ag膏。

[0050]

[第三实施方式]

[0051]

参照图7对第三实施方式的半导体装置3进行说明。

[0052]

第三实施方式中的电阻部62被设置在第一芯片30上。电阻部62通过金属线w与裸片焊盘13以及第二端子12电连接。电阻部62的材料例如是形成在第一芯片30上的薄膜电阻。或者,通过根据图4所示的第一漏极电极32以及第二源极电极33在俯视下的纵横比来对ganhemt本身的电阻进行调整,能够调整与包括第一漏极电极32和第二端子12之间的基板电容cbd的路径上连接的电阻部r的电阻。即,该情况下,第一漏极电极32以及第二源极电极33可作为第一芯片30上的电阻部62发挥功能。

[0053]

[第四实施方式]

[0054]

图8是第四实施方式的第一芯片30的示意剖视图。

[0055]

第四实施方式中的电阻部r包括设置于第一芯片30的基板31的电阻层63。电阻层63例如是低硼掺杂的高电阻si层。另外,电阻层63也可以设置在氮化物半导体层41、42中的第一漏极电极32与基板31之间的区域。

[0056]

[第五实施方式]

[0057]

参照图9~图11对第五实施方式的半导体装置5进行说明。

[0058]

半导体装置5具有第一端子11、第二端子12以及第一芯片30。第一芯片30的第一漏极电极32与第一端子11电连接,第一源极电极33与第二端子12电连接。

[0059]

半导体装置5不包括第二芯片20。半导体装置5的第一芯片30例如包括在对栅极没有输入信号的情况下成为截止的常闭型的hemt。

[0060]

第五实施方式的半导体装置5包括图10所示的芯片电阻器61作为电阻部r。芯片电阻器61电连接在与第一芯片30的基板31接合的裸片焊盘13和第二端子12之间。

[0061]

[第六实施方式]

[0062]

参照图12以及图13对第六实施方式的半导体装置6进行说明。

[0063]

半导体装置6不包括第二芯片20。半导体装置6的第一芯片30例如包括常闭型的hemt。

[0064]

在第六实施方式中,第一芯片30被搭载于第二端子12上。第二端子12还兼作搭载第一芯片30的裸片焊盘。第一芯片30的基板31通过接合部件51而与第二端子12接合。第二实施方式中的电阻部r包括将基板31和第二端子12(兼作裸片焊盘)接合的接合部件51。

[0065]

[第七实施方式]

[0066]

参照图14对第七实施方式的半导体装置7进行说明。

[0067]

半导体装置7不包括第二芯片20。半导体装置7的第一芯片30例如包括常闭型的hemt。

[0068]

第七实施方式中的电阻部62被设置在第一芯片30上。电阻部62通过金属线w与裸片焊盘13以及第二端子12电连接。

[0069]

[第八实施方式]

[0070]

第八实施方式的半导体装置不包括第二芯片20。第八实施方式的半导体装置的第一芯片30例如包括常闭型的hemt。第八实施方式中的电阻部r包括设置于第一芯片30的基板31的电阻层63。另外,电阻层63也可以设置于氮化物半导体层41、42中的第一漏极电极32

与基板31之间的区域。

[0071]

[第九实施方式]

[0072]

包括级联连接的第一芯片30以及第二芯片20的第一~第四实施方式的半导体装置如图15所示,能够应用于电源电路的半桥电路。

[0073]

半桥电路具有高侧器件101和低侧器件102。高侧器件101以及低侧器件102分别包括级联连接的第一芯片30以及第二芯片20。

[0074]

高侧器件101的第二芯片20的第二漏极电极与低侧器件102的第一芯片30的第一漏极电极相互连接。另外,高侧器件101的第二芯片20的第二漏极电极和低侧器件102的第一芯片30的第一漏极电极之间的连接部120与负载l连接。负载l连接在高侧器件101和低侧器件102的连接部120与高侧器件101的第一芯片30的第一漏极电极(第一端子11)之间。连接部120对应于高侧器件101中的第二端子,并对应于低侧器件102中的第一端子。

[0075]

将高侧器件101的第二芯片20的第二漏极电极与连接部120(第二端子)之间的寄生电感设为lss1。将高侧器件101的第一芯片30的基板电容cbd和连接部120(第二端子)之间的寄生电感设为lss2。

[0076]

高侧器件101包括串联连接在第一芯片30的基板电容cbd与寄生电感lss2之间的电阻部r1。

[0077]

将低侧器件102的第二芯片20的第二漏极电极与第二端子12之间的寄生电感设为lss1。将低侧器件102的第一芯片30的基板电容cbd与第二端子12之间的寄生电感设为lss2。

[0078]

低侧器件102包括串联连接在第一芯片30的基板电容cbd与寄生电感lss2之间的电阻部r2。

[0079]

接下来,对使用了图15所示的电路的模拟的结果进行说明。

[0080]

计算从高侧器件101以及低侧器件102都为截止状态的死区时间使低侧器件102接通时的低侧器件102的漏极/源极间电压vds和漏极电流id。第一芯片30是常开型的hemt,第二芯片20是常闭型的p型沟道mosfet。高侧器件101的第一端子11的电位为400v,连接部120以及低侧器件102的第二端子12的电位为0v,寄生电感lss1为0.2nh,寄生电感lss2为0.02nh,负载l的电感为200μh。

[0081]

图16的(a)是使插入于低侧器件102的第二芯片20的栅极中的栅极电阻值rg为30ω、使插入于高侧器件101的基板电容cbd与寄生电感lss2的线路中的电阻部r1的电阻值r1以及电阻部r2的电阻值r2为0ω时的vds的波形图,图16的(b)是此时的id的波形图。

[0082]

图17的(a)是使上述rg为30ω、使上述r1、r2为2.5ω时的vds的波形图,图17的(b)是此时的id的波形图。

[0083]

图18的(a)是使上述rg为30ω、使上述r1、r2为5ω时的vds的波形图,图18的(b)是此时的id的波形图。

[0084]

图19的(a)是使上述rg为100ω、使上述r1、r2为0ω时的vds的波形图,图19的(b)是此时的id的波形图。

[0085]

根据图16的(a)~图18的(b)的结果可知,在栅极电阻rg相同的(30ω)条件下,越增高插入于基板电容cbd和寄生电感lss2的线路中的电阻部(缓冲电阻)r1以及r2的电阻值,则越抑制了漏极电流id的振铃。为了不设置缓冲电阻r1以及r2而通过栅极电阻rg来抑

制漏极电流id的振铃,如图19的(b)的结果所示,需要增大栅极电阻rg(100ω)。然而,如果增大栅极电阻rg,则开关损耗增加,会招致电路效率的降低。

[0086]

图20是表示使图15的电路中的所述的低侧器件102导通时的栅极电阻rg、高侧器件101的电阻部(缓冲电阻)r1的电阻值r1以及开关损耗eon的关系的图表。

[0087]

开关损耗eon是高侧器件101的第一芯片30中的损耗、低侧器件102的第一芯片30中的损耗、高侧器件101的电阻部(缓冲电阻)r1中的损耗、以及低侧器件102的电阻部(缓冲电阻)r2中的损耗的合计。

[0088]

在栅极电阻rg相同的条件下,如果电阻值r1变大,则由于缓冲电阻r1中的损耗而存在开关损耗eon变大的趋势。由于即便存在缓冲电阻r1中的损耗,通过插入缓冲电阻r1也能够抑制漏极电流的振铃,所以能够减小栅极电阻rg。结果是,能够降低开关损耗eon。例如,根据图20的结果,通过使缓冲电阻r1为15ω来抑制振铃,如果能够将栅极电阻rg降至5ω,则能够减小开关损耗eon。

[0089]

对本发明的几个实施方式进行了说明,但这些实施方式只是例示,并不意图限定发明的范围。这些新的实施方式能够通过其他各种方式加以实施,在不脱离发明主旨的范围能够进行各种省略、置换、变更。这些实施方式及其变形包含于发明的范围、主旨中并且包含在权利要求所记载的发明及其等同的范围中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1