一种复合碳化硅衬底及其制备方法与流程

1.本发明涉及半导体材料领域,特别涉及一种复合碳化硅衬底及其制备方法。

背景技术:

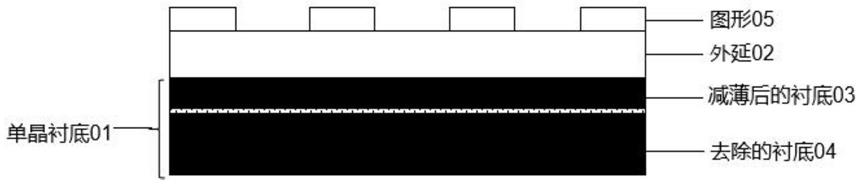

2.碳化硅(sic)具有优越的物理性能,如高禁带宽度(对应高击穿电场和高功率密度)、高电导率、高热导率等。碳化硅晶片作为半导体衬底材料,经过外延生长、器件制造等环节,可制成碳化硅基功率器件和微波射频器件,是第三代半导体产业发展的重要基础材料。考虑碳化硅衬底加工过程中的翘曲,外延过程中引入的应力,以及器件工艺中夹持的问题,商用碳化硅衬底的厚度一般在350um或以上。从目前碳化硅功率器件的工艺来看,以垂直结构的mosfet为例,为了提高器件的纵向热导,以及降低垂直沟道导通电阻,在350um厚碳化硅单晶衬底01上进行外延02、以及图形05等平面工艺后,需要对碳化硅单晶衬底做减薄处理,然后在减薄后的衬底03背面做金属欧姆接触电极,作为mosfet的漏极。该减薄工艺过程要去除200-300um厚的单晶衬底04,如图1所示。可以看出,单晶衬底中的大部分只是作为牺牲片起到了结构支撑的作用,在工艺后期被去除后,未作为最终的器件功能层得到有效利用,这造成碳化硅单晶材料的极大浪费。

3.专利cn201780044382.x公开了一种半导体基板,其特征在于,由一个单晶sic基板和多晶sic基板,以及一个高浓度掺杂氮原子或磷原子的界面层构成。该方法通过掺杂缺陷降低了界面层的电阻。专利cn201480038163.7公开了一种半导体基板的制造方法,将一个碳化硅单晶与一个碳化硅多晶,表面掺杂预备处理后通过键合的方法结合在一起,研磨抛光后得到一个包含单晶层与多晶层复合的基板。

4.上述公开的方法部分地解决了碳化硅单晶材料的损耗问题。专利cn201780044382.x虽然通过氮原子或磷原子的掺杂降低了界面层的电阻,但这些高浓度掺杂会在界面层引起大量的结构缺陷。而专利cn201480038163.7通过键合工艺制备的单晶多晶复合衬底,键合过程不可避免会在碳化硅单晶层11与碳化硅多晶层12的界面残留有微小空隙13,如等效直径10um左右,高度5nm左右的空隙,如图2所示。无论是掺杂缺陷,还是键合空隙,都严重降低了单晶层与多晶层的结合力,以及垂直于面内的方向上抗拉强度,这在后续制作器件的高温工艺,如高温cvd外延、高温离子注入以及高温退火等工艺过程,存在开裂和失效的风险。

技术实现要素:

5.本发明提出一种复合碳化硅衬底及其制备方法,旨在解决碳化硅单晶和碳化硅多晶复合衬底存在的界面结合问题,能有效保持衬底应用性能的稳定性,保证与后续垂直器件工艺的兼容性,为高性能低成本碳化硅基器件制备奠定基础。为此,本发明采用以下技术方案:

6.一种复合碳化硅衬底,如图3所示,所述衬底包括碳化硅单晶层1、碳化硅多晶层2以及位于碳化硅单晶层1与碳化硅多晶层2之间碳化硅陶瓷层3;所述碳化硅单晶层1晶体为

六方相4h型,所述碳化硅多晶层2晶体颗粒为立方相3c型;所述碳化硅陶瓷层3晶体颗粒为六方相4h型和立方相3c型的混合;

7.其中,所述碳化硅陶瓷层3靠近碳化硅单晶层1的一侧界面,其六方相4h型晶体颗粒的平均尺寸大于陶瓷层中其他位置的4h型晶体颗粒;所述碳化硅陶瓷层3靠近碳化硅多晶层2的一侧界面,其立方相3c型晶体颗粒平均尺寸大于陶瓷层中其他位置的3c型晶体颗粒。

8.其中,所述衬底在垂直于面内方向上的抗拉强度大于150mpa。

9.其中,所述碳化硅陶瓷层的厚度小于碳化硅单晶层的厚度;所述碳化硅单晶层的厚度小于碳化硅多晶层的厚度。

10.其中,所述衬底厚度为300-450um,优选为330-370um;所述碳化硅陶瓷层厚度为1-30um,优选为5um;所述碳化硅单晶层厚度为30-150um,优选80-90um;所述碳化硅多晶层厚度为100-400um,优选260-270um。

11.本发明还提出一种复合碳化硅衬底的制备方法,如图4所示,包括如下步骤:

12.1)将含有六方相α-sic和立方相β-sic的碳化硅粉末层置于六方相4h型碳化硅单晶层与立方相3c型碳化硅多晶层之间进行堆叠;

13.2)在堆叠方向上施加压力,并加热至第一目标温度,即六方相4h型晶体的结晶温度,保持一定时间,使靠近碳化硅单晶层的一侧的部分六方相α-sic粉末在六方相单晶的晶核诱导下长大为六方相4h型晶体颗粒后,而其他位置的α-sic粉末无晶核诱导,尺寸保持不变;

14.3)保持堆叠方向上施加压力,进行匀速降温,降至第二目标温度,即立方相3c型晶体的结晶温度,保持一定时间,使靠近碳化硅立方相多晶层的一侧的部分立方相β-sic粉末在立方相多晶的晶核诱导下长大为立方相3c型晶体颗粒,而其他位置的β-sic粉末无晶核诱导,尺寸保持不变;

15.4)释放压力,碳化硅粉末层烧结形成碳化硅陶瓷层,得到碳化硅单晶层与碳化硅多晶层接合在一起的晶片;

16.5)将晶片进行表面研磨抛光,得到复合碳化硅衬底。

17.其中,所述设置碳化硅粉末层的碳化硅单晶层或碳化硅多晶层的表面平均粗糙度为0.1um-2um。

18.其中,所述碳化硅粉末中六方相α-sic和立方相β-sic的质量比为1:1;所述碳化硅陶瓷粉末中还含有al2o3和y2o3粉末;al2o3粉末的质量比小于6%;y2o3粉末的质量比小于4%;

19.其中,所述六方相α-sic、立方相β-sic、al2o3和y2o3的颗粒等效直径小于1um。

20.其中,所述第一目标温度为1800-2100℃,优选1900℃,保持时间为1-5小时;所述第二目标为1300-1500℃,优选1400℃,保持时间为1-5小时;所述第一目标温度降至第二目标温度的匀速降温速度大于20℃/min。

21.其中,所述施加的压力大于10-20mpa,优选15mpa。

22.采用以上方法得到的复合碳化硅衬底翘曲度小于50um;碳化硅单晶层表面的平均粗糙度小于1nm,碳化硅多晶层表面的平均粗超度小于100nm;所述复合衬底为圆形,直径50mm-200mm,优选50mm、100mm、150mm,以及200mm。

23.所述抛光研磨,包括粗研磨,细研磨,化学机械抛光(cmp)等常规工艺,业内专业人员采用相应的设备,都可以实施。

24.本发明采用以上技术方案,通过在六方相4h型碳化硅单晶层与立方相3c型碳化硅多晶层之间放置六方相α-sic和立方相β-sic粉末高温烧结成形成碳化硅陶瓷层,通过碳化硅陶瓷层将碳化硅单晶层与碳化硅多晶层接合在一起,形成复合碳化硅衬底。在第一目标温度,即六方相4h型晶体的结晶温度,保温时,在靠近碳化硅六方相单晶层的一侧,在六方相单晶的晶核诱导下,部分六方相α-sic粉末长大为六方相4h型晶体颗粒,而其他位置的α-sic粉末无晶核诱导,晶粒无法长大,这一侧碳化硅陶瓷层与六方相4h型的碳化硅单晶层形成强力结合;在第二目标温度,即立方相3c型晶体的结晶温度,保温时,在靠近碳化硅立方相多晶层的一侧,在立方相多晶的晶核诱导下,部分立方相β-sic粉末长大为立方相3c型晶体颗粒,而其他位置的β-sic粉末无晶核诱导,晶粒无法长大,使这一侧碳化硅陶瓷层能与立方相碳化硅多晶层形成强力结合,从而有效消除了传统工艺中存在的碳化硅多晶层和碳化硅单晶层界面处的空隙和杂质缺陷等问题。能有效保持衬底应用性能的稳定性,保证与后续垂直器件工艺的兼容性。在应用该衬底时,碳化硅单晶层用于器件的功能层,而碳化硅多晶层和碳化硅陶瓷层只用于工艺中间过程,起到结构支撑作用,完成碳化硅单晶层一侧的平面工艺后,碳化硅多晶层和陶瓷层被全部去除。该方法制得的复合衬底总厚度可控制在300-450um之间,与现有半导体平面工艺和设备相兼容。碳化硅单晶层与碳化硅多晶层的结合力强,使得该复合衬底在后续应用中,可以耐受1750℃的高温工艺而不会在界面开裂。本发明提出的复合衬底,可以大幅提高碳化硅单晶的利用率,极大地降低碳化硅衬底的制造成本,适用于垂直结构的碳化硅器件,如碳化硅mosfet等。

附图说明

25.图1为现有技术中碳化硅单晶衬底减薄工艺过程示意图。

26.图2为现有技术中碳化硅单晶和碳化硅多晶复合衬底界面存在空隙的现象示意图。

27.图3为本发明复合碳化硅衬底结构示意图。

28.图4为本发明复合碳化硅衬底制备流程示意图。

具体实施方式

29.为了使本发明的目的、特征和优点更加的清晰,以下结合附图及实施例,对本发明的具体实施方式做出更为详细的说明,在下面的描述中,阐述了很多具体的细节以便于充分的理解本发明,但是本发明能够以很多不同于描述的其他方式来实施。因此,本发明不受以下公开的具体实施的限制。

30.按照本发明所述的一种复合碳化硅衬底及其制备方法,进行具体实施说明:

31.一种复合碳化硅衬底,如图3所示,所述衬底包括碳化硅单晶层1、碳化硅多晶层2以及位于碳化硅单晶层1与碳化硅多晶层2之间碳化硅陶瓷层3;所述碳化硅单晶层1晶体颗粒为六方相4h型,所述碳化硅多晶层2晶体颗粒为立方相3c型;所述碳化硅陶瓷层3晶体颗粒为六方相4h型和立方相3c型的混合;

32.其中,所述碳化硅陶瓷层3靠近碳化硅单晶层1的一侧,其六方相4h型晶体颗粒的

平均尺寸大于陶瓷层中其他位置的4h型晶体颗粒;所述碳化硅陶瓷层3靠近碳化硅多晶层2的一侧,其立方相3c型晶体颗粒平均尺寸大于陶瓷层中其他位置的3c型晶体颗粒。

33.其中,所述衬底在垂直于面内方向上的抗拉强度为160mpa。

34.其中,所述碳化硅陶瓷层的厚度小于碳化硅单晶层的厚度;所述碳化硅单晶层的厚度小于碳化硅多晶层的厚度。

35.其中,所述衬底厚度为350um;所述碳化硅陶瓷层厚度为5um;所述碳化硅单晶层厚度为85um;所述碳化硅多晶层厚度为260um。

36.一种复合碳化硅衬底的制备方法,如图4所示,包括如下步骤:

37.1)将含有六方相α-sic和立方相β-sic的碳化硅粉末层置于六方相4h型碳化硅单晶层与立方相3c型碳化硅多晶层之间进行堆叠;

38.2)在堆叠方向上施加压力,并加热至第一目标温度保持一定时间,使靠近碳化硅单晶层的一侧的部分六方相α-sic粉末在六方相单晶的晶核诱导下长大为六方相4h型晶体颗粒后,其他位置的α-sic粉末无晶核诱导保持不变,形成该界面处六方相4h型晶体颗粒的平均尺寸大于其他位置的4h型晶体颗粒;

39.3)保持堆叠方向上施加压力,进行匀速降温,降至第二目标温度保持一定时间,使靠近碳化硅立方相多晶层的一侧的部分立方相β-sic粉末在立方相多晶的晶核诱导下长大为立方相3c型晶体颗粒,其他位置的β-sic粉末无晶核诱导保持不变,形成该界面处立方相3c型晶体颗粒平均尺寸大于其他位置的3c型晶体颗粒;

40.4)释放压力,碳化硅粉末层烧结形成碳化硅陶瓷层,得到碳化硅单晶层与碳化硅多晶层接合在一起的晶片;

41.5)将晶片进行表面研磨抛光,得到复合碳化硅衬底。

42.其中,所述设置碳化硅粉末层的碳化硅单晶层或碳化硅多晶层的表面平均粗糙度为1.5um。

43.其中,所述碳化硅粉末中六方相α-sic和立方相β-sic的质量比为1:1;所述碳化硅粉末中还含有al2o3和y2o3粉末;al2o3粉末的质量比小于6%;y2o3粉末的质量比小于4%;

44.其中,所述六方相α-sic、立方相β-sic、al2o3和y2o3的颗粒等效直径小于1um。

45.其中,所述第一目标温度为2000℃,保持时间为3小时;所述第二目标为1400℃,保持时间为3小时;所述第一目标温度降至第二目标温度的匀速降温速度为25℃/min。

46.其中,所述施加的压力为15mpa。

47.采用以上方法得到的复合碳化硅衬底翘曲度小于40um;碳化硅单晶层表面的平均粗糙度为1nm,碳化硅多晶层表面的平均粗超度小于100nm;所述复合碳化硅衬底为圆形,直径50mm-200mm,优选50mm、100mm、150mm,以及200mm。

48.所述抛光研磨,包括粗研磨,细研磨,化学机械抛光(cmp)等常规工艺,业内专业人员采用相应的设备,都可以实施。

49.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1