层叠线圈部件的制造方法与流程

1.本发明涉及一种层叠线圈部件的制造方法。

背景技术:

2.作为现有的层叠线圈部件的制造方法,例如已知有专利文献1(日本专利4816971号公报)所记载的方法。专利文献1所记载的层叠线圈部件的制造方法包括用于形成具有多个芯片的层叠体的层叠工序,该芯片包含被绝缘层内包的线圈体和与该线圈体的两端连接且从绝缘层露出的一对外部电极,层叠工序具有:使用导体膏通过光刻法在绝缘层上形成线圈体用的导体图案,并且在该绝缘层的边部上形成外部电极用的外部电极图案的第一过程;和使用绝缘膏通过光刻法在该导体图案和外部电极图案上形成绝缘层的第二过程,其中,该绝缘层具有观察导体图案的通路孔及与外部电极图案连续的切口部。

技术实现要素:

3.在层叠线圈部件中,期望小型化和特性提高。为了在层叠线圈部件中实现小型化和特性提高,需要减小相邻的导体图案间的绝缘体层的厚度。在现有的层叠线圈部件的制造方法中,同时形成设置于导体图案的周围的绝缘体层和导体图案间的绝缘体层。在该方法中,不能减小导体图案间的绝缘体层的厚度。

4.本发明的一方面的目的在于提供一种能够实现导体间的绝缘体层的薄层化的层叠线圈部件的制造方法。

5.本发明的一方面所涉及的层叠线圈部件的制造方法是具备:素体,其将多个绝缘体层层叠而形成;线圈,其配置于素体内,并且包含多个导体及将对应的导体彼此连接的通孔导体而构成的层叠线圈部件的制造方法,其中,所述制造方法包括:使用感光性绝缘体膏通过光刻法形成多个绝缘体层,使用感光性导电膏通过光刻法形成多个导体及通孔导体,形成第一导体的工序;以与第一导体的上表面成为平坦的方式形成第一绝缘体层的工序,所述第一绝缘体层设置于第一导体的周围;在第一导体及第一绝缘体层上形成设置有使第一导体的一部分露出的通路孔的第二绝缘体层的工序;以及在第二绝缘体层上形成经由通路孔与第一导体连接的第二导体的工序。

6.在本发明的一方面的层叠线圈部件的制造方法中,以与第一导体的上表面成为平坦的方式形成第一绝缘体层,在第一导体及第一绝缘体层上形成设置有通路孔的第二绝缘体层。即,以第一导体的厚度和第一绝缘体层的厚度同等的方式形成,在平坦的第一导体及第一绝缘体层的上表面形成第二绝缘体层。这样,在层叠线圈部件的制造方法中,在使第一导体和第一绝缘体层的高度一致后形成第二绝缘体层,因此,能够适当地进行第二绝缘体层的厚度的调整。因此,能够减小第二绝缘体层的厚度。因此,在层叠线圈部件的制造方法中,能够实现导体间的绝缘体层的薄层化。

7.在一个实施方式中,也可以是,在形成第一绝缘体层的工序中,在包含第一导体的区域的全部区域涂布了感光性绝缘体膏后,去除第一导体上的感光性绝缘体膏。在该方法

中,能够以与第一导体的上表面成为平坦的方式形成第一绝缘体层。

8.在一个实施方式中,在形成第二导体的工序中,也可以向通路孔中填充感光性导电膏,同时形成第二导体和通孔导体。在该方法中,能够同时形成第二导体和通孔导体,因此,能够实现制造工序的高效化。

9.在一个实施方式中,在形成第一绝缘体层的工序中,也可以使涂布于第一导体的周围的感光性导电膏的厚度大于涂布于第一导体上的感光性导电膏的厚度。在该方法中,容易将第一导体上的感光性导电膏平滑化,因此,容易进行线圈的磁路长度的调整。

10.根据本发明的一方面,能够实现导体间的绝缘体层的薄层化。

附图说明

11.图1是一个实施方式的层叠线圈部件的立体图。

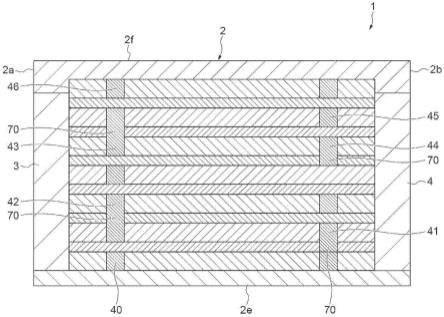

12.图2是表示层叠线圈部件的截面结构的图。

13.图3a、图3b、图3c、图3d、图3e及图3f是表示层叠线圈部件的制造工序的图。

14.图4a、图4b、图4c、图4d、图4e及图4f是表示层叠线圈部件的制造工序的图。

15.图5a、图5b、图5c及图5d是表示层叠线圈部件的制造工序的图。

具体实施方式

16.下面,参照附图对本发明的优选的实施方式进行详细地说明。此外,在附图的说明中对相同或相当要素标注相同的标号,省略重复的说明。

17.参照图1及图2对一个实施方式的层叠线圈部件进行说明。图1是一个实施方式的层叠线圈部件的立体图。图2是表示层叠线圈部件的截面结构的图。如图1及图2所示,层叠线圈部件1具备素体2、第一端子电极3和第二端子电极4以及线圈5。

18.素体2呈长方体形状。长方体形状包含角部及棱线部被倒角的长方体形状、以及角部及棱线部被弄圆的长方体形状。素体2具有端面2a、2b、主面2c、2d和侧面2e、2f作为外表面。端面2a、2b相互相对。主面2c、2d相互相对。侧面2e、2f相互相对。以下,将主面2c、2d的相对方向设为第一方向d1,将端面2a、2b的相对方向设为第二方向d2,并且将侧面2e、2f的相对方向设为第三方向d3。第一方向d1、第二方向d2及第三方向d3相互大致正交。

19.端面2a、2b以将主面2c、2d连结的方式沿第一方向d1延伸。端面2a、2b也以将侧面2e、2f连结的方式沿第三方向d3延伸。主面2c、2d以将端面2a、2b连结的方式沿第二方向d2延伸。主面2c、2d也以将侧面2e、2f连结的方式沿第三方向d3延伸。侧面2e、2f以将主面2c、2d连结的方式沿第一方向d1延伸。侧面2e、2f也以将端面2a、2b连结的方式沿第二方向d2延伸。

20.主面2d为安装面,例如为将层叠线圈部件1安装于未图示的其他电子设备(例如电路基材或层叠电子部件)时与其他电子设备相对的面。端面2a、2b为从安装面(即主面2d)连续的面。

21.在本实施方式中,素体2在第二方向d2上的长度比素体2在第三方向d3上的长度及素体2在第一方向d1上的长度长。素体2在第三方向d3上的长度和素体2在第一方向d1上的长度例如彼此同等。即,在本实施方式中,端面2a、2b呈正方形状,主面2c、2d及侧面2e、2f呈长方形状。素体2在第二方向d2上的长度可以与素体2在第三方向d3上的长度及素体2在第

一方向d1上的长度同等,也可以比这些长度短。素体2在第三方向d3上的长度及素体2在第一方向d1上的长度也可以互相不同。

22.此外,在本实施方式中,“同等”除了相等以外,还可以将包含预先设定的范围内的微差或制造误差等的值视为同等。例如,只要多个值包含在该多个值的平均值的

±

5%的范围内,就规定为该多个值同等。

23.在素体2的外表面设置有第一凹部7及第二凹部8。具体而言,第一凹部7设置于端面2a,朝向端面2b凹陷。第二凹部8设置于端面2b,朝向端面2a凹陷。

24.素体2由例如电介质材料(氧化铝、氧化镁、尖晶石、二氧化硅、镁橄榄石、滑石、顽火石、透辉石、堇青石、锶长石及硅酸锌中的任意一种以上)构成。素体2也可以由铁氧体(例如ni-cu-zn系铁氧体、ni-cu-zn-mg系铁氧体、cu-zn系铁氧体)形成。

25.第一端子电极3配置于素体2的端面2a侧。第二端子电极4配置于素体2的端面2b侧。第一端子电极3及第二端子电极4在第二方向d2上相互分离。第一端子电极3配置于第一凹部7内。第二端子电极4配置于第二凹部8内。第一端子电极3遍及端面2a及主面2d配置。第二端子电极4遍及端面2b及主面2d配置。在本实施方式中,第一端子电极3的表面与端面2a及主面2d分别大致齐平。第二端子电极4的表面与端面2b及主面2d分别大致齐平。第一端子电极3及第二端子电极4由导电材料(例如ag和/或pd)构成。

26.从第三方向d3观察,第一端子电极3呈l字状。第一端子电极3具有多个电极部分3a、3b。电极部分3a和电极部分3b在素体2的棱线部连接,且相互电连接。在本实施方式中,电极部分3a和电极部分3b一体地形成。电极部分3a沿第一方向d1延伸。从第二方向d2观察,电极部分3a呈长方形状。电极部分3b沿第二方向d2延伸。从第一方向d1观察,电极部分3b呈长方形状。各电极部分3a、3b沿第三方向d3延伸。

27.第一端子电极3是将多个第一电极层20、21、22、23、24、25、26(参照图5d)在第一方向d1上层叠而成的。即,第一电极层20~26的层叠方向为第一方向d1。在实际的第一端子电极3中,将多个第一电极层20~26一体化至其层间的边界不可辨识的程度。

28.从第三方向d3观察,第二端子电极4呈l字状。第二端子电极4具有多个电极部分4a、4b。电极部分4a和电极部分4b在素体2的棱线部连接,且相互电连接。在本实施方式中,电极部分4a和电极部分4b一体地形成。电极部分4a沿第一方向d1延伸。从第二方向d2观察,电极部分4a呈长方形状。电极部分4b沿第二方向d2延伸。从第一方向d1观察,电极部分4b呈长方形状。各电极部分4a、4b沿第三方向d3延伸。

29.第二端子电极4是将多个第二电极层30、31、32、33、34、35、36(参照图5d)在第一方向d1上层叠而成的。即,第二电极层30~36的层叠方向为第一方向d1。在实际的第二端子电极4中,将多个第二电极层30~36一体化至其层间的边界不可辨识的程度。

30.在第一端子电极3及第二端子电极4上也可以通过实施电镀或化学镀,设置含有例如ni、sn、au等的镀敷层(未图示)。镀敷层也可以具有例如含有ni且覆盖第一端子电极3及第二端子电极4的ni镀敷膜、和含有au且覆盖ni镀敷膜的au镀敷膜。

31.线圈5配置于素体2内。线圈5的一端通过连接导体48(参照图3a)与第一端子电极3连接。线圈5的另一端通过连接导体49(参照图5b)与第二端子电极4连接。如图2所示,线圈5包含多个线圈导体40、41、42、43、44、45、46及通孔导体70而构成。多个线圈导体40~46相互连接而构成线圈5。线圈5的线圈轴沿着第一方向d1设置。从第一方向d1观察,线圈导体40~

46以至少一部分相互重叠的方式配置。线圈导体40~46及通孔导体70远离端面2a、2b、主面2c、2d及侧面2e、2f而配置。线圈5由导电材料(例如ag和/或pd)构成。

32.接着,参照图3、图4及图5对层叠线圈部件1的制造方法的一例进行说明。在图3a~图3f、图4a~图4f及图5a~图5d中示出了制造工序中的俯视图和/或剖视图。在本实施方式中,使用光刻法制造层叠线圈部件1。本实施方式的“光刻法”只要为通过对包含感光性材料的加工对象的层进行曝光及显影,加工成希望的图案的方法即可,并不限定于掩膜的种类等。

33.如图3a所示,首先通过在基材b(例如pet膜)上涂布电介质材料,形成电介质层10。接着,在电介质层10上形成第一电极层20、第二电极层30、线圈导体(第一导体)40及连接导体48。第一电极层20、第二电极层30、线圈导体40及连接导体48使用光刻法形成。具体而言,在电介质层10上涂布感光性银膏(感光性导电膏)。接着,经由具有第一电极层20、第二电极层30、线圈导体40及连接导体48的图案的掩膜(例如cr掩膜)对感光性银膏照射紫外线使其曝光并且通过显影液进行显影,形成第一电极层20、第二电极层30、线圈导体40及连接导体48。第一电极层20和线圈导体40通过连接导体48电连接。下面,通过与上述光刻法同样的方法形成第一电极层21~26、第二电极层31~36、线圈导体41~46及连接导体49。

34.接着,如图3b所示,形成电介质层(第一绝缘体层)50。电介质层50形成于第一电极层20、第二电极层30及线圈导体40的周围。电介质层50使用光刻法形成。具体而言,在电介质层10、第一电极层20、第二电极层30、线圈导体40及连接导体48上涂布感光性电介质膏。即,以覆盖第一电极层20、第二电极层30、线圈导体40及连接导体48的全部区域的方式涂布感光性电介质膏。此时,涂布于第一电极层20、第二电极层30、线圈导体40及连接导体48上的感光性电介质膏的厚度小于涂布于其他区域的感光性电介质膏的厚度。即,涂布于除第一电极层20、第二电极层30、线圈导体40及连接导体48以外的区域的感光性电介质膏的厚度大于第一电极层20、第二电极层30、线圈导体40及连接导体48上的感光性电介质膏的厚度。

35.接着,经由具有第一电极层20、第二电极层30、线圈导体40及连接导体48的图案的掩膜对树脂膏照射紫外线使其曝光并且通过显影液进行显影,形成电介质层50。电介质层50以与线圈导体40(第一电极层20、第二电极层30)的上表面40a成为平坦的方式形成。即,以电介质层50的厚度和线圈导体40的厚度成为同等的方式形成电介质层50。下面,通过与上述光刻法同样的方法形成电介质层51~56。

36.在本实施方式中,“平坦”除了线圈导体40的上表面和电介质层50的上表面的高度位置相等以外,还可以包含预先设定的范围内的微差或制造误差等。例如,也可以包含相对于线圈导体40的高度(第一方向d1上的从电介质层10到上表面40a的距离)的平均值

±

2~3um的范围。此外,在线圈导体40的厚度和电介质层50的厚度不同的情况下,优选电介质层50的厚度大于线圈导体40的厚度。

37.接着,如图3c所示,形成电介质层(第二绝缘体层)60。电介质层60的厚度小于电介质层50的厚度。电介质层60使用光刻法形成。具体而言,在第一电极层20、第二电极层30、线圈导体40、连接导体48及电介质层50上涂布感光性电介质膏。接着,经由使第一电极层20、第二电极层30及线圈导体40的一部分曝光的掩膜对感光性电介质膏照射紫外线进行曝光并且通过显影液进行显影,形成电介质层60。电介质层60使第一电极层20、第二电极层30及

线圈导体40的一部分露出。在电介质层60上设置有通路孔bh。下面,通过与上述光刻法同样的方法形成电介质层61~65。

38.接着,如图3d所示,形成第一电极层21、第二电极层31及线圈导体(第二导体)41。具体而言,在第一电极层20、第二电极层30及电介质层50上涂布感光性银膏。由此,感光性银膏被填充到电介质层60的通路孔bh中。因此,同时形成线圈导体41和通孔导体70。第一电极层21形成于第一电极层20上。第一电极层21与第一电极层20电连接。第二电极层31形成于第二电极层30上。第二电极层31与第二电极层32电连接。线圈导体41经由通孔导体70与线圈导体40电连接。接着,如图3e所示,形成电介质层51。电介质层51形成于电介质层60上。接着,如图3f所示,形成电介质层61。电介质层61使第一电极层21、第二电极层31及线圈导体41的一部分露出。在电介质层61上设置有通路孔bh。

39.接着,如图4a所示,形成第一电极层22、第二电极层32及线圈导体42。具体而言,在第一电极层21、第二电极层31及电介质层51上涂布感光性银膏。由此,感光性银膏被填充到电介质层61的通路孔bh中。第一电极层22形成于第一电极层21上。第一电极层22与第一电极层21电连接。第二电极层32形成于第二电极层31上。第二电极层32与第二电极层31电连接。线圈导体42经由通孔导体70与线圈导体41电连接。接着,如图4b所示,形成电介质层52。电介质层52形成于电介质层61上。接着,如图4c所示,形成电介质层62。电介质层62使第一电极层22、第二电极层32及线圈导体42的一部分露出。在电介质层62上设置有通路孔bh。

40.接着,如图4d所示,形成第一电极层23、第二电极层33及线圈导体43。具体而言,在第一电极层22、第二电极层32及电介质层52上涂布感光性银膏。由此,感光性银膏被填充到电介质层62的通路孔bh中。第一电极层23形成于第一电极层22上。第一电极层23与第一电极层22电连接。第二电极层33形成于第二电极层32上。第二电极层33与第二电极层32电连接。线圈导体43经由通孔导体70与线圈导体42电连接。接着,如图4e所示,形成电介质层53。电介质层53形成于电介质层62上。接着,如图4f所示,形成电介质层63。电介质层63使第一电极层23、第二电极层33及线圈导体43的一部分露出。在电介质层63上设置有通路孔bh。

41.接着,如图5a所示,形成第一电极层24及第一电极层25。第一电极层24形成于第一电极层23上。第一电极层25形成于第一电极层24上。另外,形成第二电极层34及第二电极层35。第二电极层34形成于第二电极层33上。第二电极层35形成于第二电极层34上。

42.另外,形成线圈导体44及线圈导体45。线圈导体44经由通孔导体70与线圈导体43电连接。线圈导体45经由通孔导体70与线圈导体44电连接。

43.另外,形成电介质层54及电介质层55。电介质层54形成于电介质层63上。电介质层55形成于电介质层64上。另外,形成电介质层64及电介质层65。电介质层64形成于电介质层54上。电介质层65形成于电介质层55上。在电介质层64及电介质层65上分别设置有通路孔bh。

44.接着,如图5b所示,形成第一电极层26、第二电极层36、线圈导体46及连接导体49。第一电极层26形成于第一电极层25上。第二电极层36形成于第二电极层35上。线圈导体46经由通孔导体70与线圈导体45电连接。第二电极层36和线圈导体46通过连接导体49电连接。

45.接着,如图5c所示,形成电介质层56。电介质层56形成于电介质层65上。接着,如图5d所示,形成电介质层11。电介质层11形成于第一电极层26、第二电极层36及电介质层56

上。最后,对层叠体实施热处理并烧成。通过以上工序,可以得到层叠线圈部件1。根据需要,也可以在热处理后对第一端子电极3及第二端子电极4实施电镀或化学镀,设置镀敷层。

46.如以上所说明的,在本实施方式的层叠线圈部件1中,以与线圈导体40~45的上表面成为平坦的方式形成电介质层50~55,在线圈导体40~45及电介质层50~55上形成设置有通路孔bh的电介质层60~65。即,以线圈导体40~45的厚度和电介质层50~55的厚度成为同等的方式形成,在平坦的线圈导体40~45及电介质层50~55的上表面形成电介质层60~65。这样,在层叠线圈部件1的制造方法中,在使线圈导体40~45和电介质层50~55的高度一致后形成电介质层60~65,因此,能够适当地进行电介质层60~65的厚度的调整。因此,能够减小电介质层60~65的厚度。因此,在层叠线圈部件1的制造方法中,能够实现导体间的电介质层60~65的薄层化。

47.在本实施方式的层叠线圈部件1的制造方法中,在形成电介质层50~56的工序中,在包含线圈导体40~46的区域的全部区域涂布了感光性电介质膏后,去除线圈导体40~46上的感光性电介质膏。在该方法中,可以以与线圈导体40~46的上表面成为平坦的方式形成电介质层50~56。

48.在本实施方式的层叠线圈部件1的制造方法中,在形成线圈导体41、43、45的工序中,向通路孔bh中填充感光性导电膏,同时形成线圈导体41、43、45和通孔导体70。在该方法中,能够同时形成线圈导体41、43、45和通孔导体70,因此,能够实现制造工序的高效化。

49.在本实施方式的层叠线圈部件1的制造方法中,在形成电介质层50~56的工序中,使涂布于线圈导体40~46的周围的感光性导电膏的厚度大于涂布于线圈导体40~46上的感光性导电膏的厚度。在该方法中,容易将线圈导体40~46上的感光性导电膏平滑化,因此,容易进行线圈5的磁路长度的调整。

50.如上所述,对本发明的实施方式进行了说明,但本发明不必限定于上述的实施方式,在不脱离其主旨的范围内可以进行各种变更。

51.在上述实施方式中,以线圈5具有线圈导体40~46的实施方式为例进行了说明。但是,线圈导体的数量不限于上述的值。

52.在上述实施方式中,以从第三方向d3观察,第一端子电极3及第二端子电极4呈l字形状的实施方式为例进行了说明。但是,第一端子电极3及第二端子电极4的形状不限于此,也可以为例如长方体形状(从第二方向d2观察为矩形状)等。

53.在上述实施方式中,以在形成线圈导体41、43、45的工序中,向通路孔bh中填充感光性导电膏,同时形成线圈导体41、43、45和通孔导体70的实施方式为例进行了说明。但是,形成线圈导体41、43、45的时机与形成通孔导体70的时机也可以不同。

54.在上述实施方式中,以在形成电介质层50~56的工序中,使涂布于线圈导体40~46的周围的感光性导电膏的厚度大于涂布于线圈导体40~46上的感光性导电膏的厚度的实施方式为例进行了说明。但是,涂布于线圈导体40~46上的感光性导电膏的厚度和涂布于线圈导体40~46的周围的感光性导电膏的厚度也可以同等。

55.在上述实施方式中,以素体2由电介质材料形成的实施方式为例进行了说明。但是,素体2也可以由铁氧体形成。在该结构中,可以使用感光性铁氧体膏(感光性绝缘体膏)形成形成素体2的绝缘体层(相当于上述实施方式的电介质层50~56、60~65的层)。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1