多层基板表面处理层结构的制作方法

本揭示涉及多层基板,特别是涉及一种多层基板表面处理层结构。

背景技术:

1、请参阅图1,图1显示现有的多层基板表面处理层结构的示意图。

2、该多层基板表面处理层结构包括一介电层100、一导电种子层102、一焊垫层(padlayer)104、一保护金属层106以及一防焊层(solder mask layer)108。

3、制作该多层基板表面处理层结构时,先利用一光阻层(未图示)在该介电层100上方形成一凹槽110,再以溅镀或蒸镀等干式方法将该导电种子层102形成于该凹槽110底部,并与该介电层100接合,该导电种子层102做为该焊垫层104之种子(seed),接著移除该光阻层(未图示),利用电镀(electroplating)或化学镀(electroless plating)以该导电种子层102为中心往上及往旁边长出该焊垫层104,再利用电镀或化学镀于该焊垫层104上方及旁边形成该保护金属层106以完全包覆该焊垫层104,最后形成该防焊层108并部分露出或全部露出该保护金属层106。

4、欲将一外部组件焊接于铜材质之焊垫层104时,会使用锡材或其他焊剂以黏接该外部组件与该焊垫层104,该保护金属层106的目的即在于避免锡材或其他焊剂与该焊垫层104的铜接触产生互熔并形成介金属化合物(intermetalliccompound,imc),导致该多层基板表面处理层结构脆弱,产品可靠度降低。

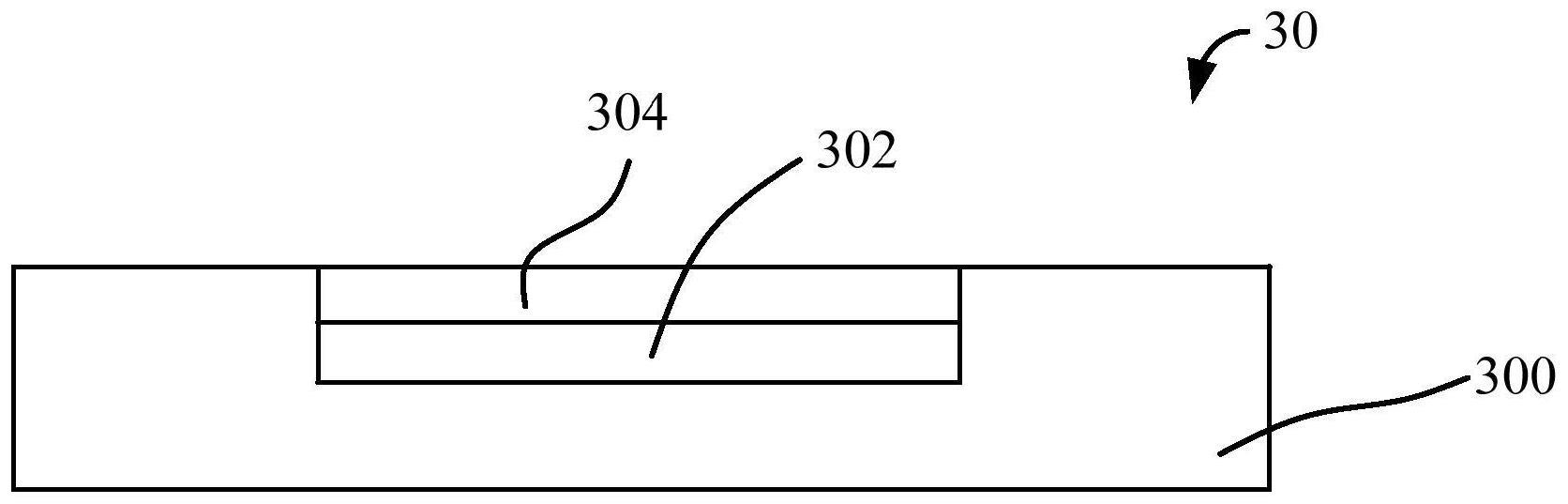

5、请参阅图2,图2显示另一现有的多层基板表面处理层结构的示意图。

6、图2之多层基板表面处理层结构与图1之多层基板表面处理层结构的差异在于在形成该导电种子层102后,不移除该光阻层(未图示),利用电镀或化学镀在该导电种子层102上形成该焊垫层104,然后才移除该光阻层(未图示)。

7、于图1与图2之多层基板表面处理层结构中,可以先形成该防焊层108,于该防焊层108形成一凹槽110,再于该凹槽110中形成该导电种子层102、该焊垫层104及该保护金属层106。也可以先完成焊垫层104及保护金属层106后再施作防焊层108,并在防焊层108中开口,露出保护金属层106。

8、然而,利用电镀或化学镀形成该焊垫层104及该保护金属层106时,会往该导电种子层102的旁边扩充,使该焊垫层104及该保护金属层106变宽,如图1所示。一般而言,若该焊垫层104的厚度为10微米(micrometer,μm),该焊垫层104一边的宽度会比该导电种子层102往外扩展约2至4微米,也就是说该焊垫层104整体(两边)的宽度会比该导电种子层102往外扩展约4至8微米。该保护金属层106整体(两边)的宽度会比该导电种子层102往外扩展约6至10微米。

9、图2之多层基板表面处理层结构中,该保护金属层106整体(两边)的宽度也会比该导电种子层102往外扩展约6至10微米。

10、再者,利用电镀或化学镀形成该焊垫层104及该保护金属层106均需在溶液中进行时,许多因素包括浓度、温度、材质等等皆会影响该焊垫层104及该保护金属层106往外扩展之范围,而使得最终含保护金属层之焊垫层之大小变得难以控制。

11、此外,在集成电路线距快速微缩的时代,相邻焊垫层之横向间距(pad pitch)越来越小,以符合超快速之集成电路晶圆的微缩速度;微缩速度在4年前约为10奈米(nanometer,nm),现今约为5奈米,公元2026年以后预期将推进到2奈米甚至1奈米。为了迎合晶圆的微缩,裸晶单元之相邻电性接点之间距亦将跟著快速缩小,预计由现今之80至100微米到5年后将成为30微米以下。在相邻焊垫层(用于与裸晶单元之电性接点电性连接)间距为30微米以下时,焊垫层之宽度将小于18微米,电镀或化学镀的不可预测之扩展必将成为图1及图2之焊垫层104及保护金属层106精细化之障碍。

12、另外,在先前技术中,焊垫层及保护金属层一般均会部分高于或低于介电层之一上表面,如此一来介电层及焊垫层间具有明显的高低差,此多层基板用于与芯片之金属露出表面产生对接时,将产生气泡,如此将伤害芯片封装之附著力。

13、因此,需要针对上述现有技术之问题提出解决方案。

技术实现思路

1、本揭示提供一种多层基板表面处理层结构,其能解决现有技术中的问题。

2、本揭示之多层基板表面处理层结构包括:一介电层;至少一焊垫层,形成于该介电层中;以及至少一保护金属层,形成于该至少一焊垫层上且与该至少一焊垫层接合,其中该至少一保护金属层主要仅包覆该至少一焊垫层之一上表面,该至少一保护金属层作为与一外部组件焊接或接触之区域,该至少一保护金属层之一上表面与该介电层之一上表面间无高低差。

3、本揭示之多层基板表面处理层结构包括:一介电层;至少一焊垫层,该至少一焊垫层的一部份形成于该介电层中;以及至少一保护金属层,形成于该至少一焊垫层上且与该焊垫层接合,其中该至少一保护金属层主要仅包覆该至少一焊垫层之一上表面,该至少一保护金属层作为与外部组件焊接或接触之区域,该至少一保护金属层之一上表面与该介电层之一上表面无高低差。

4、本揭示之多层基板表面处理层结构中,保护金属层主要仅包覆焊垫层之一上表面,不会从焊垫层的两边往外扩展,因此能解决现有技术中焊垫层及保护金属层不可预测之扩展而无法精细化的问题。再者,由于保护金属层之上表面与介电层之上表面无高低差,当多层基板表面处理层结构与芯片之金属露出表面产生完全对接时,该多层基板介电层及保护金属层之间的位置不会产生气泡,因此不会减弱将芯片封装之附著力,能避免多层基板表面与外部组件电性接触不良的问题,而达到相应之技术效果。此外,本揭示之多层基板表面处理结构中,由于保护金属层之上表面与介电层之上表面间无高低差,当多层基板表面处理结构与芯片之金属露出表面完全对接时,即使多层基板表面处理结构与芯片之金属露出表面完全密合且无间隙时,介电层与保护金属层之间的位置也不会产生气泡,此在高阶半导体封装为至关重要之技术效益果,若在多层基板与芯片完全密接时产生气泡,该气泡将随著芯片运作时散发之热量而膨胀,此时极可能将已对接之芯片电性连接点与电路板之焊垫部份由接触变为拉开,也就是由通路(short circuit)变成断路(open circuit)。

5、为让本揭示的上述内容能更明显易懂,下文特举优选实施例,并配合所附图式,作详细说明如下:

技术特征:

1.一种多层基板表面处理层结构,其特征在于,包括:

2.根据权利要求1所述的多层基板表面处理层结构,其特征在于,该介电层之材质为聚酰亚胺。

3.根据权利要求1所述的多层基板表面处理层结构,其特征在于,该至少一焊垫层之材质为铜。

4.根据权利要求1所述的多层基板表面处理层结构,其特征在于,该至少一保护金属层之材质选自于由铬、镍、钯及金所构成群组中之其中一者。

5.一种多层基板表面处理层结构,其特征在于,包括:

6.根据权利要求5所述的多层基板表面处理层结构,其特征在于,该介电层之材质为聚酰亚胺。

7.根据权利要求5所述的多层基板表面处理层结构,其特征在于,该至少一焊垫层之材质为铜。

8.根据权利要求5所述的多层基板表面处理层结构,其特征在于,该至少一保护金属层之材质选自于由铬、镍、钯及金所构成群组中之其中一者。

技术总结

一种多层基板表面处理层结构,包括:一介电层;至少一焊垫层,形成于介电层中;以及至少一保护金属层,形成于该至少一焊垫层上且与该焊垫层接合,其中该至少一保护金属层主要仅包覆该至少一焊垫层之一上表面,该至少一保护金属层作为与一外部组件焊接或接触之区域,该至少一保护金属层之一上表面与该介电层之一上表面间无高低差。

技术研发人员:邱丕良

受保护的技术使用者:巨擘科技股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!