半导体封装件的制作方法

半导体封装件

1.本技术基于2021年9月10日在韩国知识产权局提交的第10-2021-0121172号韩国专利申请并要求其优先权,该韩国专利申请的公开内容通过引用被完全包含于此。

技术领域

2.发明构思涉及一种半导体封装件,并且更具体地,涉及一种包括半导体芯片的半导体封装件。

背景技术:

3.在过去的几十年中,技术、材料和制造过程的探索已经使计算能力和无线通信技术得到快速发展。因此,使得高性能晶体管的高度集成成为可能,并且根据摩尔定律(moore's law),集成速度每18个月翻倍。半导体制造商不断地追求重量和尺寸的减小以及系统的功率效率,在似乎达到经济和物理限制的时间点,提出将系统实施在封装件中的系统封装作为有效的解决方案。

4.系统封装技术的示例包括逻辑电路和存储器电路的集成、传感器封装、微机电系统(mems)和互补金属-氧化物半导体(cmos)逻辑电路的异构集成(heterogeneous integration)。系统封装使得形状因子(form factor)的减小以及高可靠性、低功耗和低制造成本成为可能。因为近来的高度集成,所以已经对有效冷却由半导体封装件产生的大量热量的方法进行了研究。

技术实现要素:

5.发明构思将要解决的技术目标是提供一种具有改善的可靠性的半导体封装件。

6.发明构思提供了一种半导体封装件。所述半导体封装件包括:封装基底;中介体,布置在封装基底上,并且包括多个下垫和下保护层,下保护层包括暴露多个下垫的多个开口;多个导电连接器,将封装基底连接到中介体;半导体芯片,布置在封装基底与中介体之间;多个冷却片,布置在半导体芯片与中介体之间,并且具有圆柱形形状;以及绝缘填料,覆盖所述多个导电连接器、半导体芯片和所述多个冷却片,其中,所述多个冷却片中的每个冷却片的高度小于或者等于所述多个冷却片中的每个冷却片的直径,并且其中,所述多个冷却片中的每个冷却片的热导率比下保护层的热导率大。

7.根据示例实施例,提供了一种半导体封装件。所述半导体封装件包括:封装基底;中介体,布置在封装基底上,并且包括基体绝缘层和穿透基体绝缘层的多个硅通孔(tsv);多个导电连接器,将封装基底连接到中介体;半导体芯片,布置在封装基底与中介体之间;以及多个冷却片,布置在半导体芯片与中介体之间,并且具有圆柱形形状,其中,所述多个冷却片中的每个冷却片的高度小于或者等于所述多个冷却片中的每个冷却片的直径,并且其中,所述多个冷却片中的每个冷却片的热导率在10w/(m

·

k)至100w/(m

·

k)的范围内。

8.根据示例实施例,提供了一种半导体封装件。所述半导体封装件包括:再分布层,包括绝缘层、在水平方向上延伸的多个再分布图案、与所述多个再分布图案隔开且使绝缘

层在所述多个上再分布垫与所述多个再分布图案之间的多个上再分布垫、以及将所述多个再分布图案连接到所述多个再分布垫的多个再分布过孔;半导体芯片,布置在再分布层上;中介体,与再分布层间隔开且使半导体芯片在中介体与再分布层之间;多个冷却片,分别接触半导体芯片和中介体;以及绝缘填料,覆盖半导体芯片和所述多个冷却片,其中,所述多个冷却片各自包括焊料材料,并且各自具有硬币形状。

9.根据示例实施例,提供了一种半导体封装件的制造方法。所述制造方法包括:对其上安装有半导体芯片的封装基底设置多个第一导电连接器,并且对中介体设置多个第二导电连接器和多个冷却焊料;通过对多个冷却焊料进行模制来形成多个冷却片;通过将多个第一导电连接器和第二导电连接器结合来将中介体结合到封装基底;对中介体与封装基底之间的空间执行焊剂清洁工艺;以及设置覆盖半导体芯片、所述多个第一导电连接器和所述多个第二导电连接器以及所述多个冷却片的绝缘填料,其中,所述多个冷却片中的每个冷却片的热导率在10w/(m

·

k)至100w/(m

·

k)的范围内,并且其中,所述多个冷却片各自具有硬币形状。

附图说明

10.根据下面结合附图的详细描述,将更清楚地理解发明构思的实施例,在附图中:

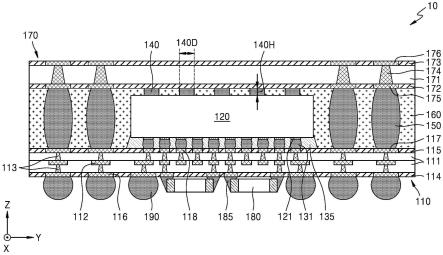

11.图1a是根据示例实施例的半导体封装件的剖视图;

12.图1b是示出冷却片的布置的平面图;

13.图2a是根据示例实施例的半导体封装件的剖视图;

14.图2b是示出冷却片和绝缘片的布置的平面图;

15.图3是根据其他示例实施例的半导体封装件的剖视图;

16.图4是根据其他示例实施例的半导体封装件的剖视图;

17.图5是根据其他示例实施例的半导体封装件的剖视图;

18.图6是根据示例实施例的半导体封装件的制造方法的流程图;

19.图7至图11是根据示例实施例的半导体封装件的制造方法的剖视图;

20.图12是根据示例实施例的半导体封装件的剖视图;

21.图13a是根据其他示例实施例的半导体封装件的平面图;以及

22.图13b是沿着图13a的线aa-aa'截取的半导体封装件的剖视图。

具体实施方式

23.在下文中,将参照附图详细地描述发明构思的一个或更多个实施例。附图中同样的附图标记指示同样的元件,并且将省略其重复描述。

24.图1a是根据示例实施例的半导体封装件10的剖视图。

25.图1b是示出半导体封装件10中的冷却片140的布置的平面图。在图1b中,为了方便,省略了除了半导体芯片120和冷却片140之外的组件。

26.参照图1a和图1b,半导体封装件10可以包括封装基底110、半导体芯片120、冷却片140、导电连接器150、绝缘填料160、中介体(interposer)170、无源元件180和外部连接端子190。

27.这里,平行于封装基底110的上表面并彼此垂直的两个方向限定为x方向和y方向,

与封装基底110的上表面垂直的方向限定为z方向。除非另有陈述,否则关于方向的限定在下面的附图中是相同的。

28.封装基底110可以是例如印刷电路板(pcb)。封装基底110可以包括基底基体111,基底基体111包括选自于酚醛树脂、环氧树脂和聚酰亚胺(pi)中的至少一种材料。此外,封装基底110可以包括布置在基底基体111的下表面上的下垫(pad,或被称为“焊盘”)116以及布置在基底基体111的上表面上的第一上垫117和第二上垫118。基底基体111可以包括被构造为电连接到第一上垫117、第二上垫118和下垫116中的至少任一者的导电图案112和导电过孔113。

29.导电图案112可以在封装基底110中在水平方向(例如,x方向和/或y方向)上延伸,并且导电过孔113可以在封装基底110中在竖直方向(例如,z方向)上延伸。导电过孔113中的每个可以从下保护层114到上保护层115逐渐变细(tapered),从而在从下保护层114到上保护层115的方向上逐渐变窄。例如,导电过孔113中的每个的宽度可以在下保护层114附近较大而在上保护层115附近较小。

30.上保护层115可以形成在基底基体111的上表面上,下保护层114可以形成在基底基体111的下表面上。暴露下垫116的下开口可以形成在下保护层114中,暴露第一上垫117和第二上垫118的开口可以形成在上保护层115中。在一些实施例中,下垫116的下表面和下保护层114的下表面可以彼此共面,第一上垫117的上表面、第二上垫118的上表面和上保护层115的上表面可以彼此共面。上保护层115和下保护层114可以包括例如阻焊剂。

31.导电图案112、导电过孔113、下垫116、第一上垫117和第二上垫118可以各自包括诸如以铜(cu)、铝(al)、钨(w)、钛(ti)、钽(ta)、铟(in)、钼(mo)、锰(mn)、钴(co)、锡(sn)、镍(ni)、镁(mg)、铼(re)、铍(be)、镓(ga)或钌(ru)为例的金属或其合金,但是材料不限于此。

32.导电连接器150可以分别附接到第一上垫117,芯片连接凸块131可以分别附接到第二上垫118。例如,导电连接器150可以接触第一上垫117的上表面,芯片连接凸块131可以接触第二上垫118的上表面。如这里使用的,除非上下文另有说明,否则术语“接触”指直接连接(即,触摸)。每个芯片连接凸块131可以是微凸块。

33.外部连接端子190可以分别附接到下垫116。外部连接端子190可以通过形成在下保护层114中的下开口分别连接到下垫116。外部连接端子190可以各自是例如焊料球。外部连接端子190可以提供半导体封装件10与外部装置之间的电连接。

34.半导体芯片120可以安装在封装基底110上。半导体芯片120可以在封装基底110与中介体170之间。半导体芯片120可以包括具有彼此相对的活性表面和非活性表面的半导体基底,并且可以包括形成在半导体基底的活性表面上的半导体器件层。半导体芯片120可以包括彼此相对的下表面和上表面。半导体芯片120可以包括布置在半导体芯片120的下表面上的芯片垫121。

35.半导体封装件10可以是扇出半导体封装件。例如,半导体芯片120的水平宽度和水平面积可以比封装基底110的水平宽度和水平面积小。

36.半导体芯片120的下表面可以与半导体基底的活性表面相邻,半导体芯片120的上表面可以与半导体基底的非活性表面相邻。半导体芯片120的芯片垫121可以通过半导体芯片120内部的布线结构(未示出)电连接到半导体器件层。

37.作为非限制性示例,半导体芯片120可以是逻辑芯片。例如,半导体芯片120可以包

括深度学习模型、微处理器、图形处理器、信号处理器、网络处理器、芯片组、音频编解码器、视频编解码器和应用处理器(ap)中的任何一者。

38.作为另一示例,半导体芯片120可以包括易失性存储器芯片和/或非易失性存储器芯片。易失性存储器芯片可以包括例如动态随机存取存储器(dram)、静态ram(sram)、晶闸管ram(tram)、零电容器ram(zram)或双晶体管ram(ttram)。此外,非易失性存储器芯片可以包括例如闪存、磁性ram(mram)、自旋转移矩mram(spin-transfer torque mram,stt-mram)、铁电ram(fram)、相变ram(pram)、电阻ram(rram)、纳米管rram、聚合物ram或绝缘体电阻变化存储器。

39.半导体芯片120可以以面朝下的方式或倒装芯片的方式安装在封装基底110上。例如,半导体芯片120的其上形成有芯片垫121的下表面可以面对封装基底110。半导体芯片120的芯片垫121可以通过芯片连接凸块131分别电连接到第二上垫118。芯片垫121可以用作用于传输半导体芯片120的输入/输出数据信号的端子或用于半导体芯片120的电力和/或接地连接的端子。

40.覆盖芯片连接凸块131的底部填充材料层135可以布置在半导体芯片120与封装基底110之间。例如,底部填充材料层135可以包括通过毛细管底部填充工艺形成的环氧树脂。作为另一示例,底部填充材料层135可以是非导电膜。作为另一示例,绝缘填料160可以根据模制底部填充方法来直接填充半导体芯片120与封装基底110之间的间隙,并且在这种情况下,可以省略底部填充材料层135。

41.中介体170可以布置在封装基底110和半导体芯片120上。中介体170可以包括基体绝缘层171、下保护层172、上保护层173、导电过孔174、下垫175和上垫176。

42.基体绝缘层171可以包括选自于酚醛树脂、环氧树脂和pi中的至少一种材料。例如,基体绝缘层171可以包括选自于pi、fr-4(flame retardant 4)、四官能环氧树脂、聚苯醚、环氧树脂/聚苯醚、双马来酰亚胺三嗪(bt)、热固树脂、氰酸酯和液晶聚合物中的至少一种材料。

43.上垫176可以布置在基体绝缘层171的上表面上。下垫175可以布置在基体绝缘层171的下表面上。导电过孔174可以穿透基体绝缘层171。在上垫176上,可以设置诸如焊料和凸块的外部连接端子。上垫176可以提供与安装在中介体170上的半导体芯片或半导体封装件的连接。

44.下垫175可以分别接触导电连接器150。每个下垫175可以通过导电连接器150连接到第一上垫117中的任何对应的一个。因此,可以在封装基底110与中介体170之间形成电连接。

45.导电过孔174可以分别接触上垫176和下垫175。每个下垫175可以通过导电过孔174电连接到上垫176中的任何对应的一个。导电过孔174可以在从下垫175到上保护层173的方向上逐渐变窄。例如,导电过孔174可以随着它们远离下垫175延伸而逐渐变细。

46.导电过孔174、下垫175和上垫176可以包括与导电图案112、导电过孔113、下垫116以及第一上垫117和第二上垫118有关的前述材料中的任何一种。

47.上保护层173可以布置在基体绝缘层171的上表面上,下保护层172可以布置在基体绝缘层171的下表面上。上保护层173可以覆盖基体绝缘层171的上表面。上保护层173可以包括上开口,上垫176通过上开口暴露。下保护层172可以覆盖基体绝缘层171的下表面。

下保护层172可以包括下开口,下垫175通过下开口暴露。上保护层173和下保护层172可以包括例如阻焊剂。

48.导电连接器150可以具有在中介体170的下垫175与封装基底110的第一上垫117之间沿z方向延伸的柱形状。导电连接器150的下部可以分别接触封装基底110的第一上垫117。导电连接器150的上部可以分别接触中介体170的下垫175。根据示例实施例,导电连接器150可以包括导电材料。根据示例实施例,导电连接器150中的每个可以包括焊料材料。根据示例实施例,导电连接器150中的每个可以包括cu、sn、铅(pb)等。根据示例实施例,导电连接器150中的每个可以包括包含cu、sn和pb中的至少一些的合金材料。

49.冷却片140可以布置在半导体芯片120与中介体170之间。冷却片140可以分别接触中介体170的下保护层172的下表面和半导体芯片120的上表面。

50.根据示例实施例,因为计算能力和工作负荷在集成电路的部分中是局部高的,所以半导体芯片120可以包括具有高热值的热点(hot spot)120h。例如,热点120h可以是在半导体芯片120被驱动时半导体芯片120的温度的局部最大点(local maximum point)。

51.根据示例实施例,冷却片140可以布置为在半导体芯片120上形成行和列。根据示例实施例,冷却片140可以彼此水平地分开。

52.根据示例实施例,冷却片140中的一些可以与热点120h相邻。根据示例实施例,冷却片140中的一些可以在z方向上与热点120h叠置。根据示例实施例,冷却片140中的一些可以接触热点120h。然而,一个或更多个实施例不限于此,冷却片140可以任意布置,以有效地冷却半导体芯片120。

53.根据示例实施例,每个冷却片140可以具有硬币形状。例如,每个冷却片140可以呈具有相对小的高宽比(aspect ratio)的圆柱形形状。这里,高宽比可以是冷却片140的高度140h与冷却片140的直径140d的比率。每个冷却片140的高宽比可以小于或者等于约1。每个冷却片140的高宽比可以等于或者大于约1/20。剖视图上的冷却片140的侧面轮廓可以是线性的。

54.根据示例实施例,每个冷却片140的高度140h可以小于或者等于每个冷却片140的直径140d。根据示例实施例,每个冷却片140的高度140h可以在约10μm至约100μm的范围内。根据示例实施例,每个冷却片140的直径140d可以在约50μm至约200μm的范围内。

55.根据示例实施例,每个冷却片140可以与导电连接器150包括相同的材料。根据示例实施例,每个冷却片140可以包括焊料材料。根据示例实施例,每个冷却片140可以包括cu、sn、pb等。根据示例实施例,每个冷却片140可以包括包含cu、sn和pb中的至少一些的合金材料。

56.根据示例实施例,每个冷却片140可以包括具有高热导率的材料。根据示例实施例,每个冷却片140的热导率可以在约10w/(m

·

k)至约100w/(m

·

k)的范围内。每个冷却片140的热导率可以在约20w/(m

·

k)至约80w/(m

·

k)的范围内。根据示例实施例,每个冷却片140的热导率可以比下保护层172的热导率大。

57.根据示例实施例,具有高热导率的冷却片140可以与半导体芯片120的热点120h相邻。因此,可以改善半导体封装件10的冷却效率和可靠性。

58.根据示例实施例,冷却片140可以保持半导体芯片120与中介体170之间的间隙。因为冷却片140,半导体封装件10可以确保足够用于焊剂清洁(flux cleaning)的空间,其中,

所述空间在半导体芯片120与中介体170之间。因此,可以防止由于不充分的焊剂清洁导致的下保护层172从基体绝缘层171脱离。

59.此外,当在制造工艺期间向半导体封装件10施加热和压力时,冷却片140可以防止包括焊料等的导电连接器150的变形。因此,可以改善半导体封装件10在z方向上的高度的均匀性,并且可以防止半导体封装件10的弯曲。

60.无源元件180可以布置在封装基底110的下表面上。无源元件180可以各自为表面安装器件(smd)。例如,至少一个无源元件180可以包括电容器元件(例如,硅电容器、低电感陶瓷电容器(licc)和多层陶瓷电容器(mlcc))以及电阻元件。无源元件180可以分别通过连接端子185电连接到下垫116。每个无源元件180可以通过连接端子185固定到下垫116。

61.绝缘填料160可以设置在封装基底110上。绝缘填料160可以保护封装基底110、半导体芯片120、冷却片140、导电连接器150和中介体170免受外部环境的影响。绝缘填料160可以覆盖封装基底110、半导体芯片120、冷却片140、导电连接器150和中介体170中的每个的至少一些部分。例如,绝缘填料160可以覆盖封装基底110的上表面、半导体芯片120的侧表面和上表面、冷却片140的侧表面、导电连接器150的侧表面以及中介体170的下表面。在一些实施例中,绝缘填料160的上表面可以与冷却片140的上表面和导电连接器150的上表面共面,并且绝缘填料160的下表面可以与芯片连接凸块131的下表面、底部填充材料层135的下表面和导电连接器150的下表面共面。

62.根据示例实施例,绝缘填料160可以填充冷却片140之间的间隙。根据示例实施例,绝缘填料160可以水平地围绕每个冷却片140。

63.根据示例实施例,绝缘填料160可以包括环氧基模塑树脂、聚酰亚胺基模塑树脂等。例如,绝缘填料160可以包括环氧模塑化合物(emc)。

64.图2a是根据示例实施例的半导体封装件11的剖视图。

65.图2b是示出冷却片140和绝缘片142的布置的平面图。在图2b中,为了便于解释,省略除了半导体芯片120、冷却片140和绝缘片142之外的部件。

66.参照图2a和图2b,半导体封装件11可以包括封装基底110、半导体芯片120、冷却片140、绝缘片142、导电连接器150、绝缘填料160、中介体170、无源元件180和外部连接端子190。

67.封装基底110、半导体芯片120、导电连接器150、绝缘填料160、中介体170、无源元件180和外部连接端子190与参照图1a和图1b描述的那些基本相同,因此不提供其重复描述。

68.根据示例实施例,冷却片140和绝缘片142可以布置在半导体芯片120与中介体170之间。根据示例实施例,冷却片140和绝缘片142可以各自接触中介体170的下保护层172的下表面和半导体芯片120的上表面。每个冷却片140的高度可以与每个绝缘片142的高度基本相同。

69.根据示例实施例,冷却片140和绝缘片142可以布置为在半导体芯片120上形成行和列。根据示例实施例,冷却片140可以与绝缘片142水平地分开。

70.根据示例实施例,绝缘片142可以在水平方向上与热点120h间隔开。根据示例实施例,每个热点120h与最靠近的一个绝缘片142之间的距离可以比每个热点120h与最靠近的一个冷却片140之间的距离大。根据示例实施例,绝缘片142在z方向上可以不与热点120h叠

置。

71.每个冷却片140可以具有比绝缘片142的热导率高的热导率。每个冷却片140的热导率可以在绝缘片142的热导率的约20倍至约100倍的范围内。每个绝缘片142的热导率可以小于或者等于约1w/(m

·

k)。每个绝缘片142的热导率可以为约0.3w/(m

·

k)。每个绝缘片142可以包括阻焊剂。

72.当从顶部观察时,每个绝缘片142的平面形状是方形(square)。然而,这仅是示例,并且发明构思的技术精神不限于此。绝缘片142的平面形状可以是例如多边形(诸如三角形、五边形或六边形)、圆形或椭圆形。

73.根据示例实施例,除了冷却片140之外,绝缘片142也布置在半导体芯片120与中介体170之间,因此,可以防止导电连接器150和冷却片140在形成导电连接器150的热压缩工艺期间变形。

74.绝缘填料160还可以覆盖绝缘片142。绝缘填料160可以填充绝缘片142之间的间隙以及绝缘片142与冷却片140之间的间隙。

75.图3是根据其他示例实施例的半导体封装件12的剖视图。

76.参照图3,半导体封装件12可以包括封装基底110、半导体芯片120、冷却片140、散热器件145、导电连接器150、绝缘填料160、中介体170'、无源元件180和外部连接端子190。

77.封装基底110、半导体芯片120、导电连接器150、绝缘填料160、无源元件180和外部连接端子190与参照图1a和图1b描述的那些基本相同,因此不提供其重复描述。

78.根据示例实施例,除了包括基体绝缘层171、下保护层172、上保护层173、导电过孔174、下垫175和上垫176之外,中介体170'还可以包括导热硅通孔(through silicon via,tsv)177、下导热垫178和上导热垫179。基体绝缘层171、下保护层172、上保护层173、导电过孔174、下垫175和上垫176与参照图1a和图1b描述的那些基本相同,因此不提供其重复描述。

79.根据示例实施例,下导热垫178和上导热垫179可以是电虚设垫(electrical dummy pad)。根据示例实施例,下导热垫178和上导热垫179可以与连接到封装基底110和半导体芯片120或中介体170'中的任一者的外部电路绝缘。根据示例实施例,下导热垫178和上导热垫179可以是电浮置的。

80.根据示例实施例,下导热垫178可以分别接触冷却片140。根据示例实施例,上导热垫179可以在z方向上分别与下导热垫178叠置。上导热垫179可以通过导热tsv 177分别连接到下导热垫178。例如,导热tsv 177的上表面可以接触上导热垫179的下表面,导热tsv 177的下表面可以接触下导热垫178的上表面。根据示例实施例,下导热垫178、导热tsv 177和上导热垫179可以向冷却片140提供散热路径。导热tsv 177可以具有与导电过孔174的形状相同的形状,并且可以由相同的材料制成。例如,导热tsv 177可以在从下导热垫178到上导热垫179的方向上逐渐变窄。

81.根据示例实施例,散热器件145可以在中介体170'上。散热器件145可以通过诸如凸块的连接端子146分别连接到上导热垫179。根据示例实施例,散热器件145可以包括具有高热导率的材料。散热器件145可以包括例如散热块(heat slug)。

82.根据示例实施例,除了设置冷却片140之外,也可以通过设置散热器件145来改善半导体封装件12的冷却效率。

83.图4是根据其他示例实施例的半导体封装件13的剖视图。

84.参照图4,半导体封装件13可以包括再分布层210、半导体芯片120、冷却片140、导电连接器150、绝缘填料160、中介体170、无源元件180和外部连接端子190。

85.半导体芯片120、导电连接器150、绝缘填料160、中介体170、无源元件180和外部连接端子190与参照图1a和图1b描述的那些基本相同,因此不提供其重复描述。

86.根据示例实施例,半导体封装件13可以是芯片最后(chip last)扇出晶圆级半导体封装件,在这种封装件中,首先形成再分布层210然后将中介体170和至少一个半导体芯片120安装在再分布层210上。

87.再分布层210可以包括绝缘层211、下再分布垫212、第一上再分布垫213和第二上再分布垫214、再分布图案215以及再分布过孔216。

88.绝缘层211可以在z方向上堆叠(层叠)。绝缘层211可以覆盖再分布图案215和再分布过孔216。绝缘层211可以暴露下再分布垫212的下表面以及第一上再分布垫213的上表面和第二上再分布垫214的上表面。

89.绝缘层211可以各自包括绝缘材料。绝缘层211可以各自包括例如包含有机化合物的材料膜。根据示例实施例,每个绝缘层211可以包括诸如感光性聚酰亚胺(pspi)的感光成像电介质(pid)、ajinomoto堆积膜(abf)等。

90.通过绝缘层211暴露的下再分布垫212可以分别连接到外部连接端子190。例如,外部连接端子190可以接触下再分布垫212的下表面。通过绝缘层211暴露的第一上再分布垫213可以分别连接到导电连接器150。例如,第一上再分布垫213的上表面可以接触导电连接器150的下表面。通过绝缘层211暴露的第二上再分布垫214可以分别连接到芯片连接凸块131。例如,第二上再分布垫214的上表面可以接触芯片连接凸块131。

91.再分布图案215可以具有在水平方向(即,x方向和y方向)上纵向延伸的线性形状。再分布过孔216可以通过穿透绝缘层211而在z方向上延伸,并且可以将处于不同水平(层级)的再分布图案215彼此连接,或者可以将下再分布垫212以及第一上再分布垫213和第二上再分布垫214连接到相邻的再分布图案215。

92.根据示例实施例,再分布过孔216可以在向下方向(即,远离半导体芯片120的方向)上逐渐变细。例如,每个再分布过孔216的水平宽度可以远离半导体芯片120减小。然而,一个或更多个实施例不限于此。类似于图5的再分布过孔216',再分布过孔216可以在向上方向(即,朝向半导体芯片120的方向)上逐渐变细。

93.下再分布垫212、第一上再分布垫213和第二上再分布垫214、再分布图案215以及再分布过孔216可以各自包括诸如cu、al、w、ti、ta、in、mo、mn、co、sn、ni、mg、re、be、ga或ru的金属或者其合金。

94.种子层可以布置在再分布图案215与绝缘层211之间以及再分布过孔216与绝缘层211之间。例如,种子层可以通过物理气相沉积来形成,再分布图案215和再分布过孔216可以通过基于种子层的无电镀(electroless plating,或被称为“化学镀”)来形成。

95.种子层可以包括例如cu、ti、tiw、氮化钛(tin)、ta、氮化钽(tan)、铬(cr)、al等。作为另一示例,种子层可以具有多层结构,诸如cu/ti或cu/tiw。当再分布图案215和再分布过孔216包括cu时,种子层可以防止cu扩散到绝缘层211。

96.图5是根据其他示例实施例的半导体封装件14的剖视图。

97.参照图5,半导体封装件14可以包括再分布层210'、半导体芯片120、冷却片140、连接结构156、绝缘填料160、中介体170、无源元件180和外部连接端子190。

98.半导体芯片120、绝缘填料160、中介体170、无源元件180和外部连接端子190与参照图1a和图1b描述的那些基本相同,因此,不提供其重复描述。

99.根据示例实施例,半导体封装件14可以是扇出面板级封装件(foplp)。例如,半导体封装件14可以通过在连接结构156上形成再分布层210'然后将中介体170附接到连接结构156来形成。连接结构156可以是分离的面板。因此,可以同时对大量半导体芯片120执行封装工艺,并且可以改善半导体封装件14的生产率。

100.再分布层210'可以包括绝缘层211、下再分布垫212、第一上再分布垫213和第二上再分布垫214、再分布图案215以及再分布过孔216'。除了再分布过孔216'具有在向上方向上逐渐变细的结构之外,再分布层210'与参照图4描述的再分布层210基本类似。

101.连接结构156可以包括绝缘层157和穿透绝缘层157的tsv 158。绝缘层157可以水平地围绕半导体芯片120。连接端子159可以设置在tsv 158与下垫175之间。可以设置连接端子159,以用于tsv 158与下垫175之间的电连接。

102.作为另一示例,可以省略连接端子159,并且tsv 158可以通过直接接合分别结合到下垫175。此外,示出了两个绝缘层157和tsv 158,但是再分布层210'可以通过单个绝缘层和单个tsv连接到中介体170。

103.图6是根据示例实施例的半导体封装件的制造方法的流程图。

104.图7至图11是根据示例实施例的半导体封装件的制造方法的剖视图。

105.参照图6至图8,在p110中,可以对封装基底110设置第一导电连接器151并且可以对中介体170设置第二导电连接器152和冷却焊料141。例如,可以在封装基底110的第一上垫117上设置第一导电连接器151,可以在中介体170的下垫175上设置第二导电连接器152,并且可以在中介体170的下保护层172上设置冷却焊料141。

106.根据示例实施例,第一导电连接器151、第二导电连接器152和冷却焊料141可以包括导电材料。根据示例实施例,第一导电连接器151、第二导电连接器152和冷却焊料141中的每个可以包括焊料材料。根据示例实施例,第一导电连接器151、第二导电连接器152和冷却焊料141可以包括cu、sn、pb等。根据示例实施例,第一导电连接器151、第二导电连接器152和冷却焊料141中的每个可以包括cu、sn和pb中的至少一些的合金材料。

107.每个冷却焊料141的高度(即,在z方向上的长度)和最大水平宽度(即,在x方向或y方向上的长度)可以为数百微米(μm)。每个冷却焊料141的高度(即,在z方向上的长度)和最大水平宽度(即,在x方向或y方向上的长度)可以为约50μm。

108.参照图6、图8和图9,在p120中,可以通过对冷却焊料141进行模制来形成冷却片140。可以通过冷却焊料141被压缩的压印工艺(coining process)来形成冷却片140。可以通过例如热压缩工艺来形成冷却片140。

109.参照图6和图10,在p130中,可以将中介体170结合到封装基底110。

110.将中介体170结合到封装基底110的步骤可以包括:通过对第一导电连接器151和第二导电连接器152进行回流或热压缩来形成导电连接器150。

111.在将中介体170结合到封装基底110之后,可以执行焊剂清洁工艺。可以使用水基ph中性清洁剂或者使用碱性清洁剂执行焊剂清洁。焊剂清洁可以包括分批式清洁工艺、浴

式清洁工艺和超声沉淀清洁工艺中的任何一种。根据示例实施例,由于冷却焊料141而可以在半导体芯片120与中介体170之间提供足够用于焊剂清洁的空间,因此可以防止对下保护层172的损坏。

112.参照图6和图11,在p140中,可以设置覆盖半导体芯片120、冷却片140和导电连接器150的绝缘填料160。参照图1a,在设置绝缘填料160之后,可以在封装基底110的下表面上进一步设置外部连接端子190和无源元件180。

113.到目前为止已经描述了图1a的半导体封装件10的制造方法。基于这里的描述,本领域普通技术人员可以容易地实践参照图2a至图5描述的半导体封装件11至半导体封装件14的制造方法。

114.图12是根据示例实施例的半导体封装件500的剖视图。

115.参照图12,半导体封装件500可以包括半导体封装件10和半导体封装件30。半导体封装件500可以是半导体封装件30堆叠在半导体封装件10上的层叠封装件类型。

116.半导体封装件30可以包括半导体芯片310、封装基底330和模制层350。

117.封装基底330可以是例如pcb。封装基底330可以包括基底基体331,基底基体331包括选自酚醛树脂、环氧树脂和pi中的至少一种材料。此外,封装基底330可以包括布置在基底基体331的上表面上的上垫335和布置在基底基体331的下表面上的下垫334。在基底基体331中,可以形成被构造为电连接到上垫335和下垫334的布线336。在基底基体331的上表面上,可以布置覆盖所述上表面并暴露上垫335的上保护层333。在基底基体331的下表面上,可以布置覆盖所述下表面并暴露下垫334的下保护层332。

118.封装基底330可以安装在中介体170上。封装基底330可以通过布置在中介体170上的连接端子360连接到中介体170。连接端子360可以分别连接到中介体170的上垫176和封装基底330的下垫334,并且可以将中介体170的上垫176电连接到封装基底330的下垫334。在示例实施例中,连接端子360可以接触中介体170的上垫176的顶表面和封装基底330的下垫334的下表面。

119.半导体芯片310可以布置在封装基底330上。例如,半导体芯片310的芯片垫315可以通过芯片连接凸块320电连接到封装基底330的上垫335。底部填充材料层340可以布置在半导体芯片310与封装基底330之间,底部填充材料层340围绕芯片连接凸块320。

120.根据示例实施例,半导体芯片120可以是与半导体芯片310相同的类型。

121.根据示例实施例,半导体芯片120可以是与半导体芯片310不同的类型。例如,当半导体芯片120是逻辑芯片时,半导体芯片310可以是存储器芯片。

122.根据示例实施例,半导体芯片310可以实施为高带宽存储器(hbm)芯片。根据示例实施例,半导体封装件500可以用作如不同类型的半导体芯片和组件(诸如无源元件)彼此电连接的系统。

123.模制层350可以布置在封装基底330上,以覆盖半导体芯片310的至少一部分。模制层350可以包括例如环氧基模塑树脂或pi基模塑树脂。例如,模制层350可以包括emc。

124.到目前为止已经描述了包括图1a的半导体封装件10的半导体封装件500,但是本领域普通技术人员基于这里的描述可以容易地实践包括图2a至图5的半导体封装件11至半导体封装件14的示例。

125.图13a是根据其他示例实施例的半导体封装件1000的平面图。

126.图13b是沿着图13a的线aa-aa'截取的半导体封装件1000的剖视图。

127.参照图13a和图13b,半导体封装件1000可以包括封装基底1100、中介体1200、第一半导体芯片1310、第二半导体芯片1320、冷却片1410和散热器件1400。

128.封装基底1100可以包括基底基体1110以及分别布置在基底基体1110的上表面和下表面上的基底上垫1120和基底下垫1130。根据示例实施例,封装基底1100可以是pcb。例如,封装基底1100可以是多层pcb。基底基体1110可以包括酚醛树脂、环氧树脂和pi中的任何一种。被构造为将外部装置电连接到半导体封装件1000的外部连接端子1140可以连接到基底下垫1130。

129.板-中介体连接凸块1283可以设置在基底上垫1120上。板-中介体连接凸块1283的尺寸可以比连接凸块1330的尺寸大。封装基底1100可以通过板-中介体连接凸块1283连接到中介体1200。

130.中介体1200可以包括布置在下导电垫1230上的下连接柱1281。下连接柱1281可以通过第二下保护层1253中的开口连接到下导电垫1230。下连接柱1281可以是凸块下金属(under bump metallurgy)。下连接柱1281可以包括ni、cu、pd、铂(pt)、金(au)或它们的组合。

131.封装基底1100可以通过板-中介体连接凸块1283电连接到中介体1200。半导体封装件1000可以包括布置在中介体1200与封装基底1100之间的第一绝缘填料1285。

132.第一绝缘填料1285可以填充中介体1200与封装基底1100之间的间隙,并且覆盖板-中介体连接凸块1283。例如,第一绝缘填料1285可以包括诸如环氧树脂的基体材料层和包含在基体材料层中的填料。

133.中介体1200可以包括tsv层1201和再分布层1202。tsv层1201可以包括基体层1210、tsv 1220、下导电垫1230、上导电垫1240、第一下保护层1251和第二下保护层1253。基体层1210可以包括半导体材料、玻璃、陶瓷或塑料。根据示例实施例,基体层1210可以包括硅晶圆,所述硅晶圆包括晶体硅、多晶硅或非晶硅。基体层1210可以是基本平面的。

134.第一下保护层1251可以覆盖基体层1210的下表面。此外,第一下保护层1251可以覆盖tsv 1220的从基体层1210的下表面突出的侧壁。根据示例实施例,第一下保护层1251可以包括无机绝缘材料。例如,第一下保护层1251可以包括氧化硅和氮化硅中的至少一种。

135.下导电垫1230可以布置在第一下保护层1251的下表面上。例如,下导电垫1230可以是分别连接到板-中介体连接凸块1283的垫。下导电垫1230可以包括例如w、al、cu等。

136.第二下保护层1253可以覆盖第一下保护层1251的下表面以及下导电垫1230的一些部分。第二下保护层1253可以包括开口,下导电垫1230的下表面中的一些通过所述开口暴露。板-中介体连接凸块1283可以通过第二下保护层1253中的开口连接到下导电垫1230。

137.根据示例实施例,第二下保护层1253可以包括与第一下保护层1251不同的材料。第一下保护层1251可以包括无机绝缘材料,第二下保护层1253可以包括有机绝缘材料。根据示例实施例,第二下保护层1253可以包括诸如pi、聚苯并噁唑(pbo)的pid等。

138.中介体1200可以包括布置在下导电垫1230上的下连接柱1281。下连接柱1281可以通过第二下保护层1253中的开口连接到下导电垫1230,并且可以接触第二下保护层1253的覆盖下导电垫1230的下表面的边缘部分的部分。下连接柱1281可以是凸块下金属。下连接柱1281可以包括ni、cu、pd、pt、au或它们的组合。在一些情况下,可以省略下连接柱1281。

139.tsv 1220可以被构造为将上导电垫1240电连接到下导电垫1230。tsv1220可以从基体层1210的上表面延伸到基体层1210的下表面,并且可以在竖直方向上穿透基体层1210。此外,tsv 1220还可以穿透第一下保护层1251。tsv 1220的上端可以连接到上导电垫1240,tsv 1220的下端可以连接到下导电垫1230。

140.再分布层1202可以布置在tsv层1201的上表面上。再分布层1202可以包括电连接到上导电垫1240的再分布图案1271和1273。再分布层1202还可以包括覆盖基体层1210的上表面的绝缘层1260。绝缘层1260可以覆盖上导电垫1240以及再分布图案1271和1273。再分布层1202可以包括后端制程(back-end-of-line,beol)结构。

141.根据示例实施例,绝缘层1260可以包括无机绝缘材料。例如,绝缘层1260可以包括氧化硅和氮化硅中的至少一种。根据另一示例实施例,绝缘层1260可以包括有机绝缘材料。例如,绝缘层1260可以包括诸如pi的pid。

142.再分布图案1271可以包括在水平方向上延伸的线部以及在竖直方向上延伸的过孔部。再分布图案1273可以包括用于电连接到第一半导体芯片1310和第二半导体芯片1320的垫部以及用于连接到再分布图案1271的过孔部。再分布图案1271和1273可以包括例如选自w、al和cu中的至少一种金属。

143.第一半导体芯片1310和第二半导体芯片1320可以安装在中介体1200上。第一半导体芯片1310和第二半导体芯片1320可以在中介体1200的再分布层1202上沿水平方向彼此间隔开。第一半导体芯片1310和第二半导体芯片1320可以以倒装芯片方式(flip-chip manner)安装在中介体1200上。第一半导体芯片1310的芯片垫1311和第二半导体芯片1320的芯片垫1321可以通过连接凸块1330电连接到再分布图案1273。第一半导体芯片1310的芯片垫1311和第二半导体芯片1320的芯片垫1321可以用作用于输入/输出数据信号传输的端子或用于电力和/或接地连接的端子。

144.例如,布置在半导体封装件1000的水平中心上的第一半导体芯片1310可以是逻辑芯片,而布置在第一半导体芯片1310的边缘上的第二半导体芯片1320可以是存储器芯片。根据示例实施例,第一半导体芯片1310的第一水平面积可以比作为每个第二半导体芯片1320的水平面积的第二水平面积大。

145.根据示例实施例,每个第二半导体芯片1320可以包括易失性存储器芯片和/或非易失性存储器芯片。易失性存储器芯片的示例可以包括dram、sram、tram、zram或ttram。此外,非易失性存储器芯片可以包括例如闪存、mram、stt-mram、fram、pram、rram、纳米管rram、聚合物ram、绝缘体电阻变化存储器等。

146.作为另一示例,第二半导体芯片1320中的每个可以包括堆叠型半导体存储器芯片。堆叠型半导体芯片可以基于hbm或混合存储器立方体(hybrid memory cube,hmc)标准来实现。

147.第一半导体芯片1310可以通过利用第二半导体芯片1320来执行由半导体封装件1000支持的应用。例如,第一半导体芯片1310可以通过包括中央处理单元(cpu)、ap、图形处理单元(gpu)、神经处理单元(npu)、张量处理单元(tpu)、视觉处理单元(vpu)、图像信号处理器(isp)和数字信号处理器(dsp)中的至少一者来执行专门的操作。

148.半导体封装件1000可以包括布置在第一半导体芯片1310和第二半导体芯片1320与中介体1200之间的第二绝缘填料1340。第二绝缘填料1340可以覆盖再分布图案1273、连

接凸块1330以及芯片垫1311和1321。

149.半导体封装件1000还可以包括覆盖第一半导体芯片1310和第二半导体芯片1320中的每个的侧表面的第三绝缘填料1350。第三绝缘填料1350可以包括诸如环氧树脂的基体材料层和包含在基体材料层中的填料。

150.冷却片1410可以布置在第一半导体芯片1310和第二半导体芯片1320上。根据示例实施例,冷却片1410可以与第一半导体芯片1310和第二半导体芯片1320中的每个的热点相邻。因为冷却片1410与参照图1描述的冷却片140类似,所以不提供其重复描述。

151.半导体封装件1000还可以包括覆盖第一半导体芯片1310的上表面和第二半导体芯片1320的上表面的散热器件1400。散热器件1400可以包括散热板(诸如散热块或散热器)。根据示例实施例,散热器件1400可以附接到封装基底1100的上表面,并且可以围绕中介体1200的侧表面以及第一半导体芯片1310的侧表面和第二半导体芯片1320的侧表面。

152.现有的半导体封装件可以布置在第一半导体芯片1310和第二半导体芯片1320与散热器件1400之间,并且可以包括具有范围从约3w/(m

·

k)至约4w/(m

·

k)的热导率的热界面材料(tim)层。因此,散热器件1400对第一半导体芯片1310和第二半导体芯片1320的冷却会是不充分的。根据示例实施例,由于具有高热导率的冷却片1410设置在第一半导体芯片1310和第二半导体芯片1320与散热器件1400之间,因此可以改善半导体封装件1000的冷却效率。

153.虽然已经参考发明构思的实施例具体示出并描述了发明构思,但是将理解的是,在不脱离所附权利要求的精神和范围的情况下,可以对其进行形式和细节上的各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1