一种RC-IGBT器件及其制备方法与流程

一种rc-igbt器件及其制备方法

技术领域

1.本技术属于功率器件技术领域,尤其涉及一种rc-igbt器件及其制备方法。

背景技术:

2.绝缘栅双极型晶体管 (insulated gate bipolar transistor,igbt)是由双极型三极管 (bjt)和绝缘栅型场效应管 (mos)组成的复合全控型电压驱动式功率半导体器件,兼有mosfet的高输入阻抗和gtr的低导通压降两方面的优点。rc-igbt器件是通过将igbt和二极管(diode)集成在一起,其主要的优点就是缩减了芯片的尺寸,减少了二极管芯片的面积,使得rc-igbt和igbt的面积类似。

3.然而,常规rc-igbt受限于集成二极管时会面临反向恢复电流较大的问题。

技术实现要素:

4.本技术的目的在于提供一种rc-igbt器件及其制备方法,旨在解决常规rc-igbt受限于集成二极管时会面临反向恢复电流较大的问题。

5.本技术实施例第一方面提供了一种rc-igbt器件的制备方法,所述制备方法包括:在n型衬底层的正面设置第一沟槽和第二沟槽;在所述第一沟槽内形成第一栅极氧化层和第一多晶硅,在所述第二沟槽内形成第二栅极氧化层和第二多晶硅;在所述第一沟槽和所述第二沟槽之间的n型衬底层上注入p型掺杂离子形成p型阱区;在所述p型阱区上形成多个n型源极区,多个所述n型源极区之间互不接触;在每个所述n型源极区上设置接触孔,并通过所述接触孔在所述p型阱区内注入p型掺杂离子,以形成二极管阳极区;在所述n型衬底层的背面形成缓冲层;在所述缓冲层上形成二极管阴极区以及电荷收集区。

6.在一个实施例中,所述在所述n型衬底层的正面设置第一沟槽和第二沟槽,包括:在光罩的遮盖下对所述n型衬底层的正面进行刻蚀形成互相平行的第一沟槽和第二沟槽。

7.在一个实施例中,所述在所述第一沟槽内形成第一栅极氧化层和第一多晶硅,在所述第二沟槽内形成第二栅极氧化层和第二多晶硅,包括:对所述第一沟槽和所述第二沟槽进行热氧化处理,以在所述第一沟槽内形成第一栅极氧化层,在所述第二沟槽内形成第二栅极氧化层;填充多晶硅材料,以在所述第一沟槽内形成第一多晶硅,在所述第二沟槽内形成第二多晶硅。

8.在一个实施例中,所述在所述p型阱区上形成多个n型源极区,包括:通过在所述p型阱区上的多个区域注入n型掺杂离子,以形成多个依次排列的n型

源极区;其中,多个所述n型源极区与所述第一沟槽垂直。

9.在一个实施例中,所述在每个所述n型源极区上设置接触孔,包括:通过光罩在多个所述n型源极区上形成多个短条状的接触孔;其中,所述接触孔的深度大于所述n型源极区的厚度。

10.本技术实施例第二方面还提供了一种rc-igbt器件,所述rc-igbt器件包括:n型衬底层,所述n型衬底层的正面内还设有第一沟槽和第二沟槽;第一栅极氧化层和第二栅极氧化层,其中,所述第一栅极氧化层设于所述第一沟槽的内壁,所述第二栅极氧化层设于所述第二沟槽的内壁;第一多晶硅和第二多晶硅,其中,所述第一多晶硅设于所述第一栅极氧化层内,所述第二多晶硅设于所述第二栅极氧化层内;p型阱区,设于所述第一沟槽和所述第二沟槽之间,且位于所述n型衬底层上;多个n型源极区,设于所述p型阱区上,多个所述n型源极区之间互不接触;多个二极管阳极区,分别设于多个所述n型源极区下,且位于所述p型阱区内;缓冲层,设于所述n型衬底层的背面;二极管阴极区和电荷收集区,设于所述缓冲层上。

11.在一个实施例中,所述第一沟槽和所述第二沟槽互相平行。

12.在一个实施例中,多个所述n型源极区依序排列,且多个所述n型源极区与所述第一沟槽垂直。

13.在一个实施例中,所述二极管阳极区的长度大于所述n型源极区的宽度。

14.在一个实施例中,所述二极管阳极区的宽度小于所述n型源极区的长度。

15.本技术提供的一种rc-igbt器件及其制备方法,其中,在n型衬底层的正面设置第一沟槽和第二沟槽,分别用于形成第一多晶硅和第二多晶硅;在第一沟槽和第二沟槽之间的n型衬底层上注入p型掺杂离子形成p型阱区,在p型阱区上形成多个互不接触的n型源极区,通过在多个n型源极区的位置形成多个短条状的接触孔,从而通过接触孔在p型阱区内注入p型掺杂离子,以形成二极管阳极区,达到减小二极管的有效面积的目的,从而减小二极管的反向恢复电流,解决了常规rc-igbt受限于集成二极管时会面临反向恢复电流较大的问题。

附图说明

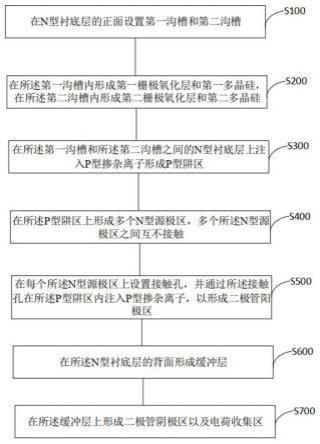

16.图1是本技术实施例提供的rc-igbt器件的制备方法的流程示例图。

17.图2是本技术实施例提供的在n型衬底层上制备沟槽的示例图。

18.图3是本技术实施例提供的在沟槽内形成栅极氧化层以及多晶硅的示例图。

19.图4是本技术实施例提供的形成p型阱区的示例图。

20.图5是本技术实施例提供的形成源极区的示例图。

21.图6是本技术实施例提供的形成接触孔以及二极管阳极区的水平截面示例图。

22.图7是本技术实施例提供的形成接触孔以及二极管阳极区的垂直截面示例图。

23.图8是本技术实施例提供的形成二极管阴极区以及电荷收集区的示例图。

具体实施方式

24.为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

25.需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。

26.需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

27.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

28.本技术实施例提供了一种rc-igbt器件的制备方法,参见图1所示,本实施例中的制备方法包括步骤s100至步骤s700。

29.在步骤s100中,在n型衬底层的正面设置第一沟槽和第二沟槽。

30.在本实施例中,结合图2所示,在n型衬底层100的正面设置第一沟槽101和第二沟槽102,第一沟槽101和第二沟槽102作为器件的栅极沟槽用于后续工艺中填充多晶硅,以形成器件的栅极。

31.在一个具体应用实施例中,步骤s100中,在所述n型衬底层的正面设置第一沟槽和第二沟槽,具体包括:在光罩的遮盖下对所述n型衬底层的正面进行刻蚀形成互相平行的第一沟槽和第二沟槽。

32.在本实施例中,可以通过光罩定义出栅极沟槽的位置,然后在光罩的保护下对n型衬底层100的正面进行刻蚀,以形成第一沟槽101和第二沟槽102。

33.在一些实施例中,第一沟槽101和第二沟槽102可以平行设置。

34.在一些实施例中,第一沟槽101和第二沟槽102的宽度和深度可以相等。

35.在一些实施例中,第一沟槽101和第二沟槽102之间的距离至少大于第一沟槽101和第二沟槽102的宽度。

36.在步骤s200中,在所述第一沟槽内形成第一栅极氧化层和第一多晶硅,在所述第二沟槽内形成第二栅极氧化层和第二多晶硅。

37.在本实施例中,结合图3所示,第一沟槽101内形成有第一栅极氧化层211以及第一多晶硅212,第一栅极氧化层211设于第一多晶硅212与n型衬底层100之间,第二沟槽102内形成有第二栅极氧化层221和第二多晶硅222,第二栅极氧化层221设于第二多晶硅222与n型衬底层100之间。

38.在一个实施例中,步骤s200中可以包括步骤s200-1以及步骤s200-2。

39.在步骤s200-1中,对所述第一沟槽和所述第二沟槽进行热氧化处理,以在所述第一沟槽内形成第一栅极氧化层,在所述第二沟槽内形成第二栅极氧化层。

40.在本实施例中,可以将步骤s100中形成的器件置入氧气环境中进行热氧化处理,从而在器件表面形成氧化硅作为栅极氧化层,具体的,第一沟槽101的内壁形成有第一栅极氧化层211,第二沟槽102的内壁形成有第二栅极氧化层221。

41.在具体应用中,栅极氧化层的厚度和热氧化处理的时间成正比例关系,可以通过控制热氧化工艺的时间控制栅极氧化层的厚度。

42.在步骤s200-2中,填充多晶硅材料,以在所述第一沟槽内形成第一多晶硅,在所述第二沟槽内形成第二多晶硅。

43.在本实施例中,通过在栅极沟槽(第一沟槽101、第二沟槽102)内填充多晶硅材料,从而在第一沟槽101内形成第一多晶硅212,并由第一栅极氧化层211包裹第一多晶硅212,在第二沟槽102内形成第二多晶硅222,并由第二栅极氧化层221包裹第二多晶硅222。

44.在一个具体应用实施例中,可以通过在n型衬底层100的正面淀积多晶硅材料的方式形成多晶硅层,此时第一沟槽101内形成第一多晶硅212,第二沟槽102内形成第二多晶硅222,然后通过化学机械抛光工艺去掉第一沟槽101和第二沟槽102之间多余的多晶硅材料,此时第一多晶硅212和第二多晶硅222的上表面齐平。

45.在步骤s300中,在所述第一沟槽和所述第二沟槽之间的n型衬底层上注入p型掺杂离子形成p型阱区。

46.在本实施例中,结合图4所示,通过向第一沟槽101和第二沟槽102之间的衬底区域注入p型掺杂离子,从而在n型衬底层100中形成p型阱区300。

47.在一些实施例中,p型阱区300的厚度小于第一多晶硅212和第二多晶硅222的深度。

48.在一些实施例中,p型阱区300中的p型掺杂离子的浓度大于n型衬底层100中的n型掺杂离子的浓度。

49.在步骤s400中,在所述p型阱区上形成多个n型源极区,多个所述n型源极区之间互不接触。

50.在本实施例中,结合图5所示,通过在p型阱区300上的指定区域注入n型掺杂离子,从而在p型阱区300上形成多个n型源极区400,且多个n型源极区400之间互不接触。

51.在一个实施例中,步骤s400中,在所述p型阱区上形成多个n型源极区,包括:通过在所述p型阱区上的多个区域注入n型掺杂离子,以形成多个依次排列的n型源极区。

52.在本实施例中,可以通过光罩定义出n型源极区400的位置,然后在光罩的遮盖下向p型阱区300注入n型掺杂离子形成多个n型源极区400,多个n型源极区400与第一沟槽101垂直。

53.在具体应用实施例中,n型源极区400中n型掺杂离子的浓度大于n型衬底层100的浓度。

54.在步骤s500中,在每个所述n型源极区上设置接触孔,并通过所述接触孔在所述p型阱区内注入p型掺杂离子,以形成二极管阳极区。

55.在本实施例中,结合图6所示,多个接触孔501形成的连线与n型源极区400垂直,此时,横截面a处的结构示意图参见图4所示,横截面b的结构示意图参见图7所示。

56.结合图6和图7所示,每个接触孔401深入至p型阱区300中,且接触孔401的长度大于n型源极区400的宽度,从而将n型源极区400划分为第一n型源极区410和第二n型源极区

420。

57.在一个实施例中,步骤s500中,在每个所述n型源极区上设置接触孔,包括:通过光罩在多个所述n型源极区上形成多个短条状的接触孔;其中,所述接触孔的深度大于所述n型源极区的厚度。

58.在本实施例中,参见图7所示,接触孔501的深度大于n型源极区400的厚度,通过接触孔401将p型掺杂离子注入至p型阱区300中,以在p型阱区300内形成二极管阳极区610。

59.在具体应用实施例中,二极管阳极区610中的p型掺杂离子的浓度大于p型阱区300内p型掺杂离子的浓度。

60.在一个实施例中,参见图6和图7所示,多个n型源极区400依序排列,且多个n型源极区400与第一沟槽101垂直。

61.在一个实施例中,二极管阳极区610的长度大于n型源极区400的宽度,具体的,二极管阳极区610的长度方向与第一沟槽101平行。

62.在一个实施例中,二极管阳极区610的宽度小于n型源极区400的长度,具体的,二极管阳极区610的宽度方向与n型源极区400平行。

63.在一个实施例中,二极管阳极区610的宽度大于接触孔501的宽度。

64.在具体应用中,可以通过调整p型掺杂离子的注入方向,调整二极管阳极区610的宽度。

65.在本实施例中,通过在多个所述n型源极区上形成多个短条状的接触孔,从而在多个n型源极区所对应的p型阱区300中的区域形成二极管阳极区610,可以减少二极管阳极区的离子注入面积,缩小二极管的有效面积,从而通过减少空穴注入数量方式减小反向恢复电流。

66.在一个实施例中,多个短条状的接触孔的长度可以不同,其长度可以以n型衬底层100的中央位置为最大,然后往边缘位置逐渐减小的方式排列。

67.在一个实施例中,本实施例中的制备方法还包括在多晶硅层(第一多晶硅212、第二多晶硅222)以及n型源极区400上形成正面金属层以及钝化层601。

68.在步骤s600中,在所述n型衬底层100的背面形成缓冲层110。

69.在本实施例中,参见图8所示,n型衬底层100的背面形成缓冲层110,缓冲层110中掺杂有n型掺杂离子,其掺杂浓度大于n型衬底层100中的掺杂浓度。

70.在具体应用中,可以通过向n型衬底层100的背面注入n型掺杂离子方式在n型衬底层100的背面形成缓冲层110。

71.在步骤s700中,在所述缓冲层上形成二极管阴极区以及电荷收集区。

72.在本实施例中,参见图8所示,缓冲层110上形成二极管阴极区(第一阴极区621和第二阴极区622)以及电荷收集区630。

73.在本实施例中,电荷收集区630设于第一阴极区621和第二阴极区622之间。

74.在具体应用中,第一阴极区621和第二阴极区622中掺杂有n型掺杂离子,其掺杂浓度大于缓冲层110中的n型掺杂离子的浓度。

75.在具体应用中,电荷收集区630中掺杂有p型掺杂离子。

76.在一个实施例中,本实施例中的制备方法还包括在二极管阴极区以及电荷收集区630上设置背面金属层,此时,二极管阴极区以及电荷收集区630设于背面金属层与n型金属

层100之间。

77.本技术实施例还提供了一种rc-igbt器件,参见图8所示,rc-igbt器件包括:n型衬底层100、第一栅极氧化层211、第二栅极氧化层221、第一多晶硅212、第二多晶硅222、p型阱区300、多个n型源极区(第一n型源极区410和第二n型源极区420)、多个二极管阳极区610、缓冲层110、二极管阴极区(第一阴极区621和第二阴极区622)以及电荷收集区630。

78.在本实施例中, n型衬底层100的正面内还设有第一沟槽和第二沟槽,第一栅极氧化层211设于第一沟槽的内壁,第二栅极氧化层221设于第二沟槽的内壁;第一多晶硅212设于第一栅极氧化层211内,第二多晶硅222设于所述第二栅极氧化层221内;p型阱区300设于第一沟槽和第二沟槽之间,且位于n型衬底层100上。

79.在本实施例中,多个n型源极区设于p型阱区300上形成,多个n型源极区之间互不接触;且每个n型源极区由对应的接触孔501划分为第一n型源极区410和第二n型源极区420。多个二极管阳极区610分别设于多个n型源极区下,且位于p型阱区300内;缓冲层110设于n型衬底层100的背面;二极管阴极区和电荷收集区630设于缓冲层110上。

80.在本实施例中,通过在多个n型源极区所对应的p型阱区300中的区域形成二极管阳极区610可以减少二极管阳极区的离子注入面积,缩小二极管的有效面积,从而通过减少空穴注入数量方式减小反向恢复电流。

81.在一个实施例中,rc-igbt器件还包括设于接触孔501内的正面金属层,以及设于多晶硅层(第一多晶硅212、第二多晶硅222)以及n型源极区400上钝化层601。

82.在一个实施例中,钝化层601可以为氧化硅或者氮化硅。

83.在一个实施例中,第一沟槽101和第二沟槽102可以平行设置。

84.在一个实施例中,多个n型源极区400依序排列,且多个n型源极区400与第一沟槽101垂直。

85.在一些实施例中,第一多晶硅212、第二多晶硅222的宽度和深度可以相等。

86.在一些实施例中,第一多晶硅212、第二多晶硅222之间的距离至少大于第一多晶硅212、第二多晶硅222的宽度。

87.在一些实施例中,p型阱区300的厚度小于第一多晶硅212和第二多晶硅222的深度。

88.在一些实施例中,p型阱区300中的p型掺杂离子的浓度大于n型衬底层100中的n型掺杂离子的浓度。

89.在一个实施例中,二极管阳极区610的长度大于n型源极区400的宽度。

90.在一个实施例中,二极管阳极区610的宽度小于n型源极区400的长度。

91.在一些实施例中,缓冲层110设于n型衬底层100的背面,缓冲层110中掺杂有n型掺杂离子,其掺杂浓度大于n型衬底层100中的掺杂浓度。

92.在本实施例中,电荷收集区630设于第一阴极区621和第二阴极区622之间。

93.在一些实施例中,第一阴极区621和第二阴极区622中掺杂有n型掺杂离子,其掺杂浓度大于缓冲层110中的n型掺杂离子的浓度。

94.在一些实施例中,电荷收集区630中掺杂有p型掺杂离子。

95.在一些实施例中,rc-igbt器件还包括设于二极管阴极区以及电荷收集区630上的背面金属层,二极管阴极区以及电荷收集区630设于背面金属层与n型金属层100之间。

96.本技术实施例还提供了一种rc-igbt器件,所述rc-igbt器件由上述任一项实施例所述的rc-igbt器件的制备方法所制备。

97.本技术提供的一种rc-igbt器件及其制备方法,其中,在n型衬底层的正面设置第一沟槽和第二沟槽,分别用于形成第一多晶硅和第二多晶硅;在第一沟槽和第二沟槽之间的n型衬底层上注入p型掺杂离子形成p型阱区,在p型阱区上形成多个互不接触的n型源极区,通过在多个n型源极区的位置形成多个短条状的接触孔,从而通过接触孔在p型阱区内注入p型掺杂离子,以形成二极管阳极区,达到减小二极管的有效面积的目的,从而减小二极管的反向恢复电流,解决了常规rc-igbt受限于集成二极管时会面临反向恢复电流较大的问题。

98.所属领域的技术人员可以清楚地了解到,为了描述的方便和简洁,仅以上述各掺杂区区的划分进行举例说明,实际应用中,可以根据需要而将上述功能区分配由不同的掺杂区完成,即将所述装置的内部结构划分成不同的掺杂区,以完成以上描述的全部或者部分功能。

99.实施例中的各掺杂区可以集成在一个功能区中,也可以是各个掺杂区单独物理存在,也可以两个或两个以上掺杂区集成在一个功能区中,上述集成的功能区既可以采用同种掺杂离子实现,也可以采用多种掺杂离子共同实现。另外,各掺杂区的具体名称也只是为了便于相互区分,并不用于限制本技术的保护范围。上述器件的制备方法中的中掺杂区的具体工作过程,可以参考前述方法实施例中的对应过程,在此不再赘述。

100.以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1