可寻址VCSEL芯片及其制备方法和激光雷达与流程

本技术涉及半导体激光器领域,更为具体地涉及可寻址vcsel芯片及其制备方法。

背景技术:

1、vcsel(vertical-cavity surface-emitting laser,垂直腔面发射激光器)是指在衬底的垂直方向上形成谐振腔,沿垂直方向出射激光的一种半导体激光器。近年来,vcsel技术在半固态激光雷达和纯固态激光雷达中得到了广泛应用。

2、具体地,纯固态激光雷达是指在不借助任何旋转部件的前提下实现激光扫描的固态激光雷达。相比于机械式激光雷达,由于不需要借助旋转部件进行旋转,可避免旋转部件在运行过程中的稳定性(例如,结构稳定性、旋转精度稳定性)和可靠性对扫描结果准确性的影响,也可简化生产工艺,降低生产成本。

3、在纯固态激光雷达的应用中,可利用vcsel寻址技术实现激光扫描。具体地,通过寻址技术实现vcsel芯片的分区点亮,并通过控制点亮区域和点亮顺序控制激光的投射范围和投射方向,使得vcsel芯片不同区域出射的激光被按照特定顺序逐步投射至被测目标区域的各个部分,以实现激光扫描。

4、目前,vcsel寻址技术可被划分为一维寻址技术和二维寻址技术。一维可寻址vcsel虽然可以实现区块信息的单独捕捉和分析,但受限于vcsel芯片的结构设计,分区捕捉的效果不佳,难以对vcsel芯片进行细微的分区捕捉,无法实现大范围的精准寻址。相比于一维可寻址vcsel芯片,二维可寻址vcsel芯片提升了细微分区捕捉能力,可到达大范围的精准寻址。然而,现有的二维可寻址vcsel芯片布线结构复杂、生产工艺也相对复杂,生产成本较高,阻碍了其在实际产业中的应用。

5、因此,需要一种优化的vcsel寻址方案,以满足实际产业对vcsel寻址的要求。

技术实现思路

1、本技术的一个优势在于提供了一种可寻址vcsel芯片及其制备方法,其中,所述可寻址vcsel芯片通过对其电极结构进行异构,在实现二维寻址的同时简化了布线结构。

2、本技术的另一个优势在于提供了一种可寻址vcsel芯片及其制备方法,其中,所述可寻址vcsel芯片能够在保证对每个vcsel发光点独立的电导通控制的条件下减少电连接于所述vcsel发光点的电连接线的数量,以简化布线结构。

3、本技术的又一个优势在于提供了一种可寻址vcsel芯片及其制备方法,其中,所述可寻址vcsel芯片的异构电极结构在晶圆级别上形成于芯片主体的上表面和/或下表面,便于后续工序中对vcsel芯片进行封装和光学元件集成。

4、本技术的又一个优势在于提供了一种可寻址vcsel芯片及其制备方法,其中,由于所述可寻址vcsel芯片的布线结构被简化,所述可寻址vcsel芯片的制备工艺也随之被简化,制备难度也随之降低。

5、本技术的又一个优势在于提供了一种可寻址vcsel芯片及其制备方法,其中,所述可寻址vcsel芯片在制备过程中仍能够沿用传统的vcsel芯片的制备工艺,仅需要配合特定的掩膜即可实现结构上的异构,这样,可保留原有的vcsel芯片生产线和生产设备以将其用于制备本技术的可寻址vcsel芯片,有效降低vcsel芯片的生产线改造成本,进而降低vcsel芯片的制备成本。

6、为了实现上述至少一优势或其他优势和目的,根据本技术的一个方面,提供了一种可寻址vcsel芯片,其包括:

7、具有相对的上表面和下表面的芯片主体,包括发光区域结构和环绕于所述发光区域结构的外围区域结构,所述发光区域结构包括多个vcsel发光单元,每一所述vcsel发光单元包括至少一vcsel发光点,每一vcsel发光点包括一发光主体和电连接于所述发光主体的正电导通层和负电导通层;和

8、寻址电路结构,包括多条正电连接线和多条负电连接线,其中,每一所述正电连接线形成于所述芯片主体的上表面或下表面且电连接于至少二所述vcsel发光单元的正电导通层,每一所述负电连接线形成于所述芯片主体的上表面或下表面且电连接于至少二所述vcsel发光单元的负电导通层,通过这样的方式,所述寻址电路结构形成所述多个vcsel发光单元的寻址电路以使得所述多个vcsel发光单元中任一所述vcsel发光单元适于通过导通一对所述正电连接线和所述负电连接线实现电导通。

9、在本技术的可寻址vcsel芯片中,每一所述vcsel发光点自下而上包括:衬底层、负电导通层、n-dbr层、有源区、具有限制孔的限制层、p-dbr层和正电导通层,所述正电导通层的上表面形成所述芯片主体的上表面的一部分。

10、在本技术的可寻址vcsel芯片中,每一正电连接线形成于所述芯片主体的上表面,每一所述负电连接线从所述负电导通层被引至所述芯片主体的上表面。

11、在本技术的可寻址vcsel芯片中,所述芯片主体具有从所述芯片主体的上表面凹陷地延伸至所述负电导通层的至少一槽体,使得所述负电导通层的至少一部分被暴露并形成所述槽体的底部,所述负电连接线被埋于所述槽体的底部并从所述槽体的底部延伸至所述芯片主体的上表面。

12、在本技术的可寻址vcsel芯片中,所述发光区域结构的上表面和所述外围区域结构的上表面形成所述芯片主体的上表面,所述负电连接线被引至所述外围区域结构的上表面。

13、在本技术的可寻址vcsel芯片中,所述外围区域结构的上表面齐平于所述发光区域结构的上表面。

14、在本技术的可寻址vcsel芯片中,每一所述正电连接线形成于所述芯片主体的上表面,每一所述负电连接线从所述负电导通层被引至所述芯片主体的下表面。

15、在本技术的可寻址vcsel芯片中,所述芯片主体具有从所述负电导通层延伸至所述芯片主体的下表面的孔结构,使得所述负电导通层的至少一部分被暴露,所述负电连接线从所述负电导通层的被暴露部分延伸至所述芯片主体的下表面。

16、在本技术的可寻址vcsel芯片中,每一所述正电连接线形成于所述芯片主体的上表面,每一所述负电连接线包括第一负电连接结构和第二负电连接结构,所述第一负电连接结构从所述负电导通层被引至所述芯片主体的下表面,所述第二负电连接结构从所述负电导通层被引至所述芯片主体的上表面。

17、在本技术的可寻址vcsel芯片中,所述芯片主体具有从所述负电导通层延伸至所述芯片主体的下表面的孔结构和从所述芯片主体的上表面凹陷地延伸至所述负电导通层的至少一槽体,所述第一负电连接结构从所述负电导通层通过所述孔结构延伸至所述芯片主体的下表面,所述第二负电连接结构从所述负电导通层通过所述槽体延伸至所述芯片主体的上表面。

18、在本技术的可寻址vcsel芯片中,每一所述vcsel发光点自下而上包括:衬底层、正电导通层、p-dbr层、有源区、具有限制孔的限制层、n-dbr层和负电导通层,所述负电导通层的上表面形成所述芯片主体的上表面的一部分。

19、在本技术的可寻址vcsel芯片中,每一所述负电连接线形成于所述芯片主体的上表面,每一所述正电连接线被引至所述芯片主体的上表面。

20、在本技术的可寻址vcsel芯片中,所述芯片主体具有从所述芯片主体的上表面凹陷地延伸至所述正电导通层的至少一槽体,使得所述正电导通层的至少一部分被暴露并形成所述槽体的底部,所述正电连接线被埋于所述槽体的底部并从所述槽体的底部延伸至所述芯片主体的上表面。

21、在本技术的可寻址vcsel芯片中,每一所述负电连接线形成于所述芯片主体的上表面,每一所述正电连接线从所述正电导通层被引至所述芯片主体的下表面。

22、在本技术的可寻址vcsel芯片中,所述芯片主体具有从所述芯片主体的下表面延伸至所述正电导通层的孔结构,使得所述正电导通层的至少一部分被暴露,所述正电连接线从所述正电导通层的被暴露部分延伸至所述芯片主体的下表面。

23、在本技术的可寻址vcsel芯片中,每一所述负电连接线形成于所述芯片主体的上表面,每一所述正电连接线包括第一正电连接结构和第二正电连接结构,所述第一正电连接结构从所述正电导通层被引至所述芯片主体的下表面,所述第二正电连接结构从所述正电导通层被引至所述芯片主体的上表面。

24、在本技术的可寻址vcsel芯片中,所述芯片主体具有从所述芯片主体的下表面延伸至所述正电导通层的孔结构和从所述芯片主体的上表面凹陷地延伸至所述正电导通层的至少一槽体,所述正电连接线通过所述孔结构延伸至所述芯片主体的下表面,所述第二正电连接结构通过所述槽体延伸至所述芯片主体的上表面。

25、在本技术的可寻址vcsel芯片中,每一所述正电连接线覆盖于至少二所述vcsel发光单元,所述正电连接线具有对应于所述多个vcsel发光单元中至少一vcsel发光点的限制孔的一个通光孔。

26、在本技术的可寻址vcsel芯片中,每一所述正电连接线电连接于沿所述芯片主体所设定的第一方向布置的一行所述vcsel发光单元的所述正电导通层,每一所述负电连接线电连接于沿所述芯片主体所设定的第二方向布置的一列所述vcsel发光单元的所述负电导通层,其中,所述第一方向和所述第二方向存在夹角。

27、在本技术的可寻址vcsel芯片中,每一条所述负电连接线电连接的一列所述vcsel发光单元的负电导通层一体地连接,以形成共用负电导通层。

28、根据本技术的另一个方面,提供了一种vcsel芯片的制备方法,其包括:

29、形成外延主体结构,所述外延主体结构自下而上包括衬底结构层、n型欧姆接触结构层、n-dbr结构层、有源区结构层和p-dbr结构层;

30、去除所述外延主体结构的至少一部分以形成多个凹槽和多个子单元结构,每一子单元结构包括衬底层、负电导通层、n-dbr层、有源区和p-dbr层;

31、分别在所述多个子单元结构上形成多个正电导通层;

32、对所述多个子单元结构进行处理以在所述有源区的上方形成具有限制孔的限制层,以形成多个vcsel发光单元,每一vcsel发光单元包括至少一vcsel发光点,每一vcsel发光点自下而上包括:所述衬底层、所述负电导通层、所述n-dbr层、所述有源区、具有限制孔的限制层、所述p-dbr层和所述正电导通层;以及

33、形成电连接于所述多个vcsel发光单元的正电连接线和负电连接线,以形成电连接于所述多个vcsel发光单元的寻址电路结构。

34、在本技术的vcsel芯片的制备方法中,去除所述外延主体结构的至少一部分以形成多个凹槽和多个子单元结构,包括:形成深度为第一深度的第一凹槽、深度为第二深度的第二凹槽和深度为第三深度的第三凹槽,其中,所述第一凹槽从所述p-dbr结构层延伸至所述有源区结构层的下方,所述第二凹槽从所述p-dbr结构层延伸至所述n型欧姆接触结构层,所述第三凹槽从所述p-dbr结构层延伸至所述衬底结构层。

35、在本技术的vcsel芯片的制备方法中,所述第二凹槽将所述外延主体结构分隔为第一区域结构和环绕于所述第一区域结构的第二区域结构,形成所述多个正电导通层和多个限制层后的所述第一区域结构形成所述多个vcsel发光单元,进而形成发光区域,所述第二区域结构形成环绕于所述发光区域结构的外围区域结构,所述第二凹槽形成所述发光区域和所述外围区域结构之间的槽体,所述槽体从所述p-dbr层延伸至所述负电导通层,使得所述负电导通层的至少一部分被暴露并形成所述槽体的底部,所述负电连接线被埋于所述槽体的底部;其中,形成电连接于所述多个vcsel发光单元的正电连接线和负电连接线,包括:形成从所述槽体的底部延伸至所述外围区域结构的上表面。

36、在本技术的vcsel芯片的制备方法中,形成电连接于所述多个vcsel发光单元的正电连接线和负电连接线,包括:形成从所述负电导通层延伸至所述衬底层的下表面的孔结构,使得所述负电导通层的至少一部分被暴露;以及,形成从所述负电导通层的被暴露部分延伸至所述衬底层的下表面的负电连接线。

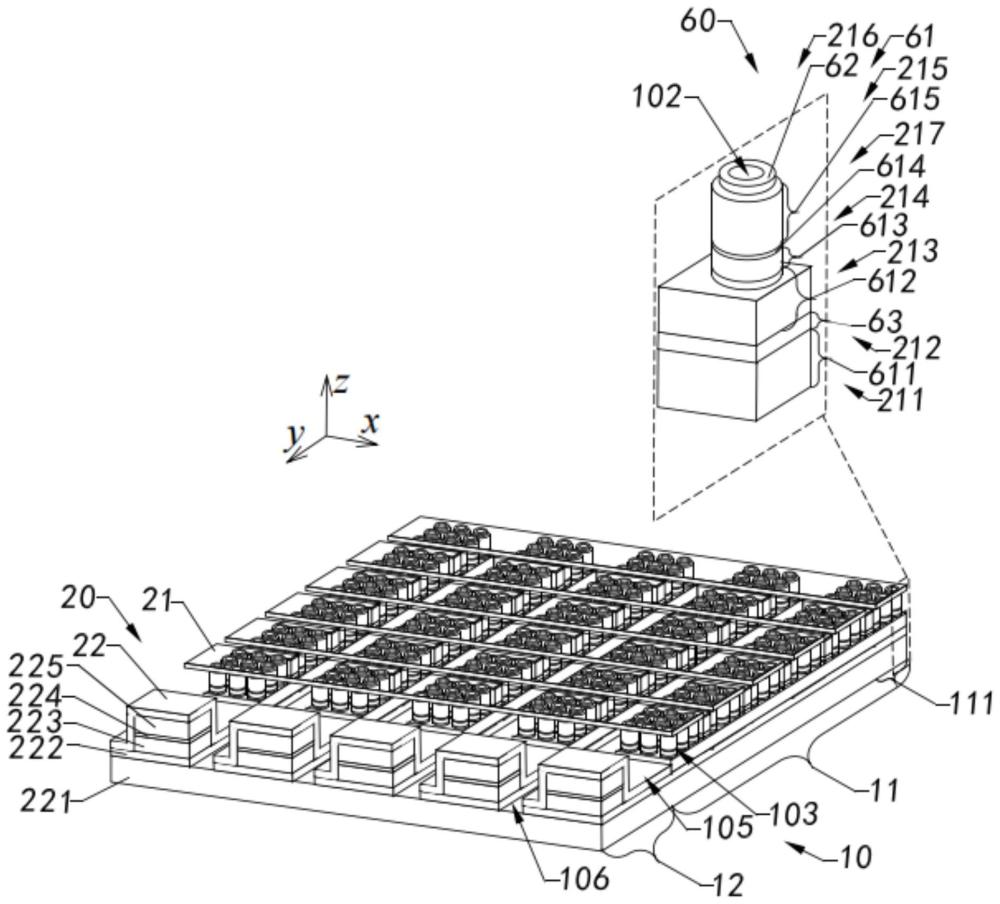

37、根据本技术的又一个方面,本技术提出了一种激光雷达,其包括:

38、用于投射激光的激光投射装置,其中,所述激光投射装置包括如上所述的任一可寻址vcsel芯片;

39、用于接收激光信号的激光接收装置;以及

40、可通信地连接于所述激光投射装置和所述激光接收装置的处理器。

41、通过对随后的描述和附图的理解,本技术进一步的目的和优势将得以充分体现。

42、本技术的这些和其它目的、特点和优势,通过下述的详细说明,附图和权利要求得以充分体现。

- 还没有人留言评论。精彩留言会获得点赞!