一种内绝缘结构的IGBT结构及其工艺的制作方法

一种内绝缘结构的igbt结构及其工艺

技术领域

1.本发明涉及igbt技术领域,具体涉及一种内绝缘结构的igbt结构。

背景技术:

2.目前,我国新型电力电子器件主要有vdmos及igbt类器件,igbt具有mos输入、双极输出功能,载流密度大、耐压高和功率mosfet驱动功率小、开关速度快、输入阻抗高、热稳定性好的优点于一身。自问世以来,很快发展成为中高功率电力电子领域的主流功率开关器件,由于igbt内存在寄生三极管,在igbt导通时,寄生三极管具有一定的导通的几率,在寄生三极管导通后会极大增加了igbt的漏电流从而对igbt造成损坏。

技术实现要素:

3.本发明实施例提供了一种内绝缘结构的igbt结构,通过在n+型飘移层设置两性掺杂区减少寄生三极管的数量,同时设置的第一掺杂区和第二掺杂区,在减少寄生三极管数量的同时还降低寄生三极管的基区电阻进一步抑制寄生三极管效应,达到避免igbt的内部出现漏电流避免对igbt造成损坏的效果。

4.鉴于上述问题,本发明提出的技术方案是:

5.一种内绝缘结构的igbt结构,包括集电极,所述集电极的上方设置有p型缓冲层,所述p型缓冲层的上方设置有n型缓冲层,所述n型缓冲层的上方设置有n+型飘移层,所述n+型飘移层的内部设置有p型块,所述n+型飘移层的顶部设置有蚀刻沟槽,所述蚀刻沟槽的内部设置有两性掺杂区域,所述两性掺杂区域的内部下方设置有第一掺杂区,所述n型缓冲层、所述n+型飘移层和所述第一掺杂区上分别设置有第二掺杂区,所述两性掺杂区域的内部上方依次设置有n型块和p型块,所述两性掺杂区域的顶部一侧设置有发射极,所述n+型飘移的顶部和所述两性掺杂区域的顶部另一侧设置有氧化层,所述氧化层的顶部设置有栅极。

6.作为本发明的一种优选技术方案,所述两性掺杂区域设置于所述n+型飘移的内部两侧。

7.作为本发明的一种优选技术方案,其特征在于:所述第一掺杂区为n型掺杂区,所述第二掺杂区为p型掺杂区。

8.作为本发明的一种优选技术方案,其特征在于:所述第一掺杂区环绕所述第二掺杂区设置。

9.本发明实施例还提供了一种内绝缘结构的igbt结构的工艺,包括以下步骤:

10.s1,在半导体衬底表面通过化学气相淀积法生长p型缓冲层;在p型缓冲层的表面通过化学气相淀积法生长n型缓冲层;在n型缓冲层的表面通过化学气相淀积法生长n+型飘移层;

11.s2,通过离子刻蚀工艺在n+型飘移层的顶部蚀刻出第一沟槽;

12.s3,在第一沟槽的内部通过化学气相淀积法生长两性掺杂区后采用离子刻蚀工艺

在两性掺杂区蚀刻出第二沟槽,在第二沟槽的内部通过化学气相淀积法生长第一掺杂区;

13.s4,采用离子刻蚀工艺在第一掺杂区、n+型飘移层和n型缓冲层上蚀刻出第三沟槽,在第三沟槽的内部通过化学气相淀积法生长第二掺杂区;

14.s5,通过化学气相淀积法在第一掺杂区和第二掺杂区上方继续生长两性掺杂区使两性掺杂区的表面与n+型飘移层的表面齐平,采用离子刻蚀工艺在两性掺杂区的表面蚀刻出第四沟槽,在第四沟槽的内部通过化学气相淀积法生长p型块,在p型块的表面通过化学气相淀积法生长n型块,采用离子刻蚀工艺在n型块表面一侧进行蚀刻得到第四沟槽,在第四沟槽的内部采用化学气相淀积法生长两性掺杂区至与n型缓冲层表面齐平;

15.s6,采用化学机械抛光工艺,去除半导体衬底并在1100℃温度下,氮气气氛中退火12分钟;

16.s7,去除半导体衬底的背面设置金属材料层形成集电极;在结构完成部分的顶部分别设置金属层和氧化层并在氧化层设置金属层分别形成发射级和栅极。

17.相对于现有技术而言,本发明的有益效果是:通过在n+型飘移层设置两性掺杂区减少寄生三极管的数量,同时设置的第一掺杂区和第二掺杂区,在减少寄生三极管数量的同时还降低寄生三极管的基区电阻进一步抑制寄生三极管效应,达到避免igbt的内部出现漏电流避免对igbt造成损坏的效果。

18.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

附图说明

19.图1为本发明实施例公开的步骤s1的结构示意图;

20.图2为本发明实施例公开的步骤s2的结构示意图;

21.图3为本发明实施例公开的步骤s3~s6的结构示意图;

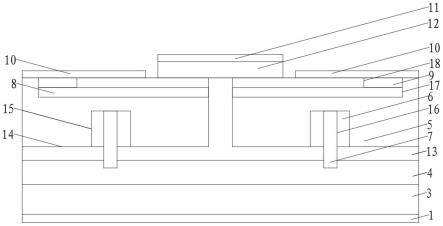

22.图4为本发明实施例公开的步骤s7的结构示意图;

23.图5为本发明实施例公开的内绝缘结构的igbt结构工艺的流程示意图。

24.附图标记:

25.1、集电极;2、半导体衬底;3、p型缓冲层;4、n型缓冲层;5、两性掺杂区;6、第一掺杂区;7、第二掺杂区;8、p型块;9、n型块;10、发射极;11、栅极;12、氧化层;13、n+型飘移层;14、第一沟槽;15、第二沟槽;16、第三沟槽;17、第四沟槽;18、第五沟槽。

具体实施方式

26.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

27.参照附图1-4所示,一种内绝缘结构的igbt结构,其包括集电极1,所述集电极1的上方设置有p型缓冲层3,所述p型缓冲层3的上方设置有n型缓冲层4,所述n型缓冲层4的上方设置有n+型飘移层13,所述n+型飘移层13的内部设置有p型块8,所述n+型飘移层13的顶部设置有蚀刻沟槽,所述蚀刻沟槽的内部设置有两性掺杂区5域,两性掺杂区5域采用n型和p型杂质,用于在n+型飘移层13起到半绝缘的作用,所述两性掺杂区5域设置于所述n+型飘

移的内部两侧,所述两性掺杂区5域的内部下方设置有第一掺杂区6,所述n型缓冲层4、所述n+型飘移层13和所述第一掺杂区6上分别设置有第二掺杂区7,所述第一掺杂区6为n型掺杂区,所述第二掺杂区7为p型掺杂区,且所述第一掺杂区6环绕所述第二掺杂区7设置,所述两性掺杂区5域的内部上方依次设置有n型块9和p型块8,所述两性掺杂区5域的顶部一侧设置有发射极10,所述n+型飘移的顶部和所述两性掺杂区5域的顶部另一侧设置有氧化层12,所述氧化层12的顶部设置有栅极11,通过在n+型飘移层13设置两性掺杂区5,形成半绝缘区域来减少igbt内部寄生三极管的数量,同时在n+型飘移层13的内部设置的第一掺杂区6和第二掺杂区7,使两性掺杂区5形成的半绝缘区域分别与n型缓冲层4和p型缓冲层3连接,在减少寄生三极管数量的同时还降低寄生三极管的基区电阻进一步抑制寄生三极管效应,通过上述设计形成在igbt内部的内绝缘结构,达到避免igbt的内部出现漏电流避免对igbt造成损坏的效果,同时igbt出现击穿电压时,还能起到降低igbt的漏电流避免对igbt造成损坏的效果。

28.参照附图1-5所示,一种内绝缘结构的igbt结构的工艺,其特征在于,包括以下步骤:

29.s1,在半导体衬底2表面通过化学气相淀积法生长p型缓冲层3;在p型缓冲层3的表面通过化学气相淀积法生长n型缓冲层4;在n型缓冲层4的表面通过化学气相淀积法生长n+型飘移层13;

30.s2,通过离子刻蚀工艺在n+型飘移层13的顶部蚀刻出第一沟槽14;

31.s3,在第一沟槽14的内部通过化学气相淀积法生长两性掺杂区5后采用离子刻蚀工艺在两性掺杂区5蚀刻出第二沟槽15,在第二沟槽15的内部通过化学气相淀积法生长第一掺杂区6;

32.s4,采用离子刻蚀工艺在第一掺杂区6、n+型飘移层13和n型缓冲层4上蚀刻出第三沟槽16,在第三沟槽16的内部通过化学气相淀积法生长第二掺杂区7;

33.s5,通过化学气相淀积法在第一掺杂区6和第二掺杂区7上方继续生长两性掺杂区5使两性掺杂区5的表面与n+型飘移层13的表面齐平,采用离子刻蚀工艺在两性掺杂区5的表面蚀刻出第四沟槽17,在第四沟槽17的内部通过化学气相淀积法生长p型块8,在p型块8的表面通过化学气相淀积法生长n型块9,采用离子刻蚀工艺在n型块9表面一侧进行蚀刻得到第四沟槽17,在第四沟槽17的内部采用化学气相淀积法生长两性掺杂区5至与n型缓冲层4表面齐平;

34.s6,采用化学机械抛光工艺,去除半导体衬底2并在1100℃温度下,氮气气氛中退火12分钟;

35.s7,去除半导体衬底2的背面设置金属材料层形成集电极1;在结构完成部分的顶部分别设置金属层和氧化层12并在氧化层12设置金属层分别形成发射级和栅极11。

36.具体的工作原理,通过在n+型飘移层13设置两性掺杂区5,形成半绝缘区域来减少igbt内部寄生三极管的数量,同时在n+型飘移层13的内部设置的第一掺杂区6和第二掺杂区7,使两性掺杂区5形成的半绝缘区域分别与n型缓冲层4和p型缓冲层3连接,在减少寄生三极管数量的同时还降低寄生三极管的基区电阻进一步抑制寄生三极管效应,达到避免igbt的内部出现漏电流避免对igbt造成损坏的效果。

37.显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精

神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1