封装基板的制作方法

本发明涉及一种半导体工艺用的封装基板,尤其涉及一种非对称式封装基板。

背景技术:

1、随着产业应用的发展,近年来逐渐朝向5g高频通信、扩增实境(augmentedreality,简称ar)、虚拟实境(virtual reality,缩写vr)等发展,因此更需要研发高阶半导体的封装技术,以应用于如人工智能(ai)芯片、高阶芯片、多芯片等的半导体倒装芯片封装或多芯片封装,而在此封装需求的下,封装尺寸势必越来越大,叠层数也越来越高,导致线路设计更是朝高密度、细线路间距、高电性连接点数等方向设计,借以满足上揭芯片的封装需求。

2、图1a为现有封装基板1的剖视图。如图1a所示,该封装基板1包括一核心板体10,其具有相对的第一侧10a及第二侧10b,且于该核心板体10的第一侧10a形成有第一线路结构11,而于该核心板体10的第二侧10b形成有第二线路结构12,其中,该核心板体10具有多个连通该第一侧10a与第二侧10b的导电通孔100,以电性连接该第一线路结构11及该第二线路结构12,且该第一线路结构11的布线层数及该第二线路结构12的布线层数相同,使该封装基板1基于布线层数呈对称式,其中,该第一线路结构11与该第二线路结构12的其中一者用于接置半导体芯片,供作置晶侧,而另一者则用于接置电路板,供作安装侧。

3、然而,现有封装基板1中,其置晶侧的接点多,而安装侧的接点少,若将该第一线路结构11的布线层数及该第二线路结构12的布线层数设计成相同时,则安装侧的线路结构不仅不易于配线(layout),且其制作成本明显过多,致使该封装基板1的制作效率不佳,且制作成本难以降低。

4、再者,虽可通过减少安装侧的布线层数,如图1b所示的第二线路结构12,以降低制作成本,但当该第一线路结构11的布线层数及该第二线路结构12的布线层数不相同时,该封装基板1因其第一侧10a与第二侧10b的布线层数不对称而使其上整体线路结构的热膨胀系数(coefficient of thermal expansion,简称cte)不同,导致该封装基板1发生翘曲的问题。

5、因此,如何克服上述现有技术的问题,实已成目前亟欲解决的课题。

技术实现思路

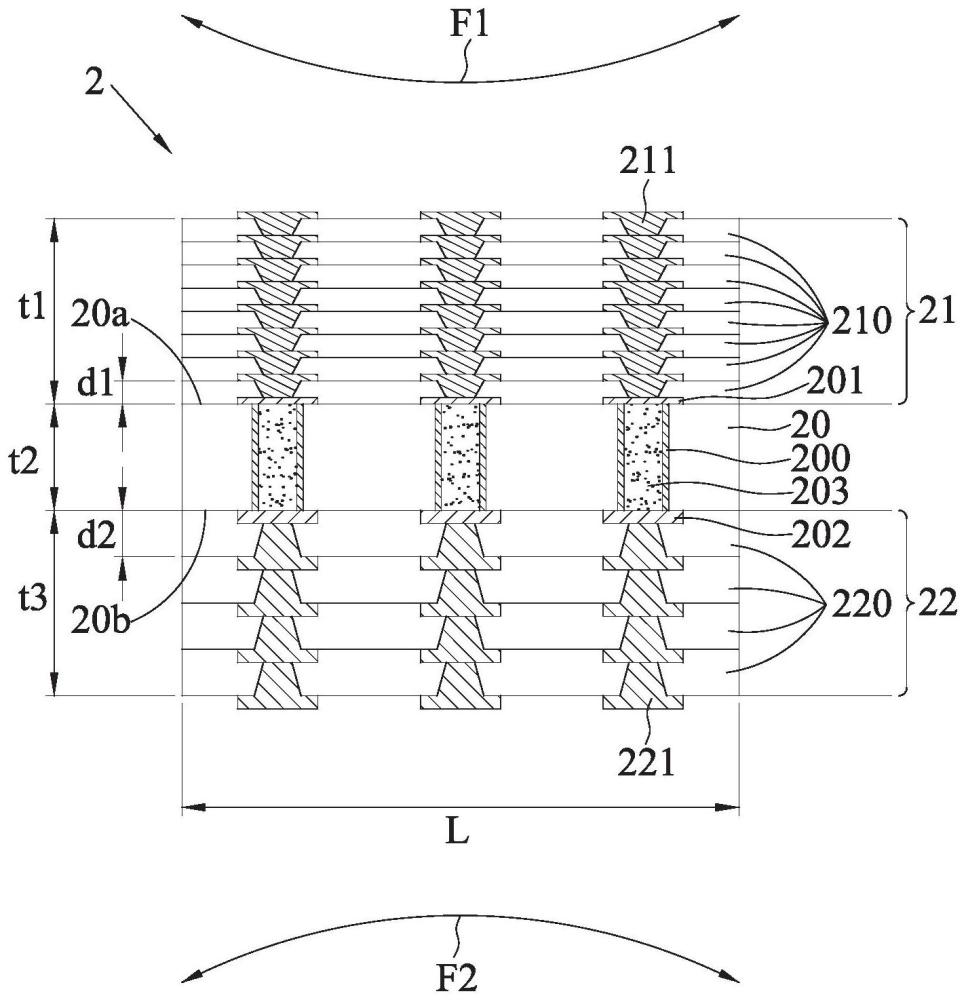

1、鉴于上述现有技术的种种缺陷,本发明提供一种封装基板,包括:核心板体,其定义有相对的第一侧及第二侧,其中,该核心基板具有连通该第一侧与第二侧的导电通孔;第一线路结构,其设于该核心板体的第一侧上,且该第一线路结构包含至少一第一介电层及结合该第一介电层且电性连接该导电通孔的第一线路层;以及第二线路结构,其设于该核心基板的第二侧上,且该第二线路结构包含至少一第二介电层及结合该第二介电层且电性连接该导电通孔的第二线路层,其中,该第一线路结构的布线层数不同于该第二线路结构的布线层数,以令该封装基板基于布线层数呈非对称式,且该封装基板的配置满足下列目标公式:

2、

3、其中,l=该封装基板的长度;t-t0=加工温度;

4、a1=该第一介电层的cte;a2=该核心板体的cte;

5、a3=该第二介电层的cte;

6、t1=t1+t2;m1=e1/e2;p1=t1/t2;

7、t2=t3+t2;m2=e3/e2;p2=t3/t2;

8、t1=该第一介电层的整体厚度;t2=该核心板体的板厚;

9、t3=该第二介电层的整体厚度;

10、e1=该第一线路结构的杨氏模数;e2=该核心板体的杨氏模数;

11、及

12、e3=该第二线路结构的杨氏模数。

13、前述的封装基板中,该核心板体于其第一侧及第二侧上布设有第一内线路层与第二内线路层,以令该导电通孔电性连接该第一内线路层与第二内线路层。

14、前述的封装基板中,该第一线路结构的布线层数大于该第二线路结构的布线层数。例如,该第二介电层的热膨胀系数大于或等于该第一介电层的热膨胀系数。或者,该第二介电层的单层厚度大于或等于该第一介电层的单层厚度。

15、前述的封装基板中,形成该第一介电层的材质为味之素增层膜(abf)、预浸材或bt(bismaleimide triazine)材。

16、前述的封装基板中,形成该第二介电层的材质为味之素增层膜(abf)、预浸材或bt(bismaleimide triazine)材。

17、前述的封装基板中,该第一介电层与第二介电层的材质相同。

18、前述的封装基板中,该第一介电层与第二介电层的材质相异。

19、前述的封装基板中,该目标公式依据提氏(timoshenko)弯曲公式作为演算基础。

20、由上可知,本发明的封装基板主要通过该目标公式配置第一线路结构与第二线路结构,以设计出不会翘曲的非对称式封装基板,故相较于现有技术,本发明的封装基板不仅易于安装侧的线路结构的配线(layout),且可减少安装侧的线路结构的制作成本,以降低该封装基板的制作成本。

技术特征:

1.一种封装基板,包括:

2.如权利要求1所述的封装基板,其中,该核心板体于其第一侧及第二侧上布设有第一内线路层与第二内线路层,以令该导电通孔电性连接该第一内线路层与第二内线路层。

3.如权利要求1所述的封装基板,其中,该第一线路结构的布线层数大于该第二线路结构的布线层数。

4.如权利要求3所述的封装基板,其中,该第二介电层的热膨胀系数大于或等于该第一介电层的热膨胀系数。

5.如权利要求3所述的封装基板,其中,该第二介电层的单层厚度大于或等于该第一介电层的单层厚度。

6.如权利要求1所述的封装基板,其中,形成该第一介电层的材质为味之素增层膜、预浸材或bt材。

7.如权利要求1所述的封装基板,其中,形成该第二介电层的材质为味之素增层膜、预浸材或bt材。

8.如权利要求1所述的封装基板,其中,该第一介电层与第二介电层的材质相同。

9.如权利要求1所述的封装基板,其中,该第一介电层与第二介电层的材质相异。

10.如权利要求1所述的封装基板,其中,该目标公式依据提氏弯曲公式作为演算基础。

技术总结

一种封装基板,包括一核心板体及设于该核心板体相对两侧的第一线路结构及第二线路结构,以令该第二线路结构的布线层数与该第一线路结构的布线层数不相同,使该封装基板呈非对称式,并依据该第一线路结构的第一介电层与该第二线路结构的第二介电层的厚度及CTE设计该第一线路结构与第二线路结构,以避免该封装基板发生翘曲的问题。

技术研发人员:张垂弘,陈敏尧,林松焜

受保护的技术使用者:芯爱科技(南京)有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!